指令级并行:处理器并行执行多条指令,同时呈现出简单顺序执行的表象。

延迟界限(latency bound, 一系列操作要求严格顺序执行导致)和吞吐量界限(throughput bound, 处理器计算能力 并发数量限制)限制了处理器的计算能力。

超标量(superscalar):它可以在每个时钟周期执行多个操作,而且是乱序的。

乱序(out-of-order):指令执行的顺序不一定要与它们在机器级程序中的顺序一致。

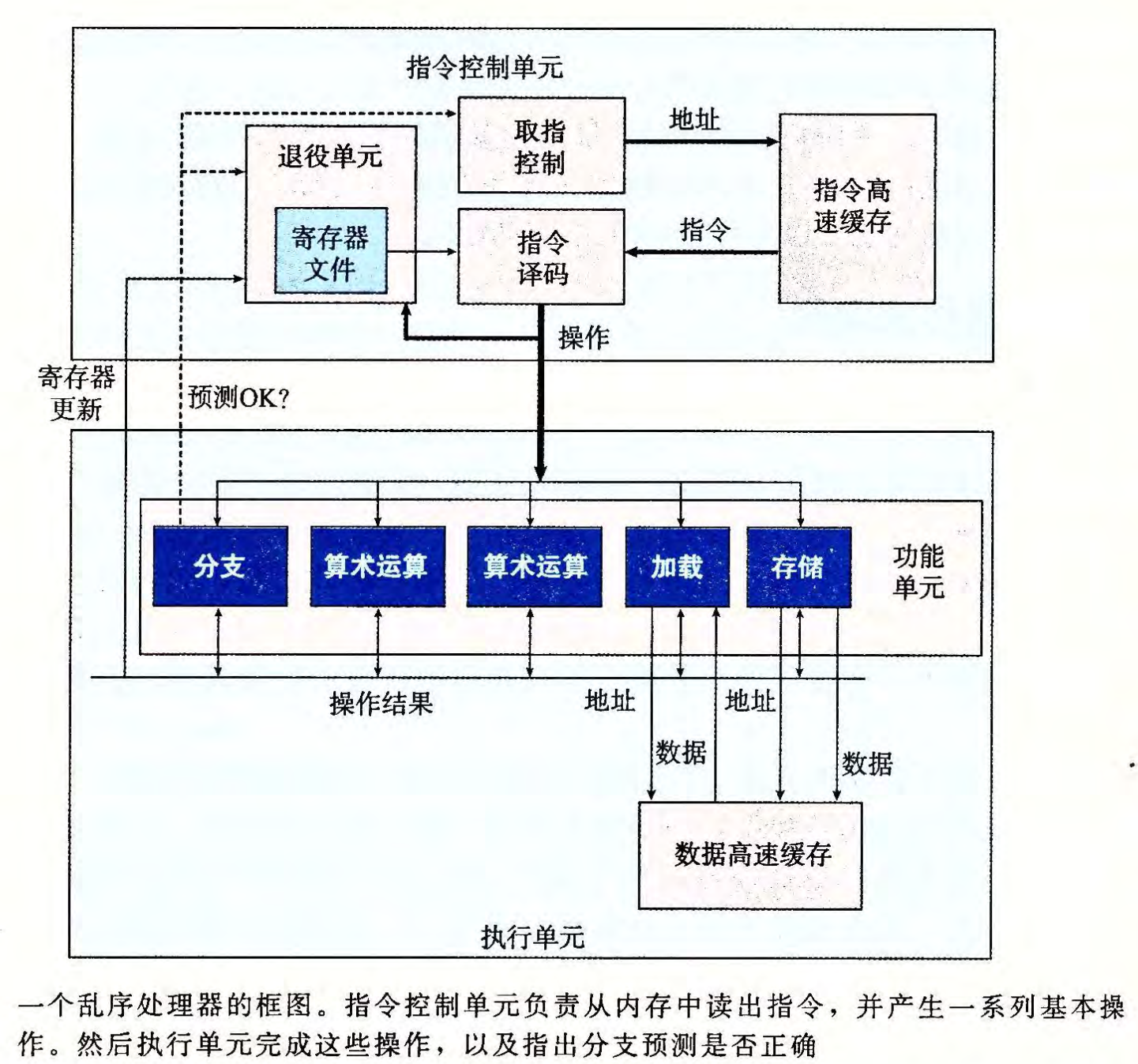

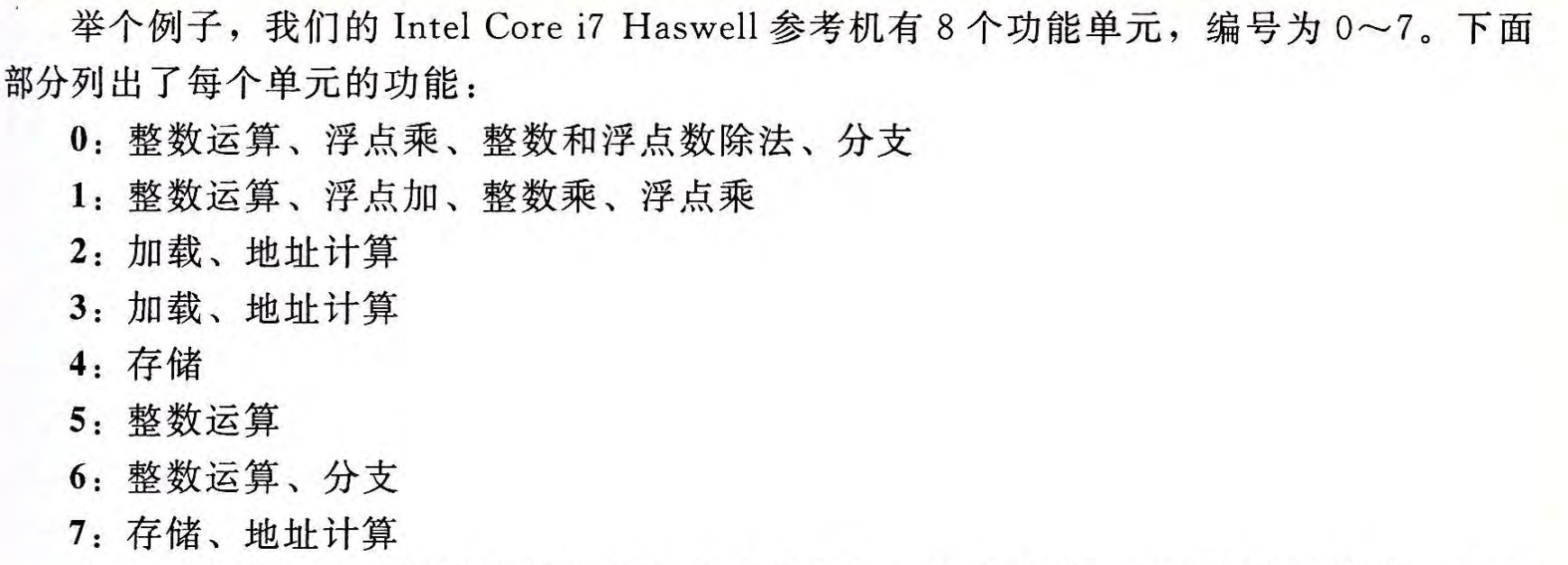

CPU有两个主要部分:指令控制单元(Instruction Control Unit, ICU)和执行单元(Execution Unit, EU)。前者负责从内存中读出指令序列,并根据其生成一组针对程序数据的基本操作,后者负责执行这些操作。

ICU从instruction cache中提前读取指令,以保证有足够时间对指令译码,并把操作发送到EU。

对于程序出现两个可能的前进方向,处理器采用分支预测(branch prediction)技术预测是否选择分支,以及分支的目标地址。使用投机执行(speculative execution)技术,处理器会在它确定分支预测是否正确之前就执行分支预测会跳到的地方的指令,并对指令译码。(提前译码,随后判断)

处理器通过流水线(Pipeline)技术实现了并行执行多条指令的效果,同时还可以呈现出简单顺序执行的表象。具体来说,流水线将CPU指令执行过程分解成若干个阶段,并将每个阶段交给不同的硬件电路来执行。例如,在x86架构的CPU中,流水线包含了取指、译码、执行、访存、写回等阶段。当一个阶段完成后,数据将被传递到下一个阶段进行处理,这样就可以让不同的指令在不同的阶段之间针对不同的操作进行并行处理。

同时,为了实现简单顺序执行的表象,CPU流水线还使用了一些技术,例如控制相关性、数据相关性和结构相关性等。这些技术可以确保指令和数据在流水线上正确地流动,同时避免了指令之间的冲突和干扰,从而保证了指令执行的正确性和顺序性。因此,CPU可以通过流水线技术实现指令的并行处理,同时又能够避免指令执行顺序的混乱,提高了CPU的运行效率和执行速度。

reference:CSAPP(Computer System: A Programer Perspective)