当rom向fpga传输数据时,可以发送coe文件,规定数据进制,以及用逗号可以分开不同的数据,但是通过上位机经过usb向fpga传输数据时,就不能是简单的txt文件,要转换成纯二进制文件,才可以保证数据的准确性。

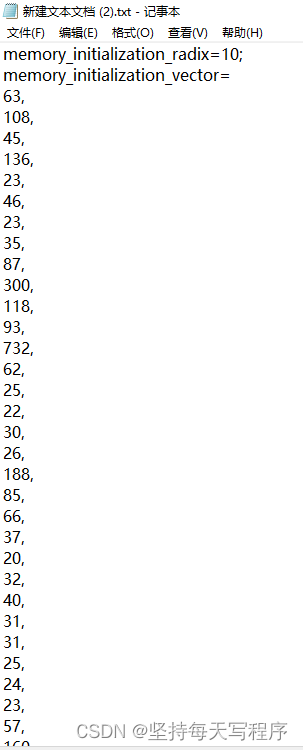

在rom实验过程中,只需要通过文本文将,写成这样的coe文件格式,就可以将相应的数据传输到fpga当中,只需要在建立romip时,设置数据位宽和数据个数(深度)就可以了。

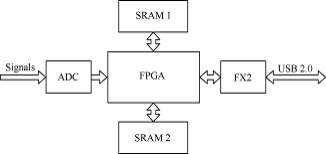

但是如果通过上位机经过usb传输时,如果传输这样的文件,就会把对应的ascii码传输给fpga,当然如果我们只是进行回环实验,然后把数据通过文件方式读取到文本文件中,就可以得到跟输入文件一样的数据了。这是因为fpga没有对数据进行处理,而fpga usb通信整个传输过程就是上位机将要发送的文件,将该符号对应的ascii码发送到fx2 usb的 模拟fifo当中(而小梅哥的开发板当中使用的fx2 usb模块,是规定为16位的数据格式),然后就传输到fpga的接收端口,当然如果fpga不做任何处理,就将该数据传输给usb的fifo当中,然后传输到上位机,并解析成对应的符号(ascii码),当然得到的数据就跟上位机发送的一样。但是,如果我们fpga要对数据进行处理,再发送,可想而知,上位机发送时,并不能识别出该进制,所以我认为应该先把数据进行严格的预处理,变成纯二进制文件,规定该数据的位数。而且,该通信过程是按照16进制传输的,所以传输纯二进制文件,就可以保证fpga收到的数据就是我们发送的数据的16进制。

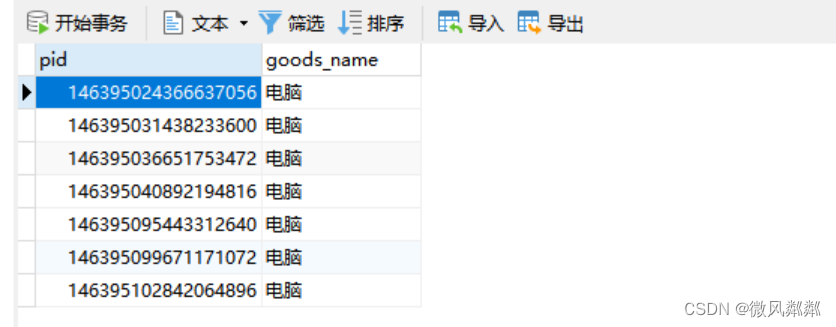

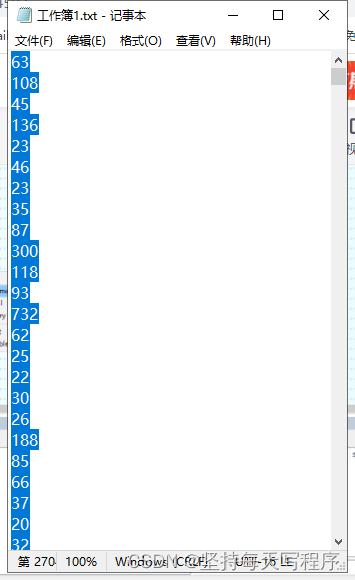

比如,我要发送如下文件,就必须把数据进行二进制格式化,把这些数据复制,因为我在rom当中设置的数据位宽是10,但是在fpga usb传输当中,规定的是16位,所以在这里我也设置为16(当然如果数据小一点,可以设置成8位,然后在接收数据时,就把高八位和低八位进行分开就好了)

测试:

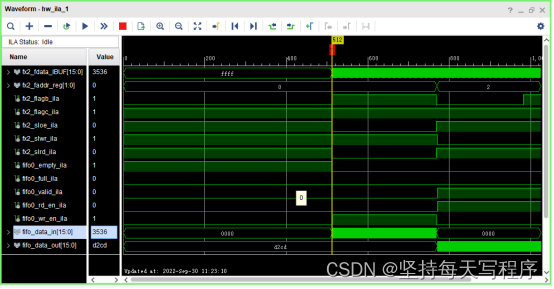

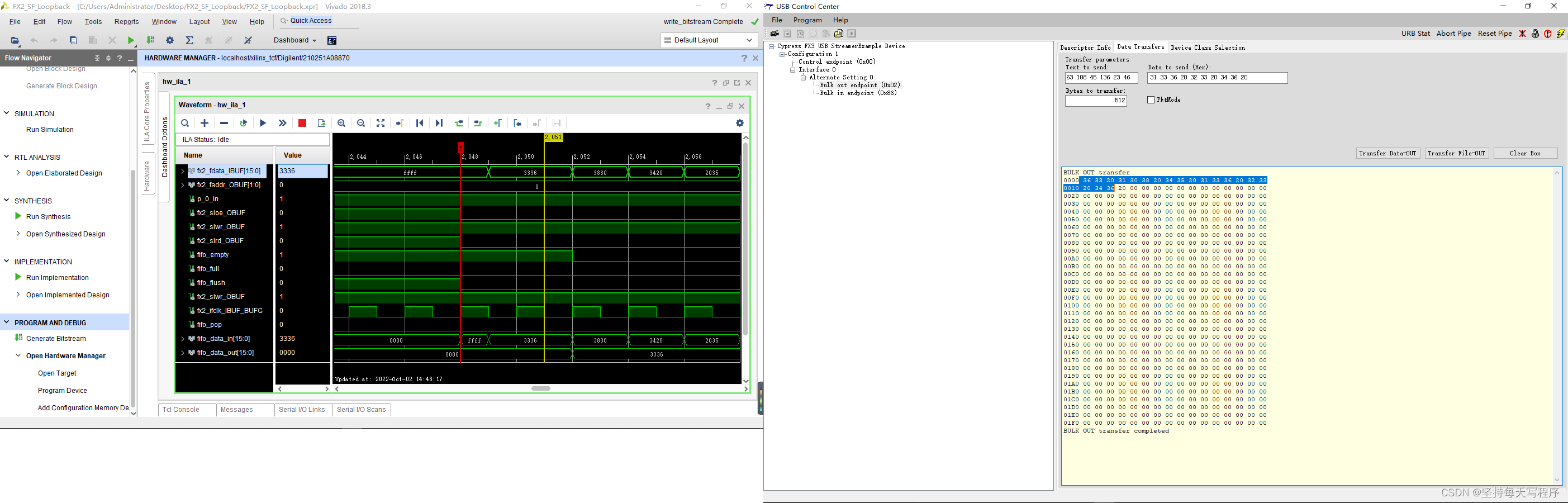

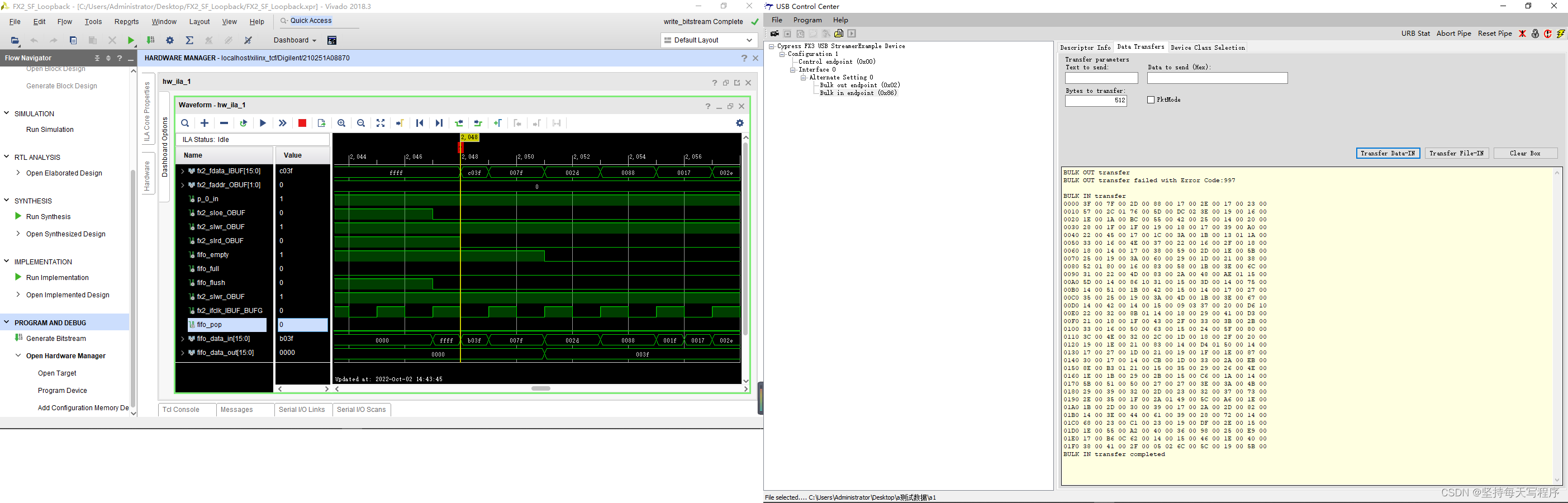

对比一下,我们直接发上面的10进制文件,fpga会收到的数据:注意看ila里面的fifo datain,这是我们fpga收到的实际数据,可以看到并不是我们想收到的63,二是6和3对应的ascii码

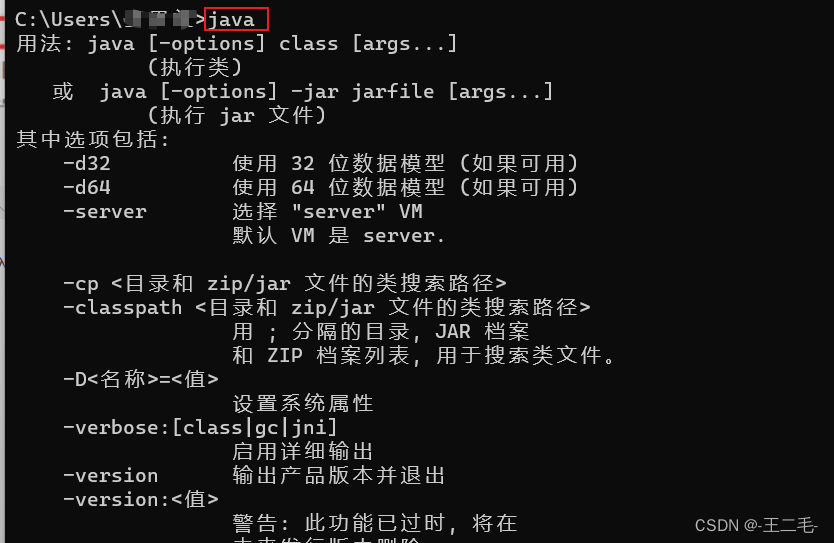

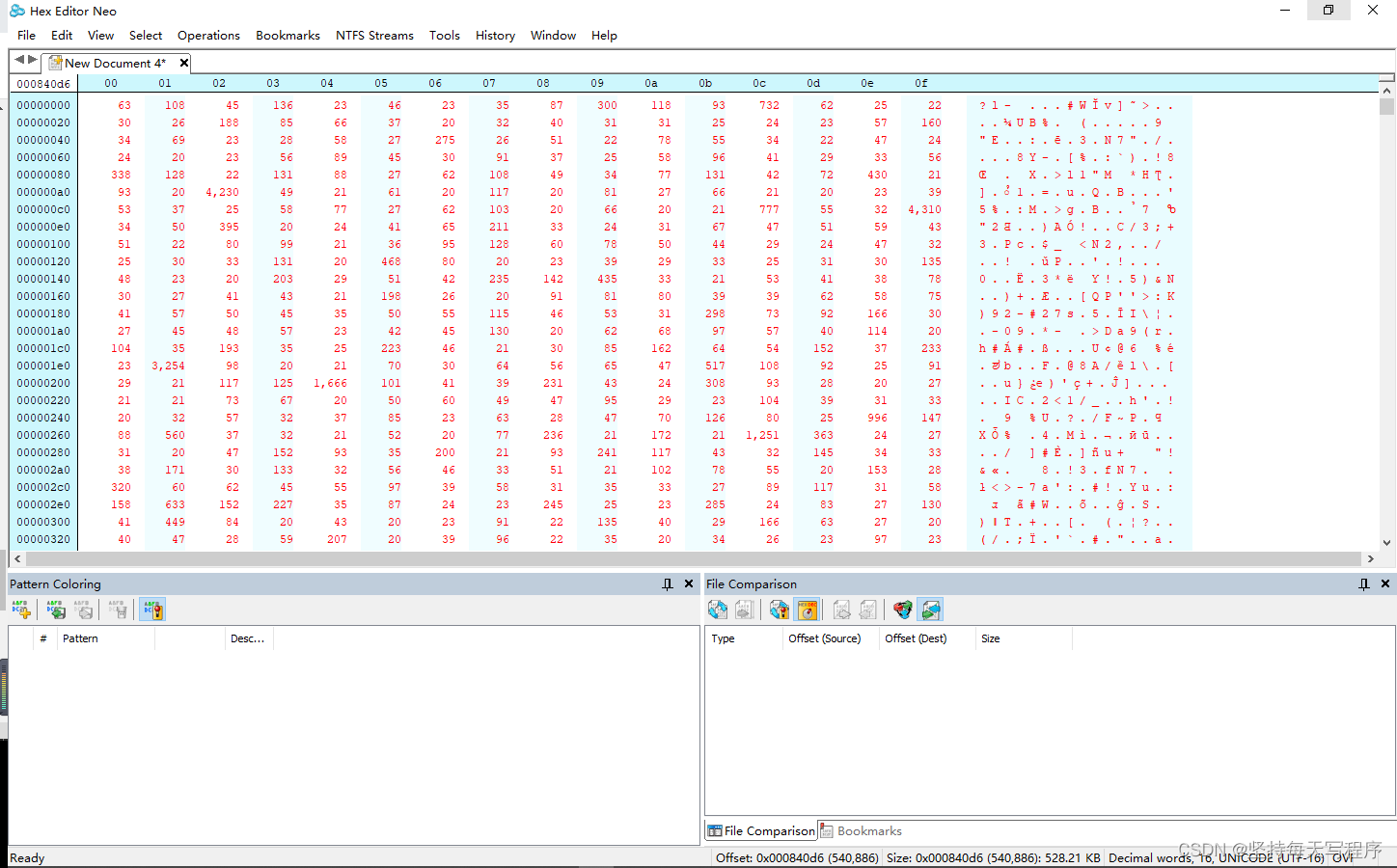

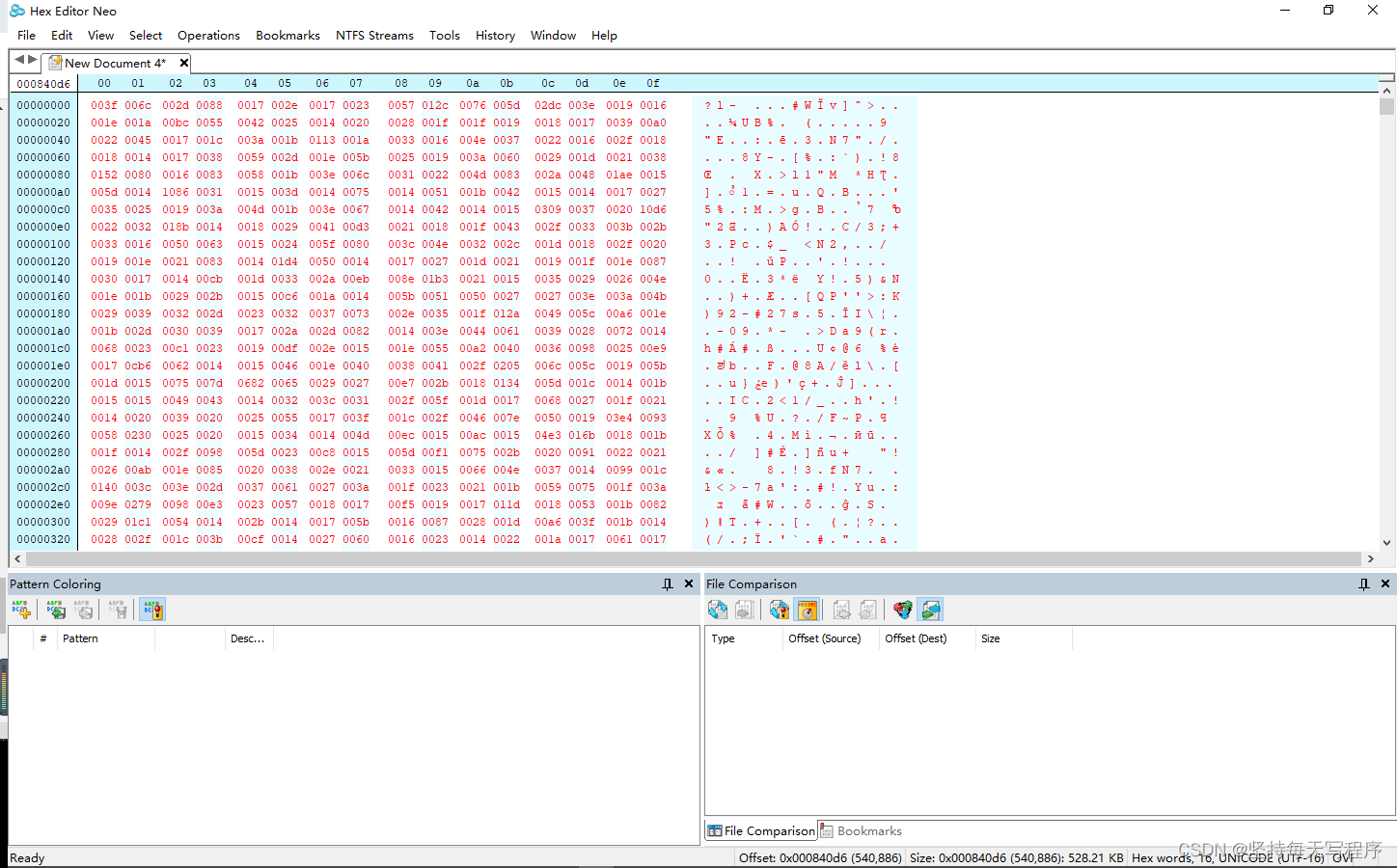

在16进制编辑器当中,将编辑器位数设置为16位,然后新建文件,将数据显示格式设置为10进制,然后把这些数据复制进去即可。

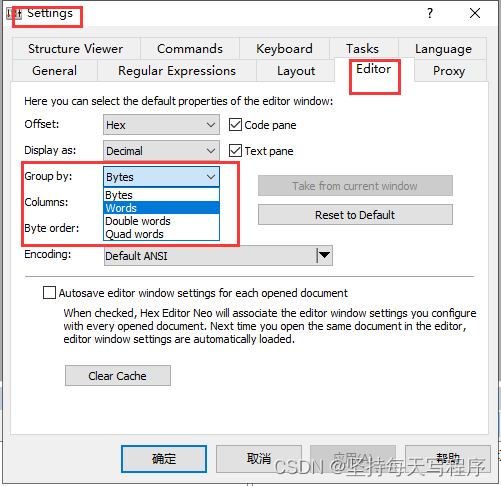

在设置当中,选择words(16位)(bytes(8位)),然后点击应用即可:

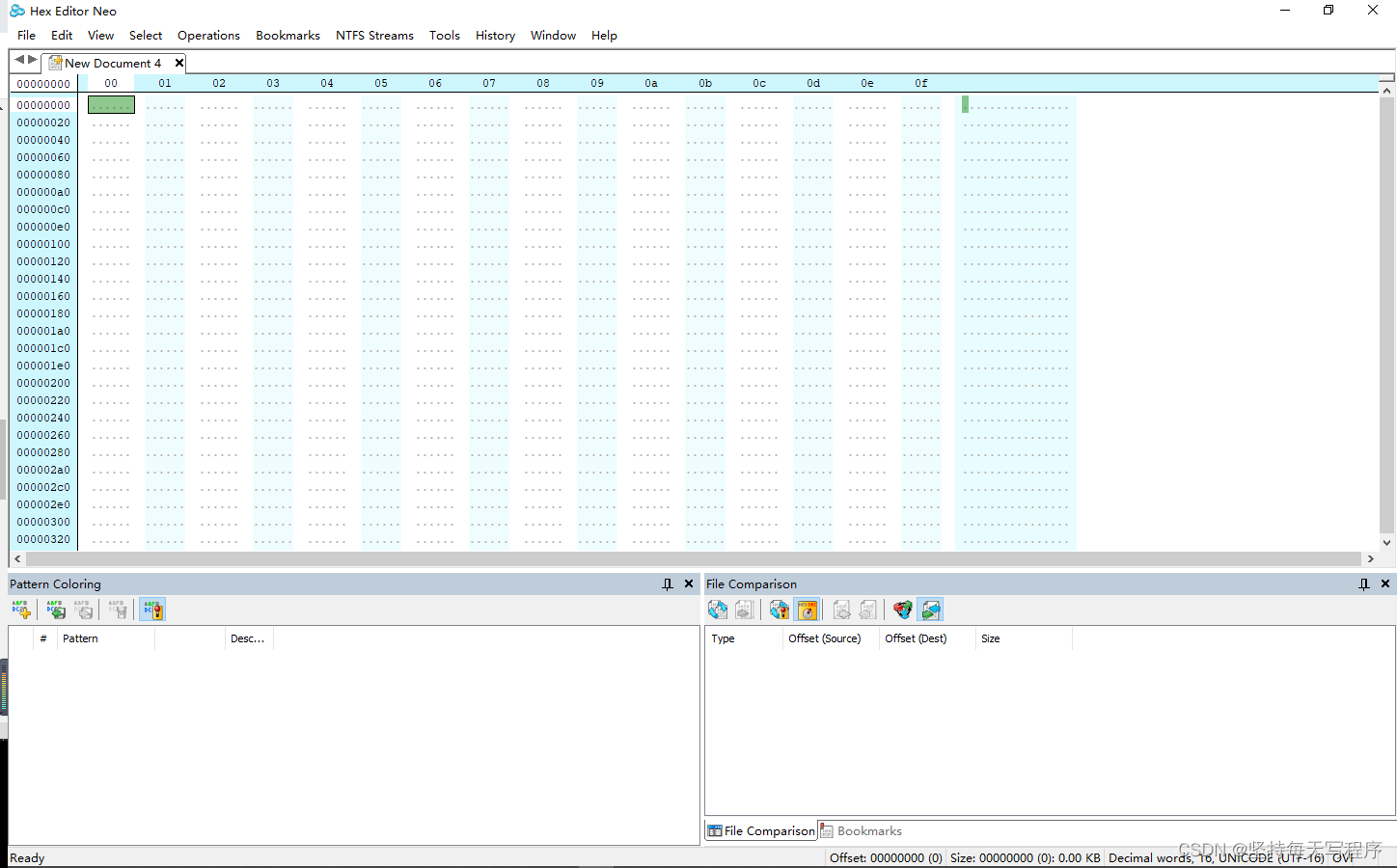

新建文件:

数据显示格式设置为10进制

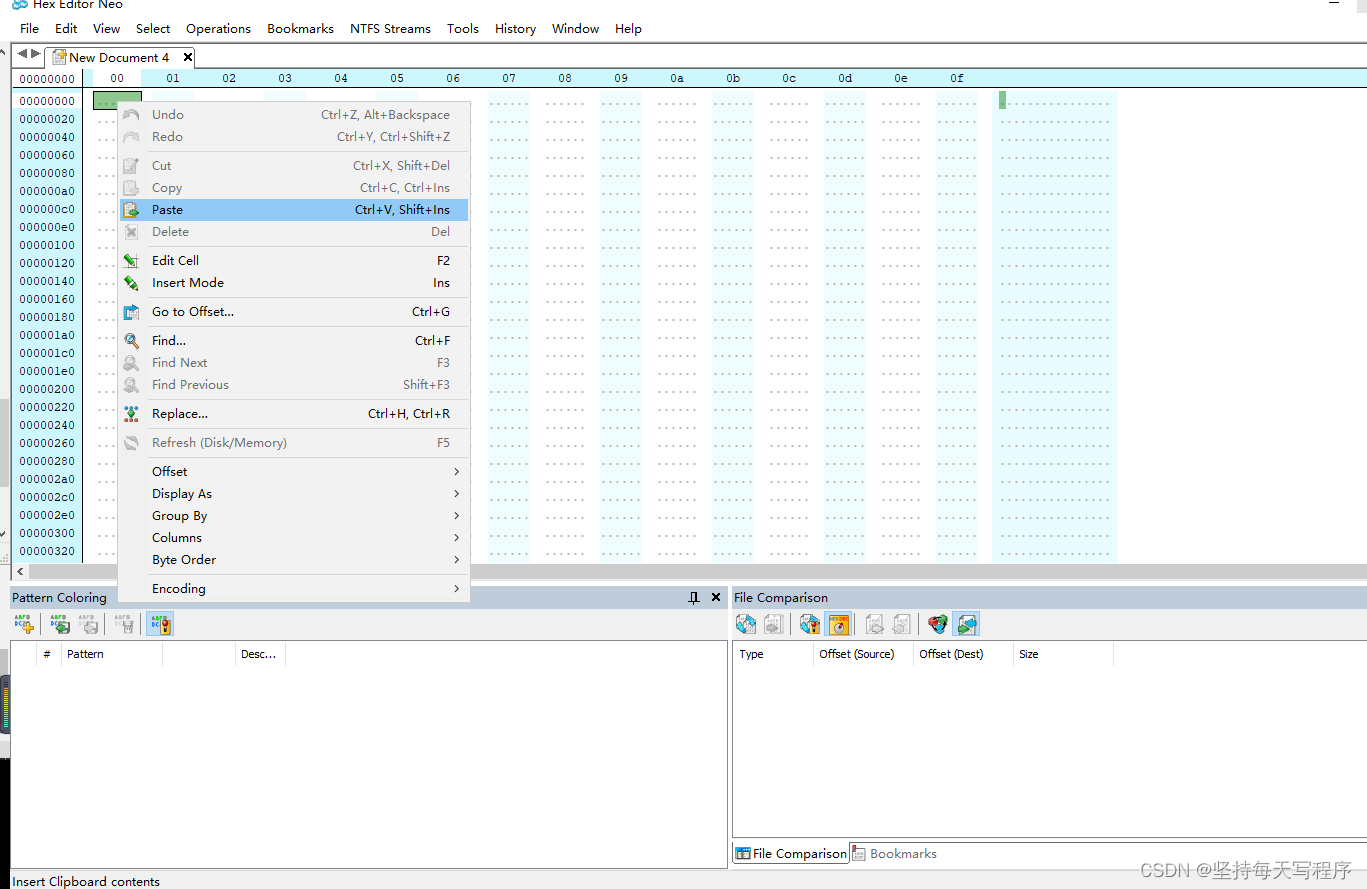

复制的时候,把鼠标放在第一位那,不要双击,直接右键复制就好,一定一定不要双击去编辑,直接右键复制

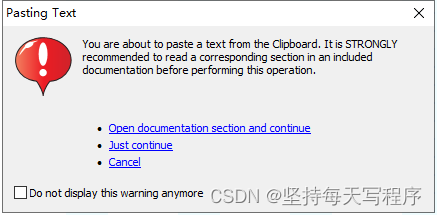

点击继续就好了

复制完成

然后改成16进制就可以看到

然后保存文件,再进行传输,就可以看到上位机收到的和fpga当中的数据是一致的

对于hex editor neo这个软件,我是直接在电脑管家里面下载的,看了一下网上的教程比较少,就自己摸索了一下,还有很多功能不太清楚。

对于这部分,是因为我想要通过把大量输入数据传输到fpga,然后运算出来,再通过上位机去读取,会比较方便,所以要对数据进行预处理而发现的一些方法,希望大家批评指正。

同时,也在小破站录了一个视频,需要的朋友可以看一下:xilinx FPGA FX2 usb通信模块之上位机发送的数据格式_哔哩哔哩_bilibili