随笔记录

目录

1. 背景介绍

2. 查看时序

2.1 Vivado tcl 模式编译固件,查看时序报告

2.1.1 时序报告路径

2.1.2 查看时序报告内容

2.2 Vivado GUI 模式编译固件,查看时序

1. 背景介绍

硬件源码,需要编译固件生成 bit/bin 文件后,检查时序

2. 查看时序

2.1 Vivado tcl 模式编译固件,查看时序报告

2.1.1 时序报告路径

# 查看时序报告所在路径,即编译生成的 bin/bit 文件同级目录中[root@bogon impl_1]#

[root@bogon impl_1]# pwd

/magx/version/DDR/DDR-V1.0.8.0/ndpp_ddr_demo/firmware/x1100_prj/prj/project_1/project_1.runs/impl_1

[root@bogon impl_1]#

[root@bogon impl_1]#[root@bogon impl_1]#

[root@bogon impl_1]# ll

total 281700

-rw-r--r--. 1 root root 12917 Aug 25 00:35 gen_run.xml

-rw-r--r--. 1 root root 394 Aug 25 00:17 htr.txt

-rw-r--r--. 1 root root 27412 Aug 25 00:22 init_design.pb

-rwxr-xr-x. 1 root root 8376 Aug 25 00:17 ISEWrap.js

-rwxr-xr-x. 1 root root 2110 Aug 25 00:17 ISEWrap.sh

-rw-r--r--. 1 root root 80373 Aug 25 00:26 opt_design.pb

-rw-r--r--. 1 root root 11709 Aug 25 00:31 phys_opt_design.pb

-rw-r--r--. 1 root root 565510 Aug 25 00:31 place_design.pb

-rw-r--r--. 1 root root 6947 Aug 25 00:17 project.wdf

-rw-r--r--. 1 root root 30051 Aug 25 00:35 route_design.pb

-rw-r--r--. 1 root root 1422 Aug 25 00:17 rundef.js

-rw-r--r--. 1 root root 257 Aug 25 00:17 runme.bat

-rw-r--r--. 1 root root 109747 Aug 25 00:35 runme.log

-rwxr--r--. 1 root root 1003 Aug 25 00:17 runme.sh

-rw-r--r--. 1 root root 991 Aug 25 00:21 vivado.jou

-rw-r--r--. 1 root root 149 Aug 25 00:36 vivado.pb

-rw-r--r--. 1 root root 36 Aug 25 00:35 yusur_ndpp_x1100_bus_skew_routed.pb

-rw-r--r--. 1 root root 367733 Aug 25 00:35 yusur_ndpp_x1100_bus_skew_routed.rpt

-rw-r--r--. 1 root root 649950 Aug 25 00:35 yusur_ndpp_x1100_bus_skew_routed.rpx

-rw-r--r--. 1 root root 386929 Aug 25 00:35 yusur_ndpp_x1100_clock_utilization_routed.rpt

-rw-r--r--. 1 root root 3507458 Aug 25 00:31 yusur_ndpp_x1100_control_sets_placed.rpt

-rw-r--r--. 1 root root 37 Aug 25 00:26 yusur_ndpp_x1100_drc_opted.pb

-rw-r--r--. 1 root root 46039 Aug 25 00:26 yusur_ndpp_x1100_drc_opted.rpt

-rw-r--r--. 1 root root 85986 Aug 25 00:26 yusur_ndpp_x1100_drc_opted.rpx

-rw-r--r--. 1 root root 76 Aug 25 00:35 yusur_ndpp_x1100_drc_routed.pb

-rw-r--r--. 1 root root 56560 Aug 25 00:35 yusur_ndpp_x1100_drc_routed.rpt

-rw-r--r--. 1 root root 111880 Aug 25 00:35 yusur_ndpp_x1100_drc_routed.rpx

-rw-r--r--. 1 root root 542732 Aug 25 00:31 yusur_ndpp_x1100_io_placed.rpt

-rw-r--r--. 1 root root 52 Aug 25 00:35 yusur_ndpp_x1100_methodology_drc_routed.pb

-rw-r--r--. 1 root root 74192 Aug 25 00:35 yusur_ndpp_x1100_methodology_drc_routed.rpt

-rw-r--r--. 1 root root 241246 Aug 25 00:35 yusur_ndpp_x1100_methodology_drc_routed.rpx

-rw-r--r--. 1 root root 40421954 Aug 25 00:25 yusur_ndpp_x1100_opt.dcp

-rw-r--r--. 1 root root 55952821 Aug 25 00:31 yusur_ndpp_x1100_physopt.dcp

-rw-r--r--. 1 root root 55928105 Aug 25 00:31 yusur_ndpp_x1100_placed.dcp

-rw-r--r--. 1 root root 71619 Aug 25 00:35 yusur_ndpp_x1100_power_routed.rpt

-rw-r--r--. 1 root root 16429197 Aug 25 00:35 yusur_ndpp_x1100_power_routed.rpx

-rw-r--r--. 1 root root 723 Aug 25 00:35 yusur_ndpp_x1100_power_summary_routed.pb

-rw-r--r--. 1 root root 67754154 Aug 25 00:35 yusur_ndpp_x1100_routed.dcp

-rw-r--r--. 1 root root 45 Aug 25 00:35 yusur_ndpp_x1100_route_status.pb

-rw-r--r--. 1 root root 651 Aug 25 00:35 yusur_ndpp_x1100_route_status.rpt

-rw-r--r--. 1 root root 13475 Aug 25 00:17 yusur_ndpp_x1100.tcl

-rw-r--r--. 1 root root 112 Aug 25 00:35 yusur_ndpp_x1100_timing_summary_routed.pb# 时序报告:yusur_ndpp_x1100_timing_summary_routed.rpt

-rw-r--r--. 1 root root 22239996 Aug 25 00:35 yusur_ndpp_x1100_timing_summary_routed.rpt

-rw-r--r--. 1 root root 22473307 Aug 25 00:35 yusur_ndpp_x1100_timing_summary_routed.rpx

-rw-r--r--. 1 root root 300 Aug 25 00:31 yusur_ndpp_x1100_utilization_placed.pb

-rw-r--r--. 1 root root 16105 Aug 25 00:31 yusur_ndpp_x1100_utilization_placed.rpt

-rw-r--r--. 1 root root 110334 Aug 25 00:35 yusur_ndpp_x1100.vdi

[root@bogon impl_1]#2.1.2 查看时序报告内容

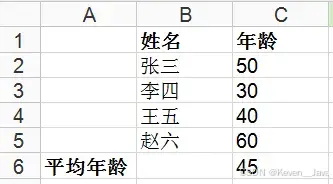

检查点:时序报告中 4个值必须全部为非负值。

- WNS(ns)

- TNS(ns)

- WHS(ns)

- THS(ns)

# 检查时序报告中 4个值必须全部为非负值。WNS(ns)

TNS(ns)

WHS(ns)

THS(ns)[root@bogon impl_1]#

[root@bogon impl_1]#

[root@bogon impl_1]# cat yusur_ndpp_x1100_timing_summary_routed.rpt|more

Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

-----

| Tool Version : Vivado v.2022.2 (lin64) Build 3671981 Fri Oct 14 04:59:54 MDT 2022

| Date : Sun Aug 25 00:35:47 2024

| Host : localhost running 64-bit CentOS Stream release 8

| Command : report_timing_summary -max_paths 10 -report_unconstrained -file yusur_ndpp_x1100_timing_summary_routed.rpt -pb yusur_ndpp_x1100_timing_summary_routed.pb -rpx yusur_ndpp_x1100_timing_summary_routed.rpx -warn_on_viola

tion

| Design : yusur_ndpp_x1100

| Device : xcku15p_CIV-ffve1517

| Speed File : -2 PRODUCTION 1.29 05-01-2022

| Temperature Grade : E

---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

-----Timing Summary Report------------------------------------------------------------------------------------------------

| Timer Settings

| --------------

------------------------------------------------------------------------------------------------Enable Multi Corner Analysis : YesEnable Pessimism Removal : YesPessimism Removal Resolution : Nearest Common NodeEnable Input Delay Default Clock : NoEnable Preset / Clear Arcs : NoDisable Flight Delays : NoIgnore I/O Paths : NoTiming Early Launch at Borrowing Latches : NoBorrow Time for Max Delay Exceptions : YesMerge Timing Exceptions : YesCorner Analyze AnalyzeName Max Paths Min Paths------ --------- ---------Slow Yes YesFast Yes Yes------------------------------------------------------------------------------------------------

| Report Methodology

| ------------------

------------------------------------------------------------------------------------------------Rule Severity Description Violations

--------- -------- ---------------------------------------- ----------

HPDR-1 Warning Port pin direction inconsistency 12

LUTAR-1 Warning LUT drives async reset alert 33

TIMING-9 Warning Unknown CDC Logic 1

TIMING-10 Warning Missing property on synchronizer 1

XDCH-2 Warning Same min and max delay values on IO port 1Note: This report is based on the most recent report_methodology run and may not be up-to-date. Run report_methodology on the current design for the latest report.check_timing reportTable of Contents

-----------------

1. checking no_clock (0)

2. checking constant_clock (0)

3. checking pulse_width_clock (0)

4. checking unconstrained_internal_endpoints (0)

5. checking no_input_delay (12)......

......

......

......12. checking latch_loops (0)

----------------------------There are 0 combinational latch loops in the design through latch input------------------------------------------------------------------------------------------------

| Design Timing Summary

| ---------------------

------------------------------------------------------------------------------------------------WNS(ns) TNS(ns) TNS Failing Endpoints TNS Total Endpoints WHS(ns) THS(ns) THS Failing Endpoints THS Total Endpoints WPWS(ns) TPWS(ns) TPWS Failing Endpoints TPWS Total Endpoints------- ------- --------------------- ------------------- ------- ------- --------------------- ------------------- -------- -------- ---------------------- --------------------0.097 0.000 0 179559 0.010 0.000 0 178757 0.000 0.000 0 92490All user specified timing constraints are met.------------------------------------------------------------------------------------------------

| Clock Summary

| -------------

------------------------------------------------------------------------------------------------ClockWaveform(n

s) Period(ns) Frequency(MHz)

---------------

-- ---------- --------------

c0_sys_clk_p{0.000 4.9

98} 9.996 100.040mmcm_clkout0{0.000 1.6

66} 3.332 300.120pll_clk[0]66} 3.332 300.120

以上截图 WNS(ns) TNS(ns) 负值,时序异常,需要定位原因。

2.2 Vivado GUI 模式编译固件,查看时序

可以直接查看Vivado 图形界面查看即可。

到此Vivado 编译固件,时序检查已完成。