从最开始进行分析,一步一步扩展与改进,直到今天的高速信息处理时代

最难的是,该处理器时间太早,很多资料和功能信息都很难查找

4004芯片:

4004历史

Intel-4004已经很难买到了,可以说是“老古董”。

Intel 4004微处理器最初是Intel专门为日本一家名为Busicom的公司设计制造,用于该公司的计算器产品。

Intel还曾开发出4001(动态内存DRAM)、4002(只读存储器ROM)、4003(Register),用4004芯片,配上4001(40字节的动态内存DRAM)、4002(256字节的只读存储器ROM)、4003(10位的移位寄存器芯片Register),再加上键盘和数码管,就构成了一台完整的微型计算机MCS-4。

4004是美国英特尔公司 (Intel) 第一款推出的微处理器,也是全球第一款商用微处理器。

4004处理器于1971年推出,尺寸为3mm×4mm,外层有16只针脚,内里有2,250个晶体管,它采用10微米制程。

4004的最高频率有740kHz,能执行4位运算,支持8位指令集及12位地址集。

4004基本信息

位数/频率:4bit/6万次

频率/前端总线:108KHZ/0.74MHz (4bit)

封装/针脚数量:陶瓷DIP,塑封DIP / 16针

核心技术/晶体管数量:10微米 / 2250

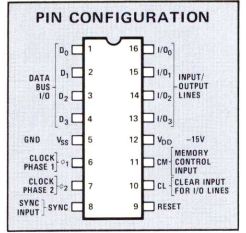

封装引脚

16脚DIP封装,有白色陶瓷+金色散热器 ( C4004 )、黑色陶瓷 ( D4004 )、黑色塑料 ( P4004 ) 等封装形式

Pin Description(管脚定义)

- 1、DATA BUS I/O(数据总线输入输出)

D0 - D3:双向总线,担任数据与地址IO - 2、CLOCK PHASE(时钟相位)

双向时钟信号输入 - 3、SYNC OUTPUT(同步输出)

同步信号输出:在一个指令周期的开始,该信号被送至ROM和RAM芯片,以确保移位寄存器正常工作(这里的ROM与RAM为MCS-4系列制芯片) - 4、MEMORY CONTROL OUTPUT(RAM控制输出)

CM-RAM0 - CM-RAM3输出:用于4002RAM芯片组的片选 - 5、MEMORY CONTROL OUTPUT(ROM控制输出)

CM-ROM输出:用于ROM芯片组的片选 - 6、TEST(测试)

测试输入:JCN指令 - 7、RESET(重置)

复位:该引脚保持高电平64个时钟周期(8个机器周期)时4004发生复位,在复位发生时,所有寄存器都被清0 - 8、Vss、Vdd

电源

内部结构

寄存器组

| 名称 | 大小(bits) | |

|---|---|---|

| – | Accumulator | 4 |

| – | Carry/Link | 1 |

| 索引寄存器 | Index Registers ( IR ) | (4+4)*8 |

| 程序寄存器 | Program Counter ( PC ) | 12 |

| 堆栈指针 | Stack Pointer ( Stack ) | 12*3 |

| 临时寄存器 | TEMP.REG | 4 |

| – | INSTRUCTION REGISTER | 8 |

指令集

(带 * 号的是双字指令,需要两个指令周期(1指令周期 = 8时钟周期))

| 基础指令 | ||||

|---|---|---|---|---|

| HEX | 助记符 | 指令字1 | 指令字2 | 功能 |

| 00 | NOP | 0000 0000 | – | 无 |

| 1 | *JCN | 0001 CCCC | AAAA AAAA | 当条件C成立,跳转到当前ROM页的A地址 |

| 2 | *FIM | 0010 RRR0 | DDDD DDDD | 取当前页D地址处的数据,送至IR的R号寄存器对内 |

| 3 | FIN | 0011 RRR0 | – | 取IR中第0寄存器对数据作为ROM页内地址,将数据送至IR寄存器的R号寄存器对内 |

| 3 | JIN | 0011 RRR1 | – | 将IR中R号寄存器对内数据作为间接跳转地址进行跳转 |

| 4 | *JUN | 0100 AAAA | AAAA AAAA | 无条件跳转至地址A |

| 5 | *JMS | 0101 AAAA | AAAA AAAA | 无条件跳转至地址A,将原地址保存在堆栈SP中 |

| 6 | INC | 0110 RRRR | – | RRRR寄存器+1 |

| 7 | *ISZ | 0111 RRRR | AAAA AAAA | RRRR寄存器+1,如果结果不为0,跳转至页内地址A |

| 8 | ADD | 1000 RRRR | – | AC=AC+RRRR+C |

| 9 | SUB | 1001 RRRR | – | AC=AC-RRRR-C |

| A | LD | 1010 RRRR | – | AC=RRRR |

| B | XCH | 1011 RRRR | – | AC与RRRR交换 |

| C | BBL | 1100 DDDD | – | 借助堆栈地址返回,AC=DDDD |

| D | LDM | 1101 DDDD | – | AC=DDDD |

| F0 | CLB | 1111 0000 | – | AC=0,C=0 |

| F1 | CLC | 1111 0001 | – | C=0 |

| F2 | IAC | 1111 0010 | – | AC=AC+1 |

| F3 | CMC | 1111 0011 | – | C=~C |

| F4 | CMA | 1111 0100 | – | AC=~AC |

| F5 | RAL | 1111 0101 | – | {C,AC}向左循环平移一位 |

| F6 | RAR | 1111 0110 | – | {C,AC}向右循环平移一位 |

| F7 | TCC | 1111 0111 | – | AC=C, C=0 |

| F8 | DAC | 1111 1000 | – | AC=AC-1 |

| F9 | TCS | 1111 1001 | – | 当C=0,AC=1001当C=1,AC=1010 |

| FA | STC | 1111 1010 | – | C=1 |

| FB | DAA | 1111 1011 | – | 对AC执行BCD修正 |

| FC | KBP | 1111 1100 | – | 对AC进行独热码到二进制转换若输入非法值,AC=1111 |

| FD | DCL | 1111 1101 | – | 使用AC的低3位进行转换页AC=000时选择CM0其他情况以三位分别控制 |

| I/O与RAM指令 | ||||

| 2 | SRC | 0010 RRR1 | – | 分别在指令周期的X2与X3处将R寄存器保存的页内地址送至ROM和RAM |

| E0 | WRM | 1110 0000 | – | 将AC写入选中的RAM主字符( 4位 )中 |

| E1 | WMP | 1110 0001 | – | 将AC写入选中的RAM端口中( 注:MCS-4中,RAM/ROM亦用作IO端口 ) |

| E2 | WRR | 1110 0010 | – | 将AC写入选中的ROM端口中 |

| E3 | WPM | 1110 0011 | – | 将AC写入选中的可读写程序存储器中( 搭配4008/4009/4289使用 ) |

| E4 | WR0 | 1110 0100 | – | 将AC写入选中的RAM的0号状态字符中 |

| E5 | WR1 | 1110 0101 | – | 将AC写入选中的RAM的1号状态字符中 |

| E6 | WR2 | 1110 0110 | – | 将AC写入选中的RAM的2号状态字符中 |

| E7 | WR3 | 1110 0111 | – | 将AC写入选中的RAM的3号状态字符中 |

| E8 | SBM | 1110 1000 | – | {C,AC}=AC-C-选中的RAM主字符 |

| E9 | RDM | 1110 1001 | – | 将选中的RAM主字符写入AC |

| EA | RDR | 1110 1010 | – | 将选中的ROM输入端口数据写入AC |

| EB | ADM | 1110 1011 | – | {C,AC}=AC+C+选中的RAM主字符 |

| EC | RD0 | 1110 1100 | – | 将选中的RAM的0号状态字符写入AC |

| ED | RD1 | 1110 1101 | – | 将选中的RAM的1号状态字符写入AC |

| EE | RD2 | 1110 1110 | – | 将选中的RAM的2号状态字符写入AC |

| EF | RD3 | 1110 1111 | – | 将选中的RAM的3号状态字符写入AC |

以上就是Intel公司首款商用处理器,Intel原本只是造存储器的一家小公司,因为日本Busicom公司(造计算器)的小看,从此Intel慢慢转型进入微处理器的市场,一发不可收拾成。4004是Intel历史性的标志。

MCS-4就是4004处理器+4001ROM+4002RAM+4003SR的组合,微型计算机就是多块芯片的集合,中央处理器用来负责控制和管理。

MCS-4微型计算机

历史

该MCS-4 (微型计算机集-4 )或4000系列或Busicom芯片组是一个家庭的4位被开发的微处理器芯片组英特尔。整个芯片组由四个独立芯片组成,包括4004 CPU,后者成为第一个商用微处理器。MCS-4于1971年3月完工,于6月投入生产,并于1971年11月15日投放市场。

在Federico Faggin于1970年加入英特尔之前,4004的发展相当缓慢。Federico在英特尔开发了多项设计创新,使得微处理器可以安装在一个芯片中,包括使用硅栅技术的随机逻辑芯片设计的新方法,Faggin开发了4004测试工具,芯片和逻辑设计,同时整个MCS-4系统的所有芯片布局。

当时,英特尔仅以其内存芯片而闻名。

组件

MCS-4只需4001 ROM和4004 CPU即可实现最低功能,但其设计与RAM和移位寄存器完全兼容。此外,另外两个芯片4008和4009扩展了系统,可与英特尔现有的任何内存芯片选择配合使用。

| 部分 | 描述 |

|---|---|

| 4001 | 只读存储器 |

| 4002 | 内存 |

| 4003 | 移位寄存器 |

| 4004 | MPU |

| 4008 | 地址锁存器 |

| 4009 | I/O接口 |

首席设计师

- 特德霍夫

- 费德里科法金

- Stan Mazor

- Masatoshi Shim

相关文件

-

MCS-4 数据表

链接:https://pan.baidu.com/s/15zO7lQ7urFh9zOpKaOIYAw

提取码:9a96 -

MCS-4 手册

链接:https://pan.baidu.com/s/12Qww3WBZ-jMgBEAfWMvnvg

提取码:utdl

框架

这就是MCS-4组成的核心部分,应该大致能理解该微型计算机的框架,接下来将分析其运作和功能

MCS-4的组成结构与功能分析

英特尔微处理器快速参考指南:https://www.intel.com/pressroom/kits/quickreffam.htm#i486

简介:

MCS-4是一套微型可编程计算机,适用于测试系统、外围设备、终端、计费机、测量系统、数字和过程控制等应用。

4004 CPU、4003 SR和4002 RAM是标准构建块。4001 ROM包含自定义微程序,使用符合客户规格的金属掩模实现。

MCS-4系统易于与开关、键盘、显示器、电传打字机、打印机、阅读器、A-D转换器和其他流行的外围设备进行接口。

使用MCS-4微型计算机集构建的系统最多可以有4K x 8位ROM字、1280 x 4位RAM和128根 I/O线,而不需要任何接口逻辑。通过添加一些简单的门,MCS-4可以在任何组合中拥有48个RAM和ROM包,以及192个 I/O行。最小系统配置由一个CPU和一个256 x 8位ROM组成。

MCS-4有一个非常强大的指令集,允许二进制和十进制算术。它包括条件分支、跳转到子例程,并通过间接获取提供了对ROM查找表的有效使用。

英特尔MCS-4微型计算机(4001/2/3/4)采用硅栅技术制造。这种低阈值技术允许设计和生产性能更高的MOS电路,并在单片芯片上提供比传统MOS技术更高的功能密度。

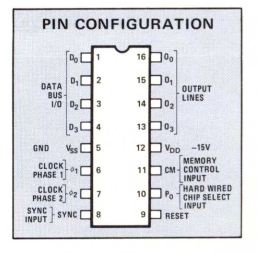

4001(ROM)

256x8位掩模可编程ROM和4位I/O端口

4001是一个2048位的金属掩模可编程ROM,为MCS-4微型计算机提供定制的微程序显示功能。

地址和数据通过时间复用在4条数据总线上传输。计时是使用两个时钟信号和4004提供的同步信号内部生成的。地址在同步之后的三个时间段从CPU接收,并在256个字中选择一个,在16个ROM中选择一个。为此,每个ROM被metal选项标识为#0、1、2到15。还提供了一个命令行(CM),它的作用域是选择一个ROM库(由16个ROM组成的组)。在寻址时间之后的两个时间段(m1&m2)内,信息从ROM传输到数据总线线路。

ROM的第二种操作模式是作为输入/输出控制设备。在这种模式下,ROM芯片将把信息路由到4 I/O外部线路的数据总线线路和数据总线线路之间。每个芯片都有能力识别自己的 I/O端口操作,识别 I/O端口指令,并决定它是输入还是输出操作和执行指令。在正常工作时,外部信号(CL)会自动清除输出寄存器。

当复位线低(负电压)时,所有内部触发器(包括输出寄存器)将被重新设置。

4002(RAM)

320位RAM和4位输出端口

4002执行两个函数。作为RAM,它将320位存储在4个寄存器中,每个寄存器包含24个4位字符(16个主存字符和4个状态字符)。作为与周边设备通信的载体,它具有4条输出线路和相应的控制逻辑来执行输出。

4003(SR)

10位串行进/并行串行出移位寄存器(SR)

4003是一个10位静态移位寄存器,具有串行输入、并行和串行输出数据,其功能是增加输出行数,与键盘、显示器、打印机、电传打字机、开关、读卡器、A-D转换器等 I/O设备进行接口。

数据是串行加载的,并在通过逻辑访问在10个输出行上并行可用。当启用(E = low)时,将读取移位寄存器内容;当未启用(E = high)时,平行线位于Vss。串行输出行不受使能逻辑的影响。

数据也可以串行地允许不确定数量的类似设备级联在一起,以提供移位寄存器长度乘以10的倍数。

数据传输由CP信号控制。内部电源接通清除电路将清除移位寄存器(Qi = Vss)之间的应用电源电压和第一个CP信号。

4004(CPU)

4004是一个中央处理器单元(CPU),设计用于与MCS-4(4001, 4002, 4003)的其他成员一起为微程序mable计算机应用程序工作。

CPU芯片由4位加法器、64位(16×4)索引寄存器、48位(4×12)程序计数器和堆栈(如果可能的话,嵌套最多3层)、地址增量器、8位指令寄存器和译码器以及控制逻辑。信息在4004和其他芯片之间通过4线数据总线流动。一个4004可以与多达48个ROM 4001和RAM(4002)芯片组合使用。

典型的机器周期从CPU向ROM和RAM发送同步计时信号(SYNC)开始。接下来,使用三个时钟周期将12位ROM地址发送到数据总线。然后将地址递增1并存储在程序计数器中。所选ROM在接下来的2个时钟周期内发送回8位指令或数据。该信息存储在两个寄存器中:OPR和OPA。接下来的三个时钟周期用于执行指令。

ROM存储空间由命令ROM控制信号(CM-ROM)控制,多达4个RAM存储空间由4个命令RAM控制信号(CM RAM0、CM RAM1、CM RAM2、CM RAM3)控制。完整的存储转换是由执行DCL指令完成的。

输入测试信号(TEST)与条件跳转(JCN)指令一起使用。外部复位信号用于清除所有寄存器和触发器。为了完全清除所有寄存器,复位信号必须应用于至少8个内存周期(8 x 8个时钟周期)。重置后,程序将从 “0” 步骤开始,并选择CM-RAM0。

执行指令周期

详细的功能规范描述了系统的操作、指令集、每条指令的CPU活动以及一些编程和硬件示例,这些详细的功能规范是单独发布的,可根据要求提供。

下面是系统运行的简要概述MCS-4使用10.8 usec指令周期。CPU(4004)生成同步信号(SYNC),指示指令周期的开始,并将其发送到ROM(4001)和RAM(4002)。

基本指令执行需要8或16个周期的750千赫时钟。在一个典型的序列中,CPU在前三个周期(A1, A2, A3)向ROM发送12位地址。所选ROM芯片在接下来的两个周期(M1. M2)中向CPU发送8位指令(OPR, OPA),然后在最后三个周期(X1. X2. X3)中对指令进行解释和执行。

CPU、RAM和ROM可以由外部复位线控制。当复位被激活时,寄存器和触发器的内容被清除。重置后,CPU将从地址0和CM-RAM0开始。

MCS-4可以有多达4K x 8位ROM字,1280 x 4位RAM和128 I/O行,不需要任何连接逻辑。通过添加一些简单的门,MCS-4可以有多达48个RAM和ROM的任何组合和192 I/O行。

4001、4002和4004由4线数据总线(D0、D1、D2、D3)连接,用于芯片之间的所有信息流,除了CPU在另外6条线路上发送的控制信号。MCS-4系统的互连如上图所示。显示了一个扩展配置。最小系统配置由一个CPU(4004)和一个ROM组成(4001)。指令周期图显示了每个时钟周期内数据总线上的活动,以及如何细分基本指令周期。

每个数据总线输出缓冲区都有三个可能的状态“1”、“0”和浮点数。在给定的时间内,只允许一个输出缓冲区驱动数据线,因此,所有其他缓冲区必须处于浮动状态。但是,每个数据行可以同时接收多个输入缓冲区MCS-4有一个非常强大的指令集,允许二进制和十进制算术。它包括条件分支。跳转到子例程,并提供了通过间接获取有效使用ROM查找表。通常,850 usec中可以添加两个8位数字。

这就是MCS-4微型计算机的基本结构。