可编程中断控制器8259A

- 8259A的外部引线

- 8259A的内部结构

- 8259A的工作过程

- 8259A的工作方式

- 8259A的初始化编程

8259A的外部引线

采用28脚双列直插式封装。

- D0~D7:双向数据线,与系统的数据总线相连。编程时控制字,命令字由此写入;中断响应时,中断向量码由此送给CPU。

- /WR,/RD为读写控制信号,与系统总线的/IOW,/IOR相连接。

- /CS为片选信号,当/CS为低电平时,8259A被选中,CPU才能对它进行读写操作。此引脚连到系统的I/O译码器输出,由此确定8259A在系统I/O地址空间的基地址。

- A0是8259A内部寄存器的选择信号,它与/CS,/WR,/RD信号相配合,对不同的内部寄存器进行读写。使用中,通常接地址总线的某一位,例如A1,A0等。

- INT为8259A的中断请求输出信号,可以直接接到CPU的INTR输入端。

- /INTA为中断响应输入信号,在中断响应过程中CPU的中断信号由此端进入8259A。

- CAS0~CAS2为级联控制线。当多片8259A级联工作时,其中一片为主控芯片,其它均为从属芯片。对于主片的8259A,其CAS0到CAS2为输出,对于各从属芯片的CAS0到CAS2为输入。主片的CAS0到CAS2与从片相同引脚对应相连。当从片提出中断请求时,主片通过CAS0到CAS2送出相应的编码给从片,使得从片的中断被允许。

- /SP/EN为双功能引线,工作在缓冲模式时,为输出,控制缓冲器的传送方向。CPU–>8259A为高电平,数据从8259A–>CPU为低电平。工作在非缓冲方式时,为输入,指定8259A是否为主片从片。/SP=1为主片,/SP=0为从片。系统中只有一片8259A时,接高电平。

- IR0~IR7为中断请求输入信号,与外设中断请求线相连,上升沿或高电(可编程设定)时表示有中断请求到达。

8259A的内部结构

8259A的内部结构如图所示:

由中断请求寄存器IRR,中断服务寄存器ISR。中断屏蔽寄存器IMR,中断判优电路,数据总线缓冲器,读/写电路,控制逻辑和级联缓冲/比较器组成。

-

中断请求寄存器IRR:

保存从IR0-IR7来的中断请求信号。某一位为1表示相应引脚上有中断请求信号。该中断请求信号至少应保持到该请求被响应为止。中断响应后,该IR输入线上的请求信号应撤销,否则,在中断处理完结后,该IR线上的高电平可能会引起又一次中断服务。 -

中断服务寄存器ISR:

ISR用于保存所有正在服务的中断源。是8位的寄存器(IS0-IS7分别对应IR0-IR7)。在中断响应时,判优电路。把发出中断请求的中断源中优先级最高的中断源所对应的位置1,表示该中断请求正在处理中,ISR的某一位ISi置1可阻止与它同级及更低优先级的请求被响应,但不阻止比它优先级更高的中断请求被响应,即允许中断嵌套,所以,ISR中可能不只有一位被置1,当8259A收到中断结束(EOI)命令时,ISR相应位会被清除。对自动EOI操作,ISR寄存器中刚被置1的位在中断相应结束时自动复位。 -

中断屏蔽寄存器IMR:

IMR用于存放中断屏蔽字,它的每一位分别与IR7~IR0相对应。其中为1的位所对应的中断请求输入将被屏蔽,为0的位所对应的中断请求输入不受影响。 -

中断判优电路

中断判优电路监测从IRR,ISR,和IMR来的输入,并确定是否应向CPU发出中断请求。在中断响应时,它要确定ISR寄存器哪一位应置1,并将相应的中断类型码送给CPU。在EOI命令时,它要决定ISR寄存器哪一位应复位。

8259A的工作过程

当系统通电后,首先应对8259A初始化,也就是由CPU执行一段程序,向8259A写入若干控制字,指定它的工作方式。初始化完成后,8259A就准备好了,随时可以接受外设的中断请求信号,当外设发出请求后,8259A对外部中断请求的处理过程如下:

5. 哪条IR线上的数据有效,IRR相应位置就置1。

6. 至少有一条中断没有被屏蔽,都屏蔽了中断输入无意义,8259A由INT引脚向CPU发INTR信号。

7. 恰好CPU处于开中断状态,完成当前指令后,用/INTR信号响应,告诉8259A收到了中断请求。

8. 8259A接收到CPU发出的第一个/INTA脉冲后,把最高优先权的ISR置1,并使相应的IRR复位。

9. 第二个中断响应周期中,CPU再输出一个/INTA脉冲,这时8259A就把刚才选定的中断源所对应的8位中断类型码放到数据总线上,CPU读取该中断类型码并乘以4,就是中断服务子程序在中断向量表中的入口地址。找到执行。

10. 若8259A工作在自动中断结束AEOI方式,在第二个/INTA脉冲结束时,把中断源所对应的ISR中相应位复位。对于非自动中断结束方式,则由CPU在中断服务子程序结束时向8259A写入EOI命令,才能使ISR中的相应位复位。

8259A的工作方式

- 中断优先方式与中断嵌套

中断优先方式:

固定优先级:各中断请求中断优先级固定不变,8259A加电后就处于这种方式,默认IR0优先级最高,IR7优先级最低,可改变默认值。

循环优先级: 实际应用中,许多中断源的优先级别是一样的,如果固定优先级,低级别的中断源可能总得不到服务。使这些中断源轮流处于最高优先级。一个中断源得到中断服务后,优先级自动降到最低,原来它的下一级中断源变为最高级,依次排列。

中断嵌套:

允许更高优先级的中断打断当前的中断处理过程。

普通全嵌套方式: 8259A最常用的工作方式,CPU响应中断时,8259A把优先权最高的中断源在ISR中置1,把它的中断类型码送到数据总线,在此中断服务子程序结束之前,比它低的或同级的被屏蔽,只有优先权高的才被允许。

特殊全嵌套方式:与普通全嵌套的区别是:同级的中断请求8259A也会响应。从而实现中断处理过程能被同级别中断请求打断。一般用在8259A级联的系统中。在这种情况下,只有主片8259A允许编程为特殊全嵌套模式。这时,来自某一从片的中断请求正在处理时,主片除了对本片上优先级较高的引脚上的中断请求处理开放,同时对于从片较高优先级的请求也会开放。 这种模式下,中断结束时,通过软件检查是否为从片唯一中断,向从片发一正常结束命令EOI,然后读ISR内容。如果为0表示只有一个中断服务,这时再向主片发一个EOI命令,结束所有中断;否则,说明从片上有两个以上的中断,则不应再向主片发EOI命令,等待该从片中断服务全部结束后,再发EOI给主片。

2.中断结束处理方式

不管用哪种优先权方式工作,当一个中断请求IRi得到响应时,8259A都会将ISR中相应ISi置1.中断服务结束时清零。否则会引起总线竞争(我认为)。这个复位动作就是中断结束处理。这里的中断结束是指8259A结束中断的处理,而不是CPU结束执行中断服务子程序。

自动中断结束方式(AEOI): 第二个中断响应周期/INTA信号的后沿,8259A自动把ISR中的对应位消除,CPU在执行中断服务,ISR中没有保留正在执行中断服务的状态。只能用于没有中断嵌套的情况。

正常中断结束方式(EOI):配合全嵌套优先权方式使用,CPU向8259A发出EOI命令,8259A就会把ISR中置1的最高位复位。因为在全嵌套方式中ISR中置1的位对应的是最后一次被响应和处理的中断。复位操作相当于结束了当前正在处理的中断。

特殊中断结束方式(SEOI): 在程序中发一条特殊的中断结束命令,这个命令指出了要擦除ISR中的哪一位。

不管是EOI还是SEOI,在一个中断服务子程序结束时,对于级联使用的8259A都必须发两次中断结束命令,一次给主片,一次给从片。

3.屏蔽中断源的方式:

8259A的8个中断请求都可根据需要单独屏蔽,(IMR置0或1)

普通屏蔽方式: 很简单,IMR置1,对应IRi被屏蔽,中断请求不能从8259A送到CPU,置0,反之。

特殊屏蔽方式: (SMM)为了动态改变系统优先权结构,在IRi的处理过程中,希望除了IRi以外的所有中断请求均可被响应,首先设置特殊屏蔽方式,再编程将IRi屏蔽掉,使得这一位复位。提供了允许较低优先级中断源得到响应的特殊手段。但是打乱了原来正常的嵌套结构,被处理的程序不一定是最高优先级的事件。所以不能用正常的EOI命令来使ISR复位。但是退出SMM方式之后,仍可以用正常的EOI结束中断。

ps:这个我感觉有点像有关系走后门,可以为所欲为,但是破坏了原来的秩序。你对他还没有办法:)

4.中断触发方式:

边沿触发方式: 8259A的引脚IRi上出现上升沿表示有中断请求,高电平并不表示有中断请求。

电平触发方式: 8259A的引脚IRi上出现高电平表示有中断请求。在这种方式下,应该及时撤除高电平,否则可能引起不应该有的第二次中断。

无论是边沿触发还是电平触发,中断请求信号IR都应维持足够的宽度,就是在第一个中断响应信号/INTA结束之前IR都必须保持高电平。如果IR信号提前变为低电平,8259A就会自动假设这个中断请求来自引脚IR7.这样能有效防止由IR输入端上的严重噪声尖峰而产生的中断,如果IR7被使用,仍可通过读ISR状态来识别非正常的IR7中断。(正常的IR7中断会使ISR的IS7置位,而非正常的IR7中断不会)

5.级联工作方式:

中断源超过8个,无法用一片8259A来进行管理,这时候使用级联工作方式。指定一片为主片,其余为从片。主片的INT接到CPU上,其余的从片INT输出分别接到主控芯片的IR输入端。一片有八个中断输入端,所以最多有64个中断输入。

在级联系统中,每一片8259A,不管是主片还是从片,都有各自独立的初始化程序,以便设置各自的工作状态。中断结束要发两次EOI命令,分别使主片和从片完成中断结束操作。

中断响应过程中,若中断请求来自从片的IR,中断响应时,主片8259A会通过级联控制线CAS0~CAS2来通知相应从片的8259A,从片即可把中断向量码放到数据总线上。

级联方式下,可以采用前面说的特殊全嵌套方式,允许从片上优先级更高的IR产生中断。主片初始化为特殊全嵌套方式后,从片结束中断时,要用软件来检查ISR的内容,看看本片上有没有其它中断请求未被处理,如果没有,连发两个EOI,使主片,从片结束中断,如果还有其它中断,只发一个EOI命令。

(这个前面说过)

8259A的初始化编程

初始化编程不必多说,就是写入控制命令字,为我所用。

控制命令字分为:初始化命令字ICW, 操作命令字OCW

写入8259A后保存在内部的ICW和OCW寄存器中。

初始化编程:由CPU向 8259A送2~4个字节的初始化命令字ICW。在 8259A工作之前,必须写入初始化命令字

操作方式编程:由CPU向 8259A送3个字节的操作命令字OCW。以规定8259A的操作方式,可在初始化后的任何状态写入。

1.8259A内部寄存器寻址方法

靠/CS,A0,/RD,/WR和数据线D4,D3配合寻址。

2.8259A初始化顺序

对8259A进行写时,若I/O地址是奇数(A0=1),则写的对象包括四个寄存器(ICW2,ICW3,ICW4,ICW1)即一个I/O地址对应了4个寄存器。按照下图顺序写入。

3.8259A内部控制字

初始化命令字ICW

ICW1–初始化字,写入条件上上图,这时写入的数据被当成ICW1,意味着重新初始化8259A,同时:

清除ISR,IMR

中断优先级设置为初始状态,IR0最高,IR7最低

设定为普通屏蔽方式

采用非自动EOI中断结束方式

状态读出电路设置为读IRR

ICW1各功能如图所示

ICW2–中断向量码

ICW2为中断向量码寄存器,CPU响应中断时,放到数据总线。

初始化只需要确定T6~T3,低三位可以任意,8259A中断响应时自动填入。

ICW3–级联控制字

仅在多片级联时需要写入,主片与从片格式不同

主片标识码图上写的很明白,从片标识码与连接主片的IR序列号一致。

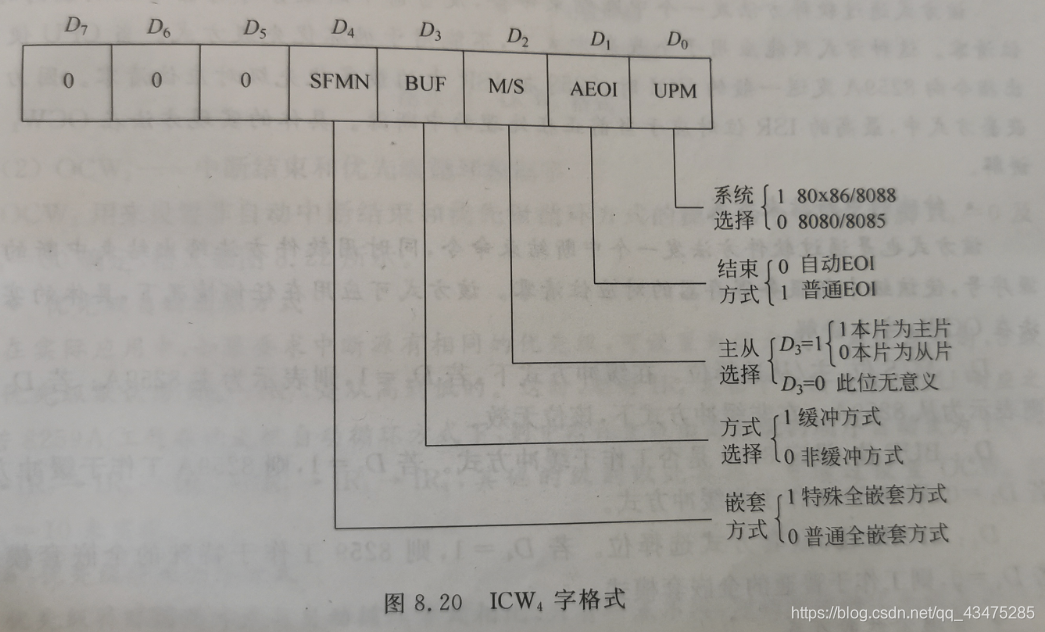

ICW4–中断结束方式字

紧跟ICW3写入同一I/O地址中

缓冲方式用于在级联工作时增大数据驱动能力,/SP/EN端作为输出端,输出一个允许信号。用来控制缓冲器的工作此时主片从片由D2位区分,主片=0,从片=1;非缓冲方式/SP/EN端为输入端,用以区分主片(高电平),从片(低电平)

操作命令字OCW

用来改变8259A 的中断控制方式,屏蔽中断源,以及读出8259A的工作状态(IRR,ISR,IMR),初始化完成后任意状态皆可写入,顺序也没有严格要求,但是对端口地址有规定:OCW1奇地址端口(A0=1),OCW2,OCW3必须为偶地址端口。

OCW1–中断屏蔽字

是否屏蔽中断,

OCW2–中断结束和优先级循环

对8259A发中断结束命令EOI,还可以控制中断优先级循环,与OCW3共用一个端口地址,有特征位D4D3=00,写入要求为偶地址。

R:优先级循环控制位:0固定优先级,IR7最低,IR0最高。1循环优先级。前面说了循环优先级

SL:特殊循环控制。SL=1,L2~L0对应的中断为最低优先级,SL=0时,对应的中断编码无效

EOI:中断结束命令,为1复位ISR相应位,,在ICW4的AEOI=0时,需要用OCW2来复位

OCW3–屏蔽方式和状态读出控制字

查询中断请求,CPU禁止中断或不想让8259A申请中断,CPU先写一个P=1的OCW3到8259A,再对同一地址读入。

I=1:表示本片8259A有中断请求,最高优先级的IR线由后三位编码组合给出

I=0;无中断请求

查询状态可重复进行,为了响应同时发生的中断。

读8259A状态

使用OCW3命令控制读出IRR,ISR,IMR的内容。

CPU先写RR RIS=10,再对同一地址读,为IRR内容

ISR同理

A0=1时读8259A,为IMR(不依赖OCW3)