文章目录

- 1中断简介

- 1.1中断

- 1.2禁止中断与中断屏蔽

- 1.3中断嵌套

- 1.4中断类型号和中断向量表

- 2,8259A简介

- 2.1 8259A介绍

- 2.2 8259A内部结构

- 2.3 8259A引脚

- 2.3.1 与CPU相连的引脚

- 2.3.2 与外设相连的引脚

- 2.4 8259a可编程寄存器

1中断简介

1.1中断

定义:CPU暂停当前程序的执行,转而执行处理紧急事务的程序,并在该事务处理完后能自动恢复执行原先程序的过程。在此,称引起紧急事务的事件为中断源,称处理紧急事务的程序为中断服务程序或中断处理程序

CPU中的中断源分为内中断和外中断,外中断又分为可屏蔽中断(INTR)和不可屏蔽中断(NMI)

1.2禁止中断与中断屏蔽

在某些情况下,CPU可能不允许响应可屏蔽中断INTR,此时当中断源向CPU申请中断后.CPU就不能终止当前正在运行的程序并转到中断服务程序,这种情况称为禁止中断。一般在 CPU内部有个中断允许触发器.只有当该触发器的状态为允许状态时 ,CPU才能响应外部中断,否则CPU禁止中断。中断允许触发器可以通过指令STI 进行置位和指令CLI进行复位,以达到CPU允许中断和禁止中断的目的。

在另外一种情况下,CPU不能响应几种特殊类型的中断,而其余的中断则可以响应,这就叫作中断屏蔽。

中断屏蔽可以通过中断屏蔽触发器来实现,将中断源对应的中断屏蔽触发器置1,则该中断源的中断请求被屏蔽,否则该中断源的中断请求被允许。中断允许触发器在CPU内部,其控制所有INTR中断源的允许与禁止。中断屏蔽寄存器在CPU外部,设置在中断控制器8259内部,其控制部分INTR中断源的允许与禁止。

1.3中断嵌套

当CPU正在处理某种类型的中断时,又有级别更高的新中断源申请中断,这时CPU就会暂停当前的中断服务程序,而转去执行新的中断处理,这种中断处理方式就叫作中断嵌套

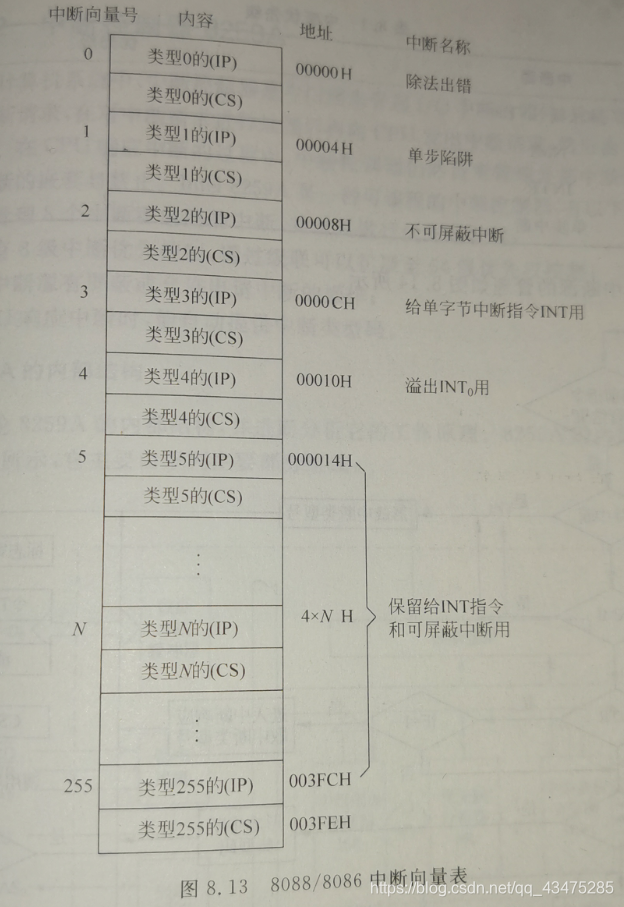

1.4中断类型号和中断向量表

- 中断向量:中断服务程序的入口地址(首地址)

- 逻辑地址包括段地址CS和偏移地址IP(共32位)

- 每个中断向量占用4个字节

- 物理地址00000H开始,依次安排各个中断向量,向量号从0开始

- 256个中断占用1KB区域,就形成中断向量表

- 向量号为N的中断向量的物理地址=N×4

2,8259A简介

2.1 8259A介绍

8259a:为8088、80286等CPU设计的一种可编程中断控制器PIC(Programmable Interrupt Controller),接收外部中断源的请求,在对中断源进行处理后向CPU发出中断请求,然后由CPU响应中断并处理

功能:

①管理8级中断,多片级连可扩展至64级;

②在中断响应周期提供相应的中断向量号

③可通过编程选择多种工作方式。

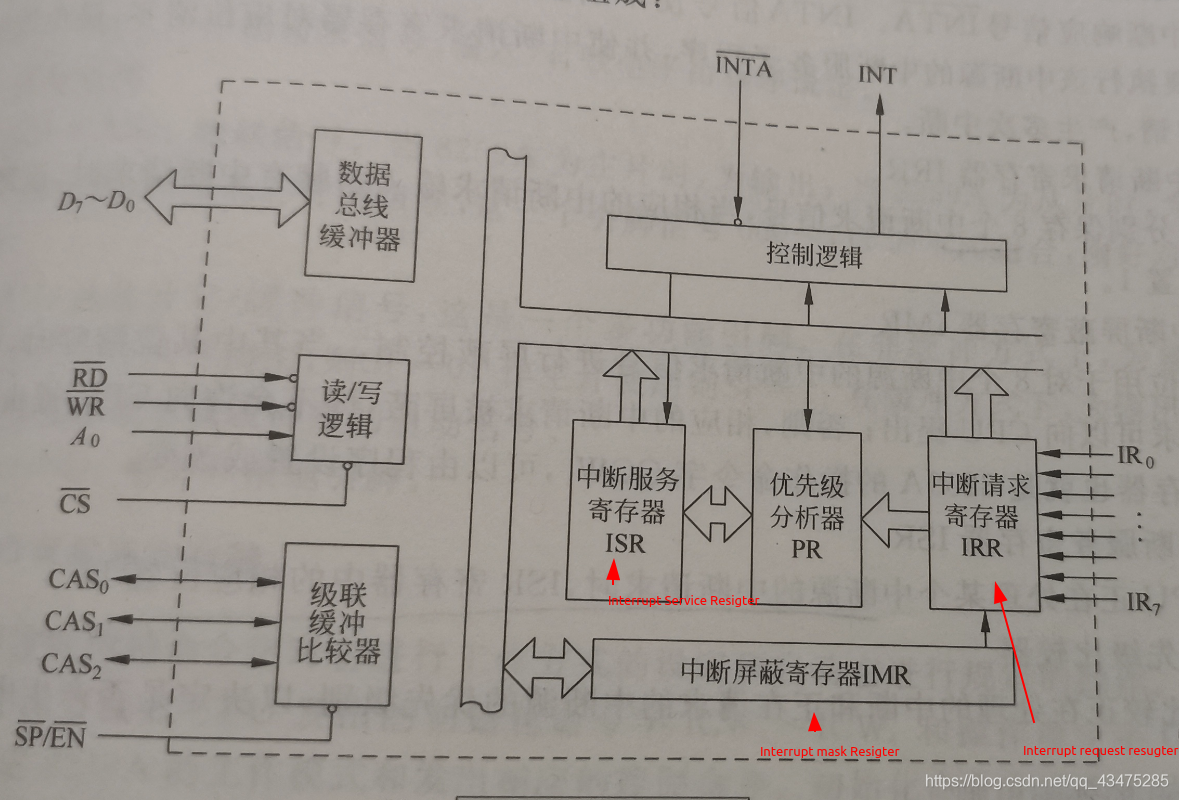

2.2 8259A内部结构

(1) 中断请求寄存器IRR (Interrupt Request Resgister)表示相应中断请求线是否有中断请求信号。保存8个中断请求信号,当相应的中断请求有中断请求时,该寄存器相应位置置1

(2) 中断服务寄存器ISR (In-Service Register)用于表示相应的中断是否正在服务中。当CPU正在处理某个中断源的中断请求时,ISR相应位置1

(3) 中断屏蔽寄存器IMR (Interrupt Mask Register) 用于对8个中断源进行屏蔽控制。当某位清零时,则相应的中断请求可以向CPU提出,否则不可以

1 —屏蔽,0 —允许

(4) 优先权电路PR(Priority Resigter):用于比较正在处理的中断和正在请求的中断源的优先级别,确定各中断请求的优先权。

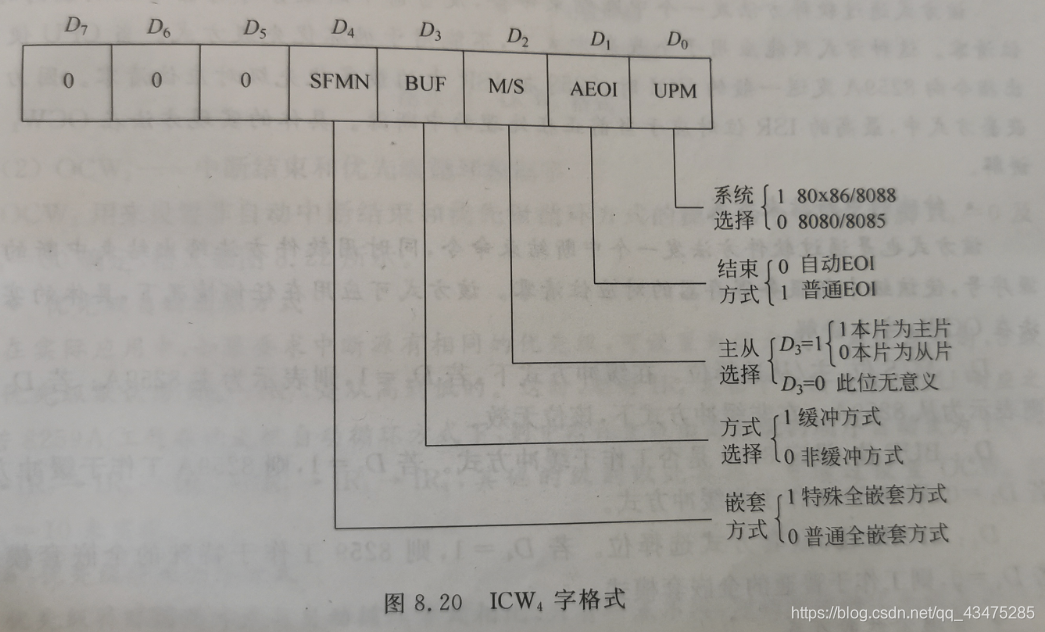

(5) 控制逻辑:向CPU发送中断请求信号,并接受响应信号。控制逻辑有6个寄存器,ICW1–ICW4用来存放初始化程序的工作字方式,管理8259A的工作,OCW2—OCW3用来存放操作命令字,对中断过程进行控制

(6) 数据总线缓冲器:接收CPU的命令数据,发送状态信息及向量号。

(7) 读/写控制逻辑:接收CPU发来命令信号。实现对8259A的读/写操作

(8) 级联缓冲比较器:实现8259A的ID号的存储与比较。用以实现8259A芯片的级联,最高由8级拓展到64级

2.3 8259A引脚

8259A一共28个引脚,一组与CPU相连,一组与设备相连

2.3.1 与CPU相连的引脚

D7~D0:数据线,双向,三态。与系统的数据总线相连,与CPU进行信息交换

1,A0:奇/偶地址选择信号

2,/CS:片选信号,低电平有效,输入。决定8259A端口地址范围

3,/(WR):写控制信号,输入,低电平有效

4,/(RD):读控制信号,输入,低电平有效

5,INT:(Interrupt):中断请求信号,输出,高电平有效。与CPU的 INTR(Interrupt Request)相连,向CPU发出中断请求

6,/(INTA):Interrupt Acknowledgement 中断响应信号,输入,低电平有效,与CPU的/(INTA)相连,在CPU发出第二个/(INTA)信号时,8259A将最高级别的中断请求的中断类型码传给CPU

2.3.2 与外设相连的引脚

1,CAS2~CAS0:级联信号

2,/(SP)/ /(EN):从片开启/缓冲信号

3,+5V,GND:接地

2.4 8259a可编程寄存器

8259a在工作前要先接受初始化命令字ICW1-ICW4和操作命令字OCW1-OCW3,

ICW1

ICW2

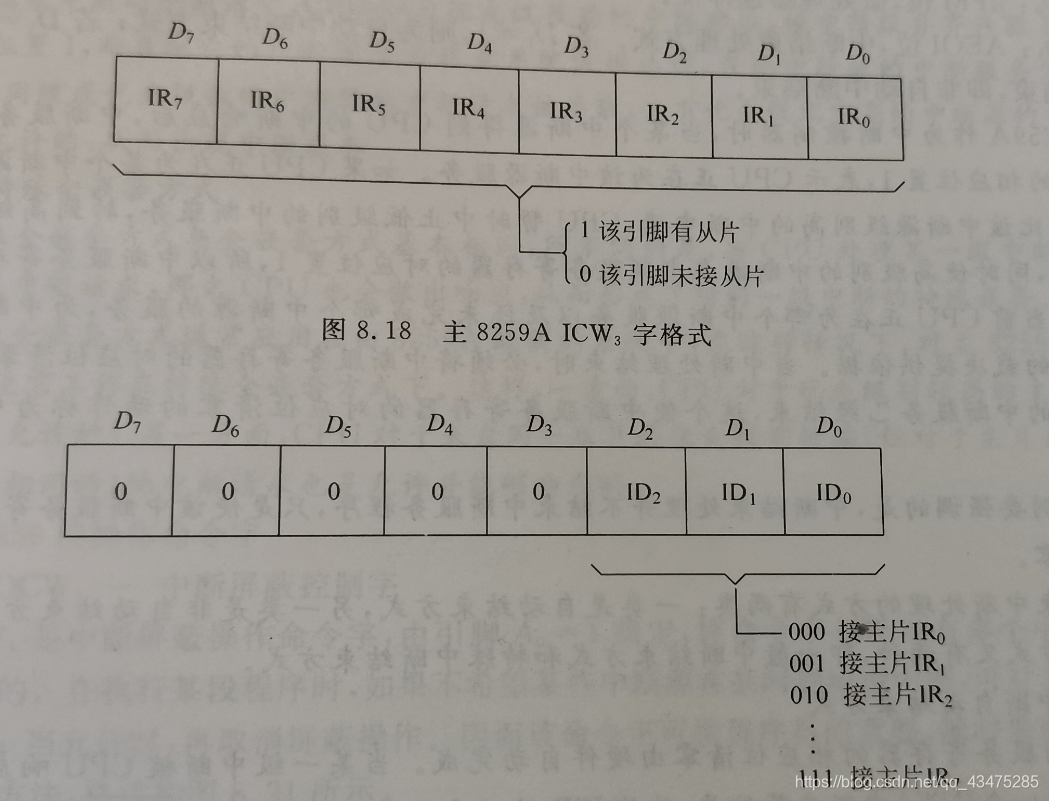

ICW3

ICW4