1. ip core 应用场景

使用Intel FPGA自带的LVDS ip core进行电路板之间的串行数据收发以及并串、串并转换(Serdes)。

两块电路板之间相隔100m,使用双绞线作为传输介质,串行码流的速率为163.84Mbps,由于长距离传输中,高频信号衰减严重,采用预加重和均衡的技术补偿高频信号衰减,发送端采用LMH0001做预加重处理,接收端采用LMH0074做均衡处理。

2.数据传输逻辑框图

数据传输逻辑功能框图如上图所示,为保持串行码流的直流平衡,发送端采用8B/10B编码,对应的接收端需要对应的10B/8B解码模块。

3.需要注意的细节

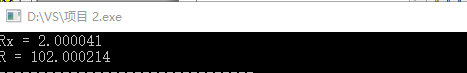

3.1预加重芯片(LMH0001)的参考电阻Rref影响输出差分电压的摆幅,进而影响传输的误码率,经过测量,当电阻值为470Ω,传输无误码。

3.2 接收端数据字节对齐处理(Word align)

接收端从串行码流中恢复出并行数据,需要用到altlvds rx ip的rx_data_align端口,ip配置的端口如下图所示。 具体做法为发送端先发送一定数目的K码(K28.5),接收端通过rx_data_align端口对并行数据进行移位操作,当接收端的并行数据为K28.5时,表示字节对齐完成,可正确接收数据。

具体做法为发送端先发送一定数目的K码(K28.5),接收端通过rx_data_align端口对并行数据进行移位操作,当接收端的并行数据为K28.5时,表示字节对齐完成,可正确接收数据。