目录

1、简介

2、时钟树

2.1、时钟源

2.2、时钟模式

2.3、各模块的时钟频率

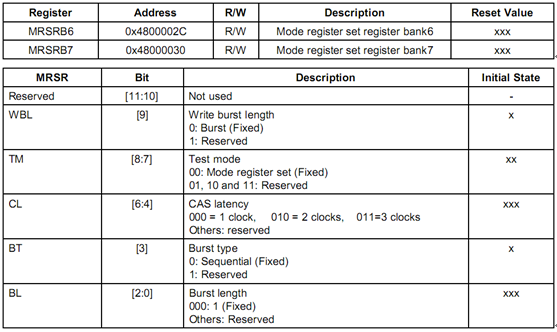

3、寄存器

3.1、SCG_VERID:Version ID Register

3.2、SCG_PARAM:Parameter Register

3.3、SCG_CSR:Clock Status Register

3.4、SCG_RCCR:Run Clock Control Register

3.5、SCG_VCCR:VLPR Clock Control Register

3.6、SCG_HCCR:HSRUN Clock Control Register

3.7、SCG_CLKOUTCNFG:SCG CLKOUT Configuration Register

3.8、SCG_SOSCCSR:System OSC Control Status Register

3.9、SCG_SOSCDIV:System OSC Divide Register

3.10、SCG_SOSCCFG:System Oscillator Configuration Register

3.11、SCG_SIRCCSR:Slow IRC Control Status Register

3.12、SCG_SIRCDIV: Slow IRC Divide Register

3.13、SCG_SIRCCFG: Slow IRC Configuration Register

4、时钟代码配置

4.1、SOSC时钟源配置

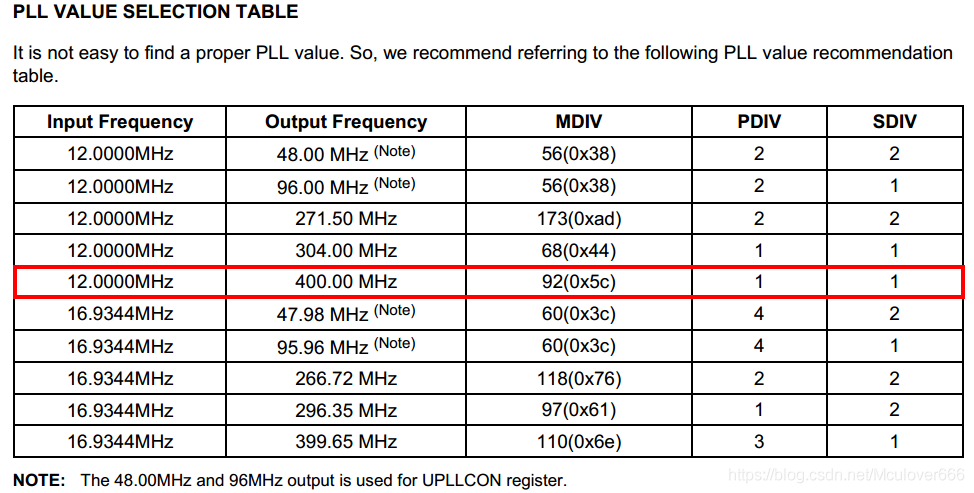

4.2、SPLL高速时钟配置

4.3、运行时钟配置

博客只是用于记录自己使用过的东西,将自己的感想和使用方法记录,过程可能会出现很多纰漏以及理解的不到位,希望可以和大家交流

1、简介

开发板S32K144+S32DS+JLINK

2、时钟树

其中可以看到

2.1、时钟源

| Fast IRC(内部高速时钟源) | 48 MHz |

| Slow IRC(内部低速时钟源) | 可选2 - 8 MHz |

| LPO(内部低功耗时钟源) | 128kHz |

| SOSC(外部时钟源) | 8MHz |

2.2、时钟模式

HSRUN模式下等待CORE_CLK和SYS_CLK的时钟频率最高支持112MHz

RUN模式下的时钟频率最高支持80MHz,但是不能小于BUS_CLK时钟频率

BUS_CLK频率最高支持56MHz和HSRUN模式下最高支持48MHz

FLASH——CLK频率最高支持28MHz和HSRUN模式下26.67MHz或更小

如参考手册的时钟模式选项,仅仅给出几个常用的:

总结了S32K14x/S32K11x最大频率和示例,各内部时钟配置:

2.3、各模块的时钟频率

| LPUART | BUS_CLK |

| LPSPI | BUS_CLK |

| LPI2C | BUS_CLK |

| FlexIO | BUS_CLK |

| LPTMR | BUS_CLK |

| LPIT | BUS_CLK |

| RTC | BUS_CLK |

| WDOG | BUS_CLK |

| EWM | BUS_CLK |

| PMC | BUS_CLK |

| SIM | BUS_CLK |

| RCM | BUS_CLK |

| CRC | BUS_CLK |

| PORT | BUS_CLK |

| TRGMUX | BUS_CLK |

| DMAMUX | BUS_CLK |

| CMU | BUS_CLK |

| ADC | BUS_CLK |

| CMP | BUS_CLK |

| SAI | BUS_CLK |

| QuadSPI | BUS_CLK/ |

| FlexCAN | SYS_CLK |

| PDB | SYS_CLK |

| FlexTimer | SYS_CLK |

| GPIO | SYS_CLK |

| DMA | SYS_CLK |

| MPU | SYS_CLK |

| EIM | SYS_CLK |

| ERM | SYS_CLK |

| MSCM | SYS_CLK |

| System RAM | SYS_CLK |

| ENET | SYS_CLK |

| FTFC | FLASH_CLK |

3、寄存器

寄存器有很多个保留位,这些保留位默认为0且只读,如果写入将会导致错误

3.1、SCG_VERID:Version ID Register

SCG的版本号

3.2、SCG_PARAM:Parameter Register

参数寄存器,其中32位的定义如下,其他的为保留位

| Field | Name | Description |

| 31-27 | DIVPRES | 指示现在的SCG分频器使用状态 DIVPRES[27]=1 DIVSLOW 正在被使用 DIVPRES[28]=1 DIVBUS 正在被使用 DIVPRES[31]=1 DIVCORE 正在被使用 |

| 7-0 | CLKPRES | 指示当前状态下哪个时钟正在被当做 SCG 时钟源 CLKPRES[0] Reserved CLKPRES[1]=1 System OSC (SOSC) 正在被使用 CLKPRES[2]=1 Slow IRC (SIRC) 正在被使用 CLKPRES[3]=1 Fast IRC (FIRC) 正在被使用 CLKPRES[6]=1 System PLL (SPLL) 正在被使用 |

3.3、SCG_CSR:Clock Status Register

返回当前的系统时钟源和系统时钟分频器配置,镜像SCG_RCCR,SCG_VCCR,SCG_HCCR三个时钟控制器之一的配置

| Field | Name | Description |

| 27-24 | SCS | 返回当前配置的系统时钟发生器来源 0001 System OSC (SOSC_CLK) 0010 Slow IRC (SIRC_CLK) 0011 Fast IRC (FIRC_CLK) 0110 System PLL (SPLL_CLK) 其余的值无效 |

| 19-16 | DIVCORE | 指示现在的核心时钟分频比率 * 若 SPLL 被选做时钟源,则最大比率是 4 分频比率 = |

| 7-4 | DIVBUS | 返回现在的总线(BUS)时钟分频比率 |

| 3-0 | DIVSLOW | 返回现在的慢速时钟分频比率 |

3.4、SCG_RCCR:Run Clock Control Register

寄存器给核心,平台,外围,总线控制系统时钟源和系统时钟分频器,只在 Run 模式下起作用,这个寄存器写入的时候只能一次写入 32 位。

在 Run 模式下选择一个不同的时钟源需要时钟源在系统时钟调整到时钟源前就要开启并且保证有效

如果系统时钟分频器比率改变的同时选择了一个不同的时钟模式,则新的分频器比率只有在新的时钟源有效后才会发生改变。

3.5、SCG_VCCR:VLPR Clock Control Register

SCG_VCCR 控制的是 VLPR 模式下的,而不是 Run 模式下的,其他的寄存器地图什么的和 SCG_RCCR 一样。写入的时候只能一次写入 32 位。

3.6、SCG_HCCR:HSRUN Clock Control Register

在 HSRUN 模式下的时钟控制寄存器

3.7、SCG_CLKOUTCNFG:SCG CLKOUT Configuration Register

控制哪一个 SCG 时钟源被输出到 CLKOUT 管脚

| Field | Name | Description |

| 27-24 | SCS | 选择 SCG 系统时钟作为 CLKOUT 0001 System OSC (SOSC_CLK) 0010 Slow IRC (SIRC_CLK) 0011 Fast IRC (FIRC_CLK) 0110 System PLL (SPLL_CLK) 其余的值无效 |

3.8、SCG_SOSCCSR:System OSC Control Status Register

寄存器控制 SCG 模块中的 SOSC 工作状态

| Field | Name | Description |

| 26 | SOSCERR | System OSC Clock Error 此位只能被单片机的上电复位重置,但是软件也可以通过向此位写入 1 清零 0 SOSC 检测器被关闭或者没有检测到错误 1 SOSC 检测器被开启并且检测到一个错误 |

| 25 | SOSCSEL | System OSC Selected 此位不可写入 |

| 24 | SOSCVLD | System OSC Valid 此位不可写入 |

| 23 | LK | Lock Register |

| 17 | SOSCCMRE | System OSC Clock Monitor Reset Enable |

| 16 | SOSCCM | System OSC Clock Monitor |

| 0 | SOSCEN | System OSC Enable |

3.9、SCG_SOSCDIV:System OSC Divide Register

寄存器控制两个时钟输出,既可以用作外围器件的功能时钟,也可以作为时钟模块使用,每一路输出都有分频器提供分频,

应该在 SOSC 被关闭的情况下更改该寄存器的值以避免输出的值出现错误。

| Field | Name | Description |

| 10-8 | SOSCDIV2 | System OSC Clock Divide 2 |

| 2-1 | SOSCDIV1 | System OSC Clock Divide 1 |

3.10、SCG_SOSCCFG:System Oscillator Configuration Register

寄存器控制振荡器的工作状态,在 SOSC 运行的时候无法被写入,强行写入会被忽略并不会报赋值错误。

| Field | Name | Description |

| 5-4 | RANGE | System OSC Range Select |

| 3 | HGO | High Gain Oscillator Select |

| 2 | EREFS | External Reference Select |

3.11、SCG_SIRCCSR:Slow IRC Control Status Register

| Field | Name | Description |

| 25 | SIRCSEL | Slow IRC Selected |

| 24 | SIRCVLD | Slow IRC Valid |

| 2 | SIRCLPEN | Slow IRC Low Power Enable |

| 1 | SIRCSTEN | Slow IRC Stop Enable |

| 0 | SIRCEN | Slow IRC Enable |

3.12、SCG_SIRCDIV: Slow IRC Divide Register

寄存器控制 SIRC 的分频器工作状态,请确保该寄存器在改变前,SIRC 是关闭着的,以防止出现错误

| Field | Name | Description |

| 10-8 | SIRCDIV2 | Slow IRC Clock Divide 2 |

| 2-1 | SIRCDIV1 | Slow IRC Clock Divide 1 |

3.13、SCG_SIRCCFG: Slow IRC Configuration Register

| Field | Name | Description |

| 0 | RANGE | Frequency Range |

剩余的 FIRC 跟这个差不多,但是有一部分细微的变化,到用的时候请查询对应的用户手册。

4、时钟代码配置

4.1、SOSC时钟源配置

void SOSC_init_8MHz(void)

{/*!* SOSC Initialization (8 MHz):* ===================================================*/SCG->SOSCDIV = SCG_SOSCDIV_SOSCDIV1(1)|SCG_SOSCDIV_SOSCDIV2(1); /* SOSCDIV1 & SOSCDIV2 =1: divide by 1 */SCG->SOSCCFG = SCG_SOSCCFG_RANGE(2)| /* Range=2: Medium freq (SOSC betw 1MHz-8MHz) */SCG_SOSCCFG_EREFS_MASK; /* HGO=0: Config xtal osc for low power *//* EREFS=1: Input is external XTAL */while(SCG->SOSCCSR & SCG_SOSCCSR_LK_MASK); /* Ensure SOSCCSR unlocked */SCG->SOSCCSR = SCG_SOSCCSR_SOSCEN_MASK; /* LK=0: SOSCCSR can be written *//* SOSCCMRE=0: OSC CLK monitor IRQ if enabled *//* SOSCCM=0: OSC CLK monitor disabled *//* SOSCERCLKEN=0: Sys OSC 3V ERCLK output clk disabled *//* SOSCLPEN=0: Sys OSC disabled in VLP modes *//* SOSCSTEN=0: Sys OSC disabled in Stop modes *//* SOSCEN=1: Enable oscillator */while(!(SCG->SOSCCSR & SCG_SOSCCSR_SOSCVLD_MASK)); /* Wait for sys OSC clk valid */

}4.2、SPLL高速时钟配置

void SPLL_init_160MHz(void)

{/*!* SPLL Initialization (160 MHz):* ===================================================*/while(SCG->SPLLCSR & SCG_SPLLCSR_LK_MASK); /* Ensure SPLLCSR unlocked */SCG->SPLLCSR &= ~SCG_SPLLCSR_SPLLEN_MASK; /* SPLLEN=0: SPLL is disabled (default) */SCG->SPLLDIV |= SCG_SPLLDIV_SPLLDIV1(2)|/* SPLLDIV1 divide by 2 */SCG_SPLLDIV_SPLLDIV2(3); /* SPLLDIV2 divide by 4 */SCG->SPLLCFG = SCG_SPLLCFG_MULT(24); /* PREDIV=0: Divide SOSC_CLK by 0+1=1 *//* MULT=24: Multiply sys pll by 4+24=40 *//* SPLL_CLK = 8MHz / 1 * 40 / 2 = 160 MHz */while(SCG->SPLLCSR & SCG_SPLLCSR_LK_MASK); /* Ensure SPLLCSR unlocked */SCG->SPLLCSR |= SCG_SPLLCSR_SPLLEN_MASK; /* LK=0: SPLLCSR can be written *//* SPLLCMRE=0: SPLL CLK monitor IRQ if enabled *//* SPLLCM=0: SPLL CLK monitor disabled *//* SPLLSTEN=0: SPLL disabled in Stop modes *//* SPLLEN=1: Enable SPLL */while(!(SCG->SPLLCSR & SCG_SPLLCSR_SPLLVLD_MASK)); /* Wait for SPLL valid */

}

4.3、运行时钟配置

void NormalRUNmode_80MHz (void)

{

/*! Slow IRC is enabled with high range (8 MHz) in reset.* Enable SIRCDIV2_CLK and SIRCDIV1_CLK, divide by 1 = 8MHz* asynchronous clock source.* ==========================================

*/SCG->SIRCDIV = SCG_SIRCDIV_SIRCDIV1(1)| SCG_SIRCDIV_SIRCDIV2(1);/*!* Change to normal RUN mode with 8MHz SOSC, 80 MHz PLL:* ====================================================*/SCG->RCCR=SCG_RCCR_SCS(6) /* Select PLL as clock source */|SCG_RCCR_DIVCORE(0b01) /* DIVCORE=1, div. by 2: Core clock = 160/2 MHz = 80 MHz */|SCG_RCCR_DIVBUS(0b01) /* DIVBUS=1, div. by 2: bus clock = 40 MHz */|SCG_RCCR_DIVSLOW(0b10); /* DIVSLOW=2, div. by 2: SCG slow, flash clock= 26 2/3 MHz */while (((SCG->CSR & SCG_CSR_SCS_MASK) >> SCG_CSR_SCS_SHIFT ) != 6) {} /* Wait for sys clk src = SPLL */

}