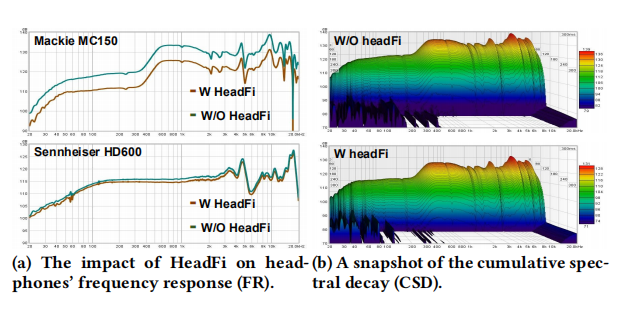

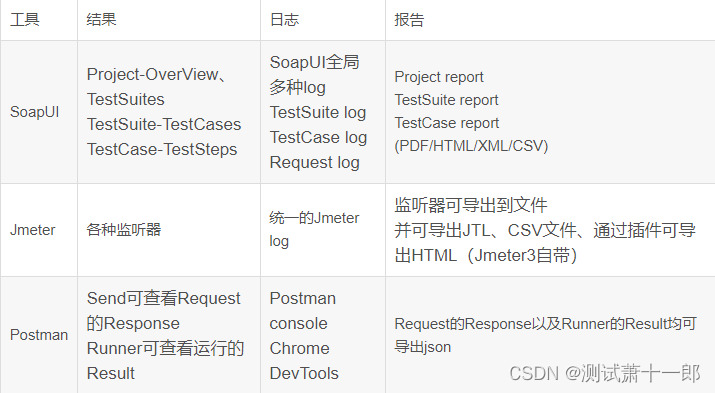

1.时钟架构

简化一下如图所示:

1.1.时钟源的选择

S3C2440的时钟源来源有两种:

- 外部晶振(OSC)

- 外部时钟信号(EXTCLK)

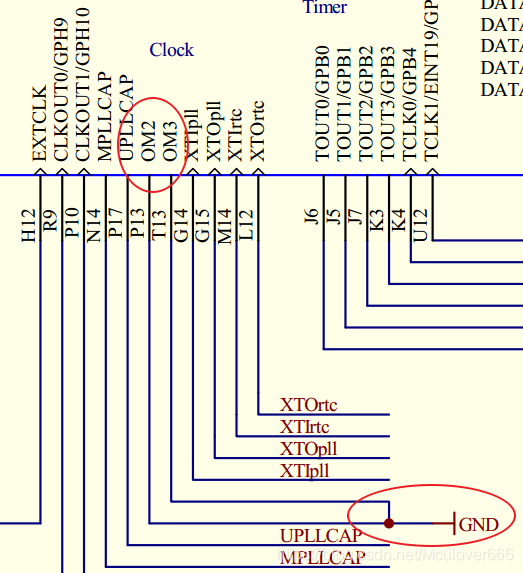

选择哪一路作为S3C2440的时钟源由模式控制引脚OM3和OM2引脚(的电平)决定,如何选择见下图:

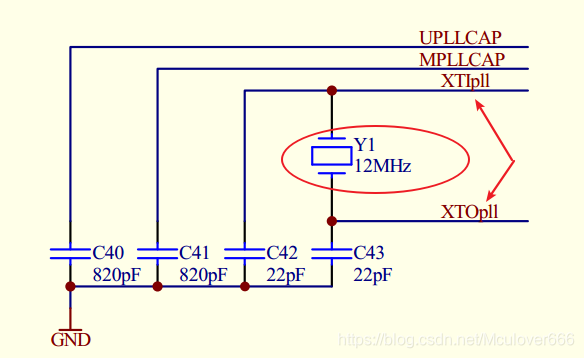

以JZ2440开发板为例,其使用的是12Mhz外部晶振, 硬件电路如下:

其OM3和OM2选择引脚设置如下,选择第一种方式:

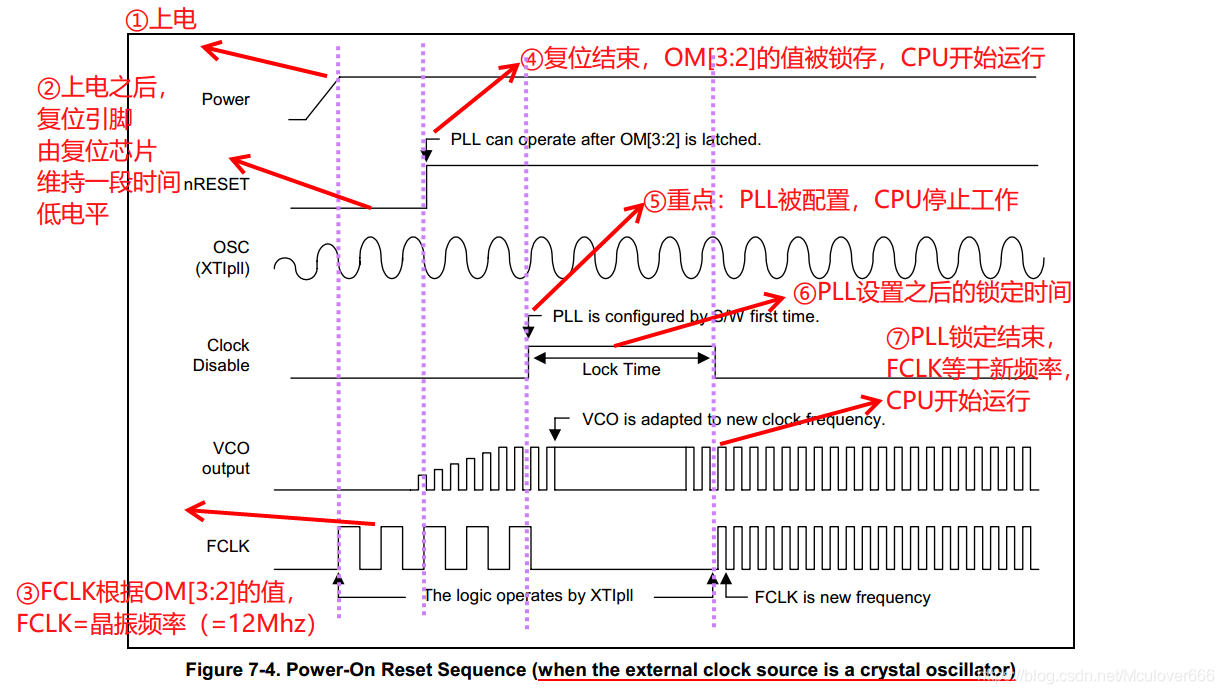

1.2.MPLL改变主时钟FCLK的控制时序(上电复位时序)

2.实验 —— LED闪烁(为了后续对比)

2.1.实验目的

使用C语言控制LED闪烁。

2.2.实验代码

启动文件与之前相同;

C程序添加延时函数delay修改后如下:

void delay(unsigned int xms)

{while(xms--);

}int main(void)

{/* 设置GPFCON寄存器,配置GPF4引脚为输出模式 */*(unsigned int *)0x56000050 &= ~(3<<(2*4));*(unsigned int *)0x56000050 |= 1<<(2*4);/* 程序循环闪烁LED */while(1){/* 设置GPFDAT寄存器,GPF4输出低电平,点亮LED */*(unsigned int *)0x56000054 &= ~(1<<4);delay(100000);/* 设置GPFDAT寄存器,GPF4输出高电平,熄灭LED */*(unsigned int *)0x56000054 |= (1<<4);delay(100000);}

}

编译的makefile也和之前相同;

2.3.运行结果

第一个LED先亮起,1s后熄灭,1s后再次点亮,如此循环。

3.实验 —— 设置芯片时钟运行频率

3.1.实验目的

设置芯片的时钟工作频率最高,如下:

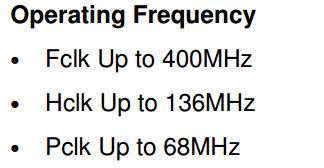

- FCLK = 400Mhz

- HCLK = 100Mhz

- PCLK = 50Mhz

与实验2对比观察效果。

注:芯片手册中给出的最高时钟频率:

3.2.实验步骤

- 设置PLL更改之后的锁定时间(默认即可)

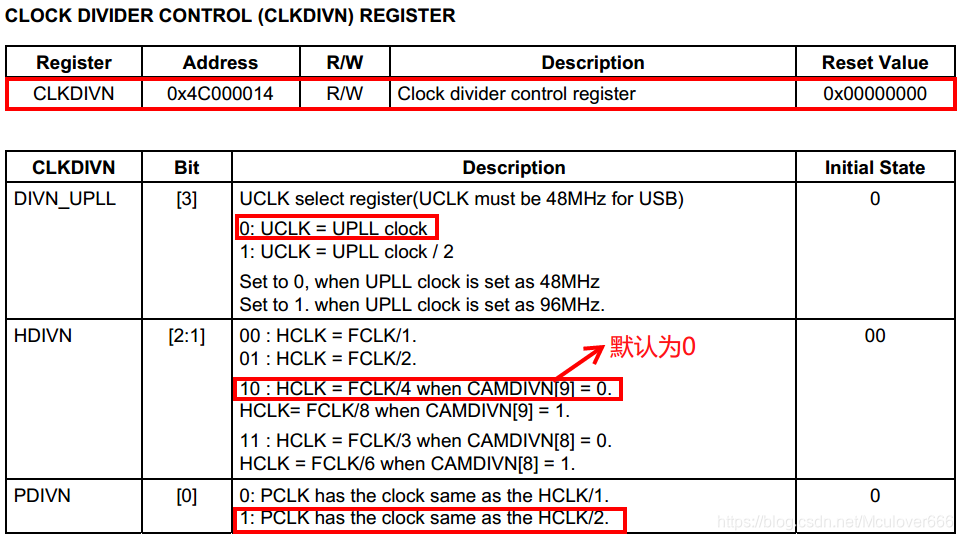

- 设置分频系数(UCLK=UPLL(默认值)、HCLK = FCLK/4(100M)、PCLK=HCLK/2(50M))

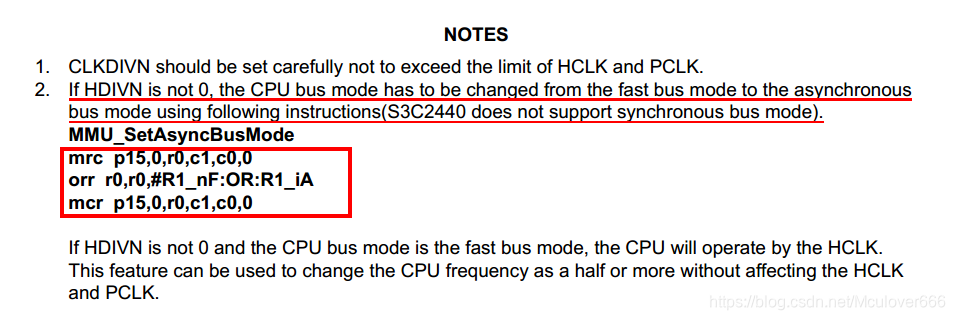

- HDIVN不为0,设置CPU为异步模式

注:其中#R1_nF:OR:R1_iA的值为0xc0000000。

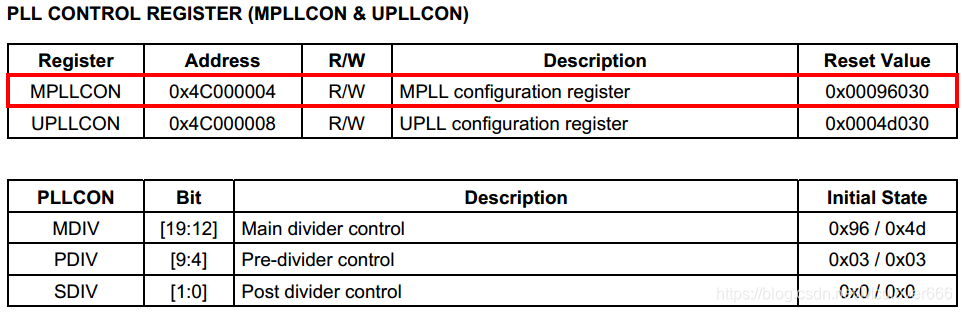

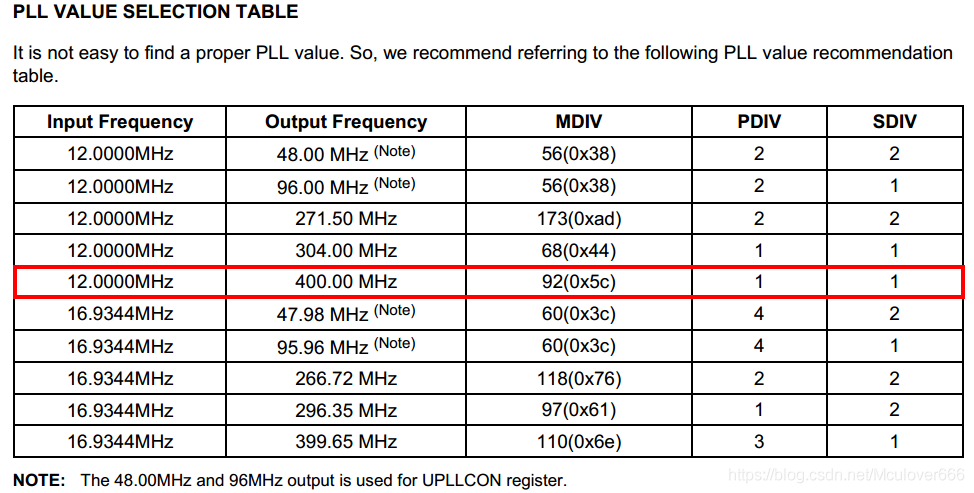

- 设置MPLL倍频,产生FCLK=400Mhz:

注:MPLLCON寄存器的值可以由公式自己推算,但芯片手册中推荐直接查找推荐表获得:

3.3.实验代码

时钟修改应该在上电后修改,所以在启动文件中关闭看门狗之后添加:

@ brief: S3C2440启动文件

@ author: mculover666

@ note:

@ 1.关闭看门狗

@ 2.设置栈顶指针SP(从Nand启动)

@ 3.设置时钟:FCLK=400Mhz,HCLK=100Mhz,PCLK=50Mhz

@ 4.调用main函数,保存返回地址,转入C程序.text

.global _start_start:@ 关闭看门狗LDR R0,=0x53000000MOV R1,#0STR R1,[R0]@ 设置栈顶指针SP(从Nand启动)LDR SP,=4096@ 设置时钟:FCLK=400Mhz,HCLK=100Mhz,PCLK=50Mhz@ 设置PLL更改之后的锁定时间(默认值)LDR R0,=0x4c000000LDR R1,=0xFFFFFFFFSTR R1,[R0]@ 设置分频系数LDR R0,=0x4c000014LDR R1,=0x05STR R1,[R0]@ HDIVN不为0,设置CPU为异步模式(来源芯片手册)mrc p15,0,r0,c1,c0,0orr r0,r0,#0xc0000000 @#R1_nF:OR:R1_iAmcr p15,0,r0,c1,c0,0@ 设置MPLL,输出FCLK=400MhzLDR R0,=0x4c000004LDR R1,=(92<<12)|(1<<4)|(1<<0)STR R1,[R0] @ 设置MPLL之后锁定一段时间,然后系统变为设置的频率@ 调用main函数,保存返回地址,转入C程序BL main@ main函数返回,程序暂停

halt:B halt为了方便对比**,C程序与实验2的相同**;

编译的makefile和之前的也相同;

3.4.实验结果

程序编译下载后,可以观察到,LED闪烁速度与之前相比快了非常多。

3.5.实验总结

通过本节的两个实验,

- 从直观的的现象来看:同样的C语言程序(都是

delay(100000)),但是在第二个实验中因为CPU时钟FCLK提高到最高运行频率400Mhz,所以LED的闪烁速度与之前相比快了好几倍; - 深入到S3C2440芯片的结构:掌握了S3C2440的时钟体系架构和上电复位时序,其时钟源有两个:外部晶振或者外部时钟,通过

OM[3:2]硬件选择,其内部主要调整频率的PLL有两个:MPLL(产生FCLK)和UPLL(产生UCLK),其主要的时钟频率有三个(FCLK->CPU使用,HCLK->AHB总线高速外设使用,PCLK->APB总线低速外设使用),其中HCLK和PCLK由FCLK分频而来; - 在芯片操作上:掌握了如何编程设置寄存器控制S3C2440的时钟频率(比如本节设置FCLK=400Mhz,HCLK=100Mhz,PCLK=50Mhz)。