超前进位加法器

描述

题目描述:

求两个四位的数据编写一个四位的超前进位加法器,建议使用子模块

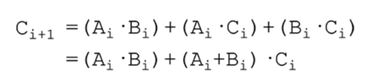

提示:超前进位加法器的位公式如下

这里‘+’ ‘·’符号不是‘加’和‘乘’,是‘或’和 ‘与’

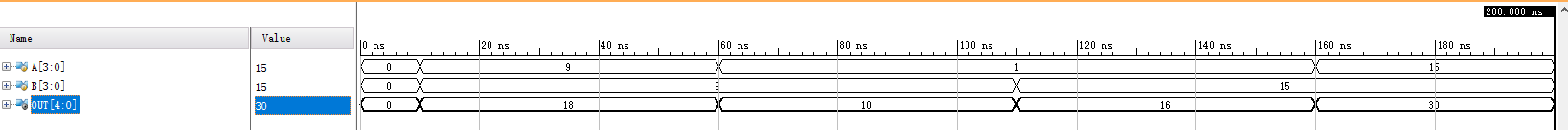

波形示意图:

输入描述:

A B 输入值

输出描述:

OUT 加法结果

解题思路

超前进位加法器详解

可参考博文:

行波进位/超前进位加法器详解

【Verilog学习日常】—牛客网刷题—Verilog快速入门—VL12

根据本题中的描述,可画出超前进位加法器电路设计图:

子模块详解

子模块Add1——1bit全加器

在子模块Add1中:

输入信号为1bit的a,b,C_in;其中,a、b为单比特输入信号,C_in为进位信号;

输出信号分别为1bit的f,g,p;其中,f为输出信号,可表示为。g、p表示中间变量;其中

;(由进位公式

得出)

因此,子模块的代码为:

module Add1

(input a,input b,input C_in,output f,output g,output p);assign g = a & b;assign p = a | b;assign f = a ^ b ^ C_in;endmodule当仅考虑子模块Add1的添加时(即将进位信号C的公式全都直接在主函数中进行表示)

`timescale 1ns/1nsmodule huawei8//四位超前进位加法器

(input wire [3:0]A,input wire [3:0]B,output wire [4:0]OUT

);//*************code***********//

wire [3:0] P,G; //设置中间变量

wire [3:0] C; //设置进位变量

assign C[0] = 1'b0;

assign C[1] = A[0]&B[0];

assign C[2] = A[1]&B[1] | (A[1]|B[1])&C[1];

assign C[3] = A[2]&B[2] | (A[2]|B[2])&C[2];Add1 A1 (.a(A[0]), .b(B[0]), .C_in(C[0]), .f(OUT[0]), .g(G[0]), .p(P[0]));

Add1 A2 (.a(A[1]), .b(B[1]), .C_in(C[1]), .f(OUT[1]), .g(G[1]), .p(P[1]));

Add1 A3 (.a(A[2]), .b(B[2]), .C_in(C[2]), .f(OUT[2]), .g(G[2]), .p(P[2]));

Add1 A4 (.a(A[3]), .b(B[3]), .C_in(C[3]), .f(OUT[3]), .g(G[3]), .p(P[3]));assign OUT[4] = A[3]&B[3] | (A[3]|B[3])&C[3];//*************code***********//

endmodule//下面是两个子模块module Add1

(input a,input b,input C_in,output f,output g,output p);assign g = a & b;assign p = a ^ b;assign f = p ^ C_in;endmodule子模块CLA_4

子模块CLA_4主要描述进位Ci的情况;

根据题中给出的公式:

可得中间变量

问题:变量Gm、Pm的定义是??

代码如下:

module CLA_4(input [3:0]P,input [3:0]G,input C_in,output [4:1]Ci,output Gm,output Pm);assign Ci[1] = C_in & P[0] | G[0];assign Ci[2] = Ci[1] & P[1] | G[1];assign Ci[3] = Ci[2] & P[2] | G[2];assign Ci[4] = Ci[3] & P[3] | G[3];assign Gm = 1'b0;assign Pm = 1'b0;

endmodule完整代码

`timescale 1ns/1nsmodule huawei8//四位超前进位加法器

(input wire [3:0]A,input wire [3:0]B,output wire [4:0]OUT

);//*************code***********//

wire [3:0] P,G; //设置中间变量

wire [4:1] C; //设置进位变量Add1 A1 (.a(A[0]), .b(B[0]), .C_in(1'b0), .f(OUT[0]), .g(G[0]), .p(P[0]));

Add1 A2 (.a(A[1]), .b(B[1]), .C_in(C[1]), .f(OUT[1]), .g(G[1]), .p(P[1]));

Add1 A3 (.a(A[2]), .b(B[2]), .C_in(C[2]), .f(OUT[2]), .g(G[2]), .p(P[2]));

Add1 A4 (.a(A[3]), .b(B[3]), .C_in(C[3]), .f(OUT[3]), .g(G[3]), .p(P[3]));CLA_4 cla (.P(P), .G(G), .C_in(1'b0), .Ci(C), .Gm(), .Pm());assign OUT[4] = C[4];//*************code***********//

endmodule//下面是两个子模块module Add1

(input a,input b,input C_in,output f,output g,output p);assign g = a & b;assign p = a | b;assign f = a ^ b ^ C_in;endmodulemodule CLA_4(input [3:0]P,input [3:0]G,input C_in,output [4:1]Ci,output Gm,output Pm);assign Ci[1] = C_in & P[0] | G[0];assign Ci[2] = Ci[1] & P[1] | G[1];assign Ci[3] = Ci[2] & P[2] | G[2];assign Ci[4] = Ci[3] & P[3] | G[3];assign Gm = 1'b0;assign Pm = 1'b0;

endmodule