ic

2024/9/24 7:26:15芯片数字后端设计入门书单推荐(可下载)

数字后端设计,作为数字集成电路设计的关键环节,承担着将逻辑设计转化为物理实现的重任。它不仅要求设计师具备深厚的电路理论知识,还需要对EDA工具有深入的理解和熟练的操作技能。尽管数字后端工作不像前端设计那样频繁涉及代码编写ÿ…

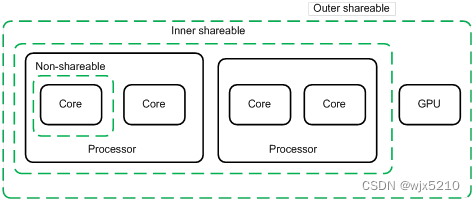

armv8 memory model概述

概述

在armv8 架构中,它引入了更多的维度来描述内存模型,从而在此基础上进行硬件优化(但其中一些并未被主流的软件所接受),在此做一些简单的整理,更多信息请参考 Arm spec 以及 AMBA 协议。下文主要是对Memory 和 Device 两大类的…

24届数字IC验证——SV+UVM基础知识汇总(九)

文章目录 前言57、module和program区别58、仿真调度区域59、fork-join、fork-join_none和fork-join_any的区别(经常问)60、D触发器输入高阻,输出是什么61、recovery time和removal time62、设置仿真退出时间62、$ time和$ realtime区别63、选择验证的原因(常问)64、验证工…

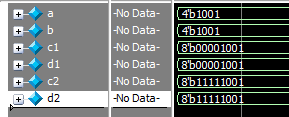

基于FPGA的数字信号处理(11)--定点数的舍入模式(2)向最临近值取整nearest

前言

在之前的文章介绍了定点数为什么需要舍入和几种常见的舍入模式。今天我们再来看看另外一种舍入模式:向最临近值取整nearest。

10进制数的nearest

nearest: 向最临近值方向取整。它的舍入方式和四舍五入非常类似,都是舍入到最近的整数…

【ARM】v8架构programmer guide(4)_ARMv8的寄存器

目录 4.4Endianness(端序或字节序)

4.5 改变execution state

4.5.1 Registers at AArch32

4.5.2 PSTATE at AArch32

4.6 NEON 和浮点数寄存器

4.6.1 AArch64中浮点寄存器的组织结构

4.6.2 标量寄存器大小

4.6.3 向量寄存器大小

4.6.4 NEON在AArc…

逻辑这回事(一)----编码规范

说明:优先级是M的规则为强制项,优先级为R的规则为建议项。

通用约束

应有全局观念。

优先级:M

说明:你所编写的代码在成为最终硅片上的一部分之前,需要经过许多设计者利用各种各样的工具进行各种各样的处理。有时&…

基于FPGA的数字信号处理(6)--如何确定Verilog表达式的符号

前言

尽管signed语法的使用能带来很多便利,但同时也给表达式的符号确定带来了更多的不确定性。比如一个有符号数和一个无符号数的加法/乘法结果是有符号数还是无符号数?一个有符号数和一个无符号数的比较结果是有符号数还是无符号数?等等。接…

《基于FPGA的数字信号处理》专栏的导航与说明

Part 1 定点数与浮点数 基于FPGA的数字信号处理(1)--什么是无符号数?什么是有符号数? 基于FPGA的数字信号处理(2)--什么是定点数? 基于FPGA的数字信号处理(3)--什么是浮…

(55)MOS管专题--->(10)MOS管的封装

(10)MOS管的封装

1 目录

(a)IC简介

(b)数字IC设计流程

(c)Verilog简介

(d)MOS管的封装

(e)结束

1 IC简介

(a)在IC设计中,设计师使用电路设计工具(如EDA软件)来设计和模拟各种电路,例如逻辑电路、模拟电路、数字信号处理电路等。然后,根据设计电路的…

【ARM】v8架构programmer guide(5)_ARMv8指令集介绍

目录

5.1 ARMv8 指令集

5.1.1 32bit和64bit A64指令的重大区别

5.1.2 地址

5.1.3 寄存器

5.2 不同指令集直接的切换 ARMv8架构中最显著的变化之一是引入了64位指令集。这个指令集补充了现有的32位指令集架构。这一增加使得处理器可以访问64位宽的整数寄存器和数据操作&…

【ARM】v8架构programmer guide(5)_ARMv8指令集介绍

目录

5.1 ARMv8 指令集

5.1.1 32bit和64bit A64指令的重大区别

5.1.2 地址

5.1.3 寄存器

5.2 不同指令集直接的切换 ARMv8架构中最显著的变化之一是引入了64位指令集。这个指令集补充了现有的32位指令集架构。这一增加使得处理器可以访问64位宽的整数寄存器和数据操作&…

【IC前端虚拟项目】测试点思路和文档编写

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 好,又到了测试点文档了这一部分了,我经常跟带着学习的童鞋说,对于芯片验证人来说测试点文档就是最重要的一个交付文件,也是在项目交付中最为看重的进度衡量…

【24届数字IC秋招总结】正式批面试经验汇总6——禾赛

文章目录 一、禾赛-数字IC验证工程师1.1 一面面试问题1.2 二面面试问题一、禾赛-数字IC验证工程师

面试时间:9.19 9.25

1.1 一面面试问题

1、自我介绍 2、研究生课题 3、build_phase从上至下还是从下至上 4、哪些phase是task phase 5、perl脚本做了什么 6、整个验证环境是怎…

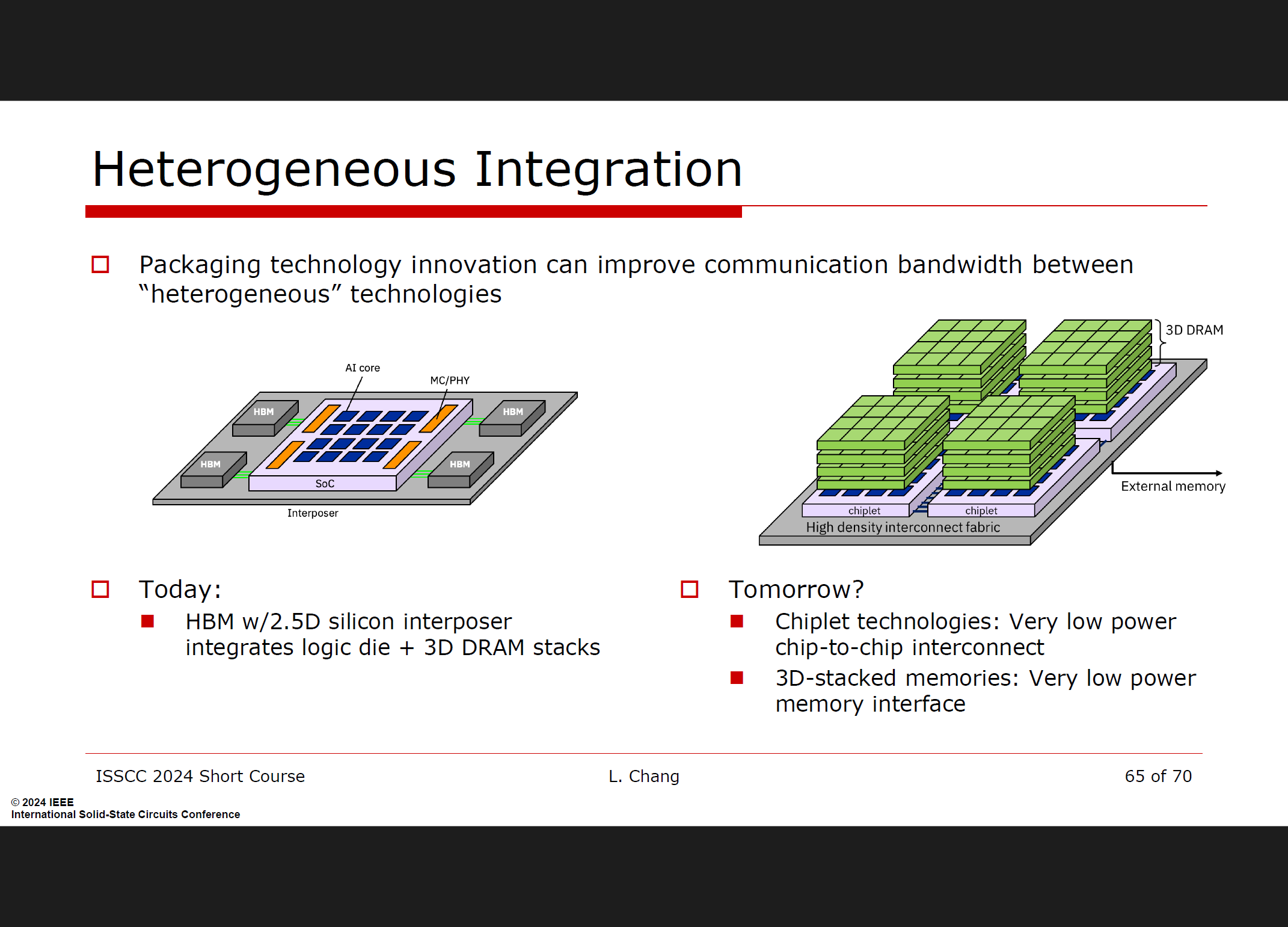

isscc2024 short course2 Performance Compute Environment

这部分分为4部分: 概览:LLMs和生成式AI

探讨大语言模型(LLMs)和生成式AI的整体环境,及其对硬件加速器设计的影响。 高性能AI加速器的特定考虑因素

广泛的模型和使用案例支持:需要设计能支持多种模型和应…

芯片验证 | UVM的objection机制

了解完phase机制后,发现这不了解objection极其不合适,于是好吧好吧,再学习一点。 以下内容全部来自白皮书。 1 objection与task phase

objection字面的意思就是反对、异议。在验证平台中,可以通过drop_objection来通知系统可以关…

PT通过size vt修时序脚本

常用到mmmc的情况下通过synopsys的prime time的multisceanrio 模式提高fix 效率

以下内容仅供学习参考

##start job:dsubjob pt_shell -multi_scenario -f setup_size_vt.tcl

set date [exec date %m%d%H%M]

set work_path setup_fixvt_${date}

sh rm -rf ./$work/*

set_hos…