定点数

2024/9/23 3:29:26基于FPGA的数字信号处理(4)--浮点数的定点化

写在前面

首先要说明的是,题目《浮点数的定点化》中所谓的 浮点数 并不是指 IEEE754 规定的 单精度浮点数 或者 双精度浮点数 等格式,而是指10进制小数。所以说白了,这篇文章要讲的就是如何将10进制小数采用定点数的形式表示。 为什么2进制无…

基于FPGA的数字信号处理(4)--浮点数的定点化

写在前面

首先要说明的是,题目《浮点数的定点化》中所谓的 浮点数 并不是指 IEEE754 规定的 单精度浮点数 或者 双精度浮点数 等格式,而是指10进制小数。所以说白了,这篇文章要讲的就是如何将10进制小数采用定点数的形式表示。 为什么2进制无…

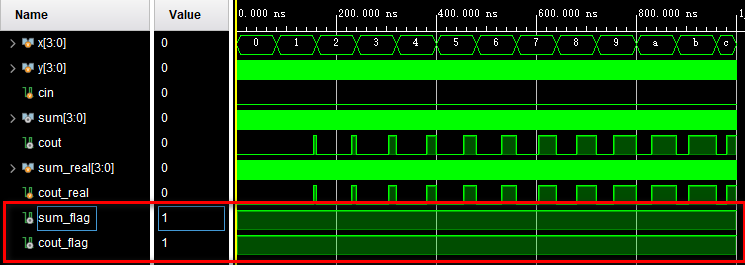

基于FPGA的数字信号处理(21)--超前进位加法器(Carry Lookahead Adder,CLA)

目录

1、什么是超前进位加法器

2、CLA加法器的关键路径

3、CLA加法器的Verilog实现

4、CLA加法器的时序性能

5、总结 文章总目录点这里:《基于FPGA的数字信号处理》专栏的导航与说明 1、什么是超前进位加法器 在之前的文章,我们介绍了行波进位加法器…

基于FPGA的数字信号处理(21)--超前进位加法器(Carry Lookahead Adder,CLA)

目录

1、什么是超前进位加法器

2、CLA加法器的关键路径

3、CLA加法器的Verilog实现

4、CLA加法器的时序性能

5、总结 文章总目录点这里:《基于FPGA的数字信号处理》专栏的导航与说明 1、什么是超前进位加法器 在之前的文章,我们介绍了行波进位加法器…

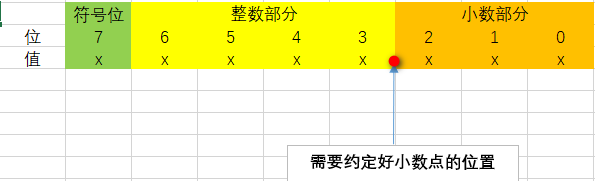

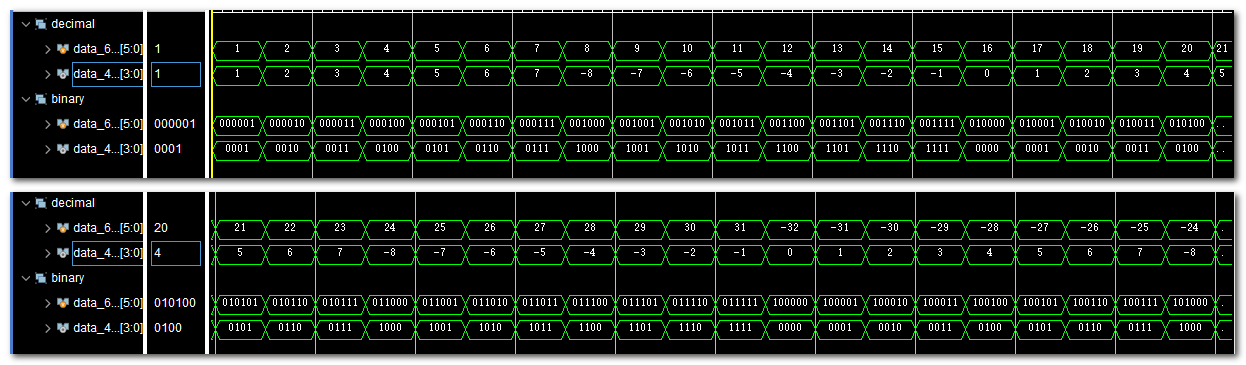

基于FPGA的数字信号处理(2)--什么是定点数?

在实际的工程应用中,往往会进行大量的数学运算。运算时除了会用到整数,很多时候也会用到小数。而我们知道在数字电路底层,只有「高电平1」和「低电平0」的存在,那么仅凭 0和1 该如何表示小数呢?

数字电路中࿰…

基于FPGA的数字信号处理(2)--什么是定点数?

在实际的工程应用中,往往会进行大量的数学运算。运算时除了会用到整数,很多时候也会用到小数。而我们知道在数字电路底层,只有「高电平1」和「低电平0」的存在,那么仅凭 0和1 该如何表示小数呢?

数字电路中࿰…

基于FPGA的数字信号处理(21)--超前进位加法器(Carry Lookahead Adder,CLA)

目录

1、什么是超前进位加法器

2、CLA加法器的关键路径

3、CLA加法器的Verilog实现

4、CLA加法器的时序性能

5、总结 文章总目录点这里:《基于FPGA的数字信号处理》专栏的导航与说明 1、什么是超前进位加法器 在之前的文章,我们介绍了行波进位加法器…

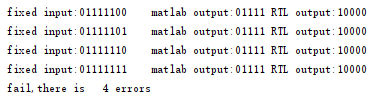

基于FPGA的数字信号处理(10)--定点数的舍入模式(1)四舍五入round

1、前言

将浮点数定量化为定点数时,有一个避不开的问题:某些小数是无法用有限个数的2进制数来表示的。比如: 0.5(D) 0.1(B) 0.1(D) 0.0001100110011001~~~~(B) 可以看到0.5是可以精准表示的,但是0.1却不行。原因是整数是离散的…

基于FPGA的数字信号处理(9)--定点数据的两种溢出处理模式:饱和(Saturate)和绕回(Wrap)

1、前言

在逻辑设计中,为了保证运算结果的正确性,常常需要对结果的位宽进行扩展。比如2个3bits的无符号数相加,只有将结果设定为4bits,才能保证结果一定是正确的。不然,某些情况如77 14(1110),如果结果只…

基于FPGA的数字信号处理(4)--浮点数的定点化

写在前面

首先要说明的是,题目《浮点数的定点化》中所谓的 浮点数 并不是指 IEEE754 规定的 单精度浮点数 或者 双精度浮点数 等格式,而是指10进制小数。所以说白了,这篇文章要讲的就是如何将10进制小数采用定点数的形式表示。 为什么2进制无…

基于FPGA的数字信号处理(4)--浮点数的定点化

写在前面

首先要说明的是,题目《浮点数的定点化》中所谓的 浮点数 并不是指 IEEE754 规定的 单精度浮点数 或者 双精度浮点数 等格式,而是指10进制小数。所以说白了,这篇文章要讲的就是如何将10进制小数采用定点数的形式表示。 为什么2进制无…

基于FPGA的数字信号处理(4)--浮点数的定点化

写在前面

首先要说明的是,题目《浮点数的定点化》中所谓的 浮点数 并不是指 IEEE754 规定的 单精度浮点数 或者 双精度浮点数 等格式,而是指10进制小数。所以说白了,这篇文章要讲的就是如何将10进制小数采用定点数的形式表示。 为什么2进制无…