Chisel

2024/9/24 1:26:39Chisel中对对<: 和:的理解(其实是Scala中的理解)

在 Scala 语言和 Chisel 硬件构造语言中,<: 和 : 是用于类型注解的两个不同的符号,它们在泛型编程和类型系统中扮演重要角色。下面是它们各自的意义和用途:

<:(子类型关系)

<: 符号在 Scala 中表示子类型关…

【数字集成电路与系统设计】基本的组合逻辑电路

目录 一、简单例子引入

1.1 端口声明

1.1.2 Verilog实现

1.1.3 Chisel实现

逐行解释

1.2 内部逻辑实现

1.2.1 Verilog实现

1.2.2 Chisel实现

Chisel 关键点解释

1.3 常用的硬件原语

二、Chisel主要数据类型介绍

2.1 数据类型

2.2 数据宽度

2.3 数据转换

2.4 运算…

【数字集成电路与系统设计】基本的组合逻辑电路

目录 一、简单例子引入

1.1 端口声明

1.1.2 Verilog实现

1.1.3 Chisel实现

逐行解释

1.2 内部逻辑实现

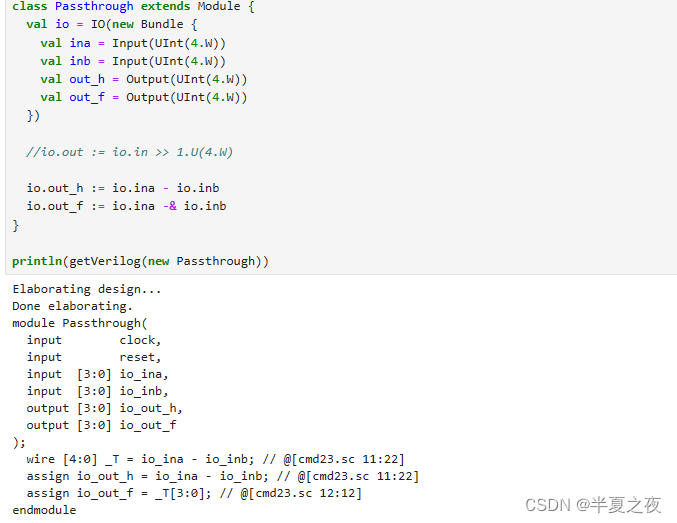

1.2.1 Verilog实现

1.2.2 Chisel实现

Chisel 关键点解释

1.3 常用的硬件原语

二、Chisel主要数据类型介绍

2.1 数据类型

2.2 数据宽度

2.3 数据转换

2.4 运算…

【Chisel】chisel中怎么处理类似verilog的可变位宽和parameter

在 Chisel 中处理可变位宽和参数的方式与 Verilog 有一些不同,因为 Chisel 是建立在 Scala 语言之上的。以下是如何在 Chisel 中处理这些概念的方法:

参数化(Parameters) 在 Chisel 中,参数化是通过在模块构造函数中定…

Chisel3 入门 (1)

Chisel3 入门(1) 文章目录 Chisel3 入门(1)Chisel3 基本数据类型定义变量创建变量、常量 布尔逻辑类型转换Analog/BlackBox 类型 Chisel3 基本数据类型

chisel提供三种类型数据类型描述信号连接、组合逻辑、寄存器:

Bits: 可表示 一个bit 向量UInt: 扩展自Bits, 表…

【数字集成电路与系统设计】Chisel/Scala简介与Verilog介绍

目录 一、芯片前端设计开发背景知识

二、Verilog介绍

2.1 硬件设计一些重要概念

2.2 功能性仿真

2.3 简单的Verilog代码例子(4-bit的加法器)

三、Chisel简介

3.1 Chisel基本概念

3.2 Chisel代码展示

3.3 Chisel转成Verilog代码

四、Scala入…

Chisel 入门(2)运算符

Chisel 入门(2) 运算符

逻辑运算符

ChiselExplanationwidth!x逻辑非1x && y逻辑与1x||y逻辑或1

位操作运算符

ChiselExplanationwidthin Verilog~x位反w(x)~ signal_xx & y位与max(w(x), w(y))signal_x & signal_yx | y位或max(w(x), w(y))signal_x | sign…

在Chisel3中,不支持对子字(subword)进行赋值。在 Chisel 中,UInt 类型是一个不可变的位宽数据类型,它表示一个固定位宽的无符号整数。

在Chisel3中,不支持对子字(subword)进行赋值。这种设计决策背后的原因涉及到硬件描述语言中类型和数据抽象的最佳实践。

不支持子字赋值的原因 硬件描述的性质: 在硬件设计中,操作和修改单独的位或子字通常与较高的复…

Chisel 入门(2)运算符

Chisel 入门(2) 运算符

逻辑运算符

ChiselExplanationwidth!x逻辑非1x && y逻辑与1x||y逻辑或1

位操作运算符

ChiselExplanationwidthin Verilog~x位反w(x)~ signal_xx & y位与max(w(x), w(y))signal_x & signal_yx | y位或max(w(x), w(y))signal_x | sign…