数字电路之于FPGA意义重大。本“可预置倒计时器”设计采用施密特触发器40106作为振荡电路,由同步十进制可逆计数器74LSl92、译码器74LS47D和七段共阳数码管构成计时电路,具有启动/预置、暂停/继续计时和报警功能。紫色文字是超链接,点击自动跳转至相关博文。持续更新,原创不易!

目录:

一、简介

二、电路组成

1、秒脉冲发生器

2、计数器

3、译码及显示电路

4、控制电路

5、电路的变体

三、元件功能

四、掌握数字电路的意义

前置知识:卡诺图与逻辑代数化简法、数字电路-时序逻辑电路。

一、电路简介

本设计采用施密特触发器40106作为振荡电路,由同步十进制可逆计数器74LSl92、译码器74LS47D和七段共阳数码管构成计时电路,具有启动/预置、暂停/继续计时和报警功能。电路框图:

Microsoft Visio绘制

二、电路组成

电路由秒脉冲发生器、计数器、译码器、显示电路、声光报警电路、控制电路共6个部分组成。其部分电路如下图所示,仿真原文件下载移步:可预置倒计时器Multisim仿真。

1、秒脉冲发生器

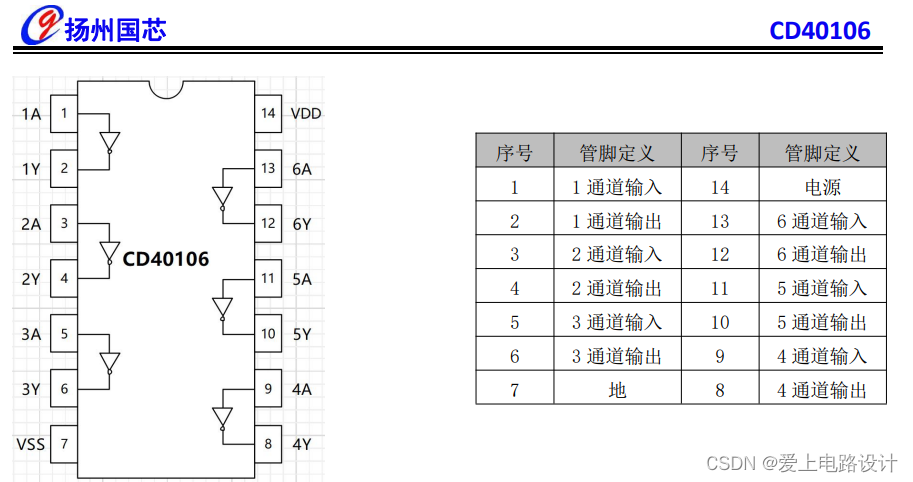

秒脉冲发生器由40106和外接元件R1、C1构成多谐振荡器。输出脉冲的频率f ≈ 1Hz即1秒。

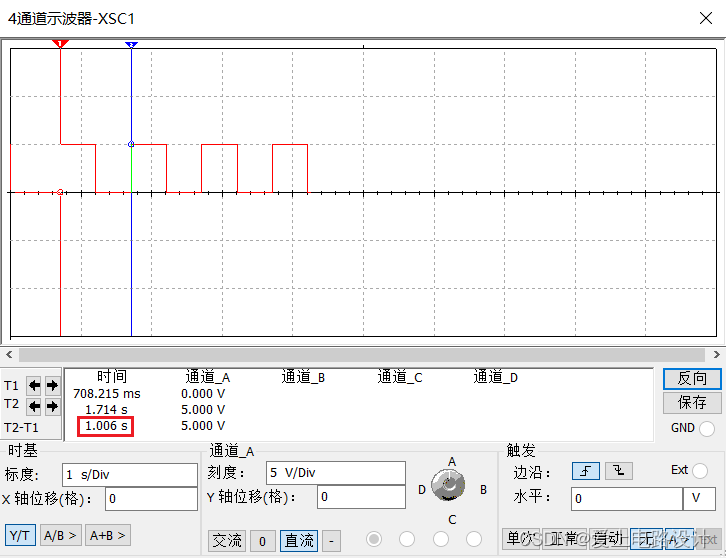

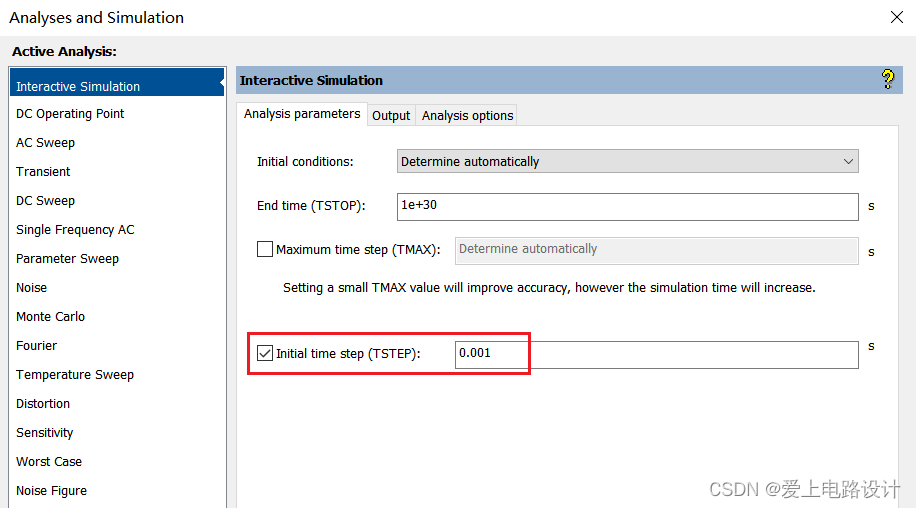

仿真设置如下图,否则振荡器不工作。

2、计数器

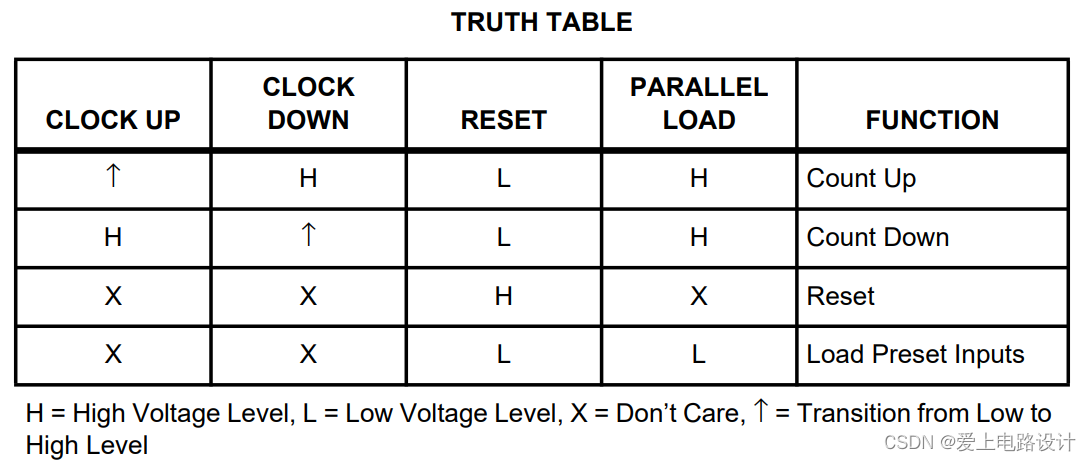

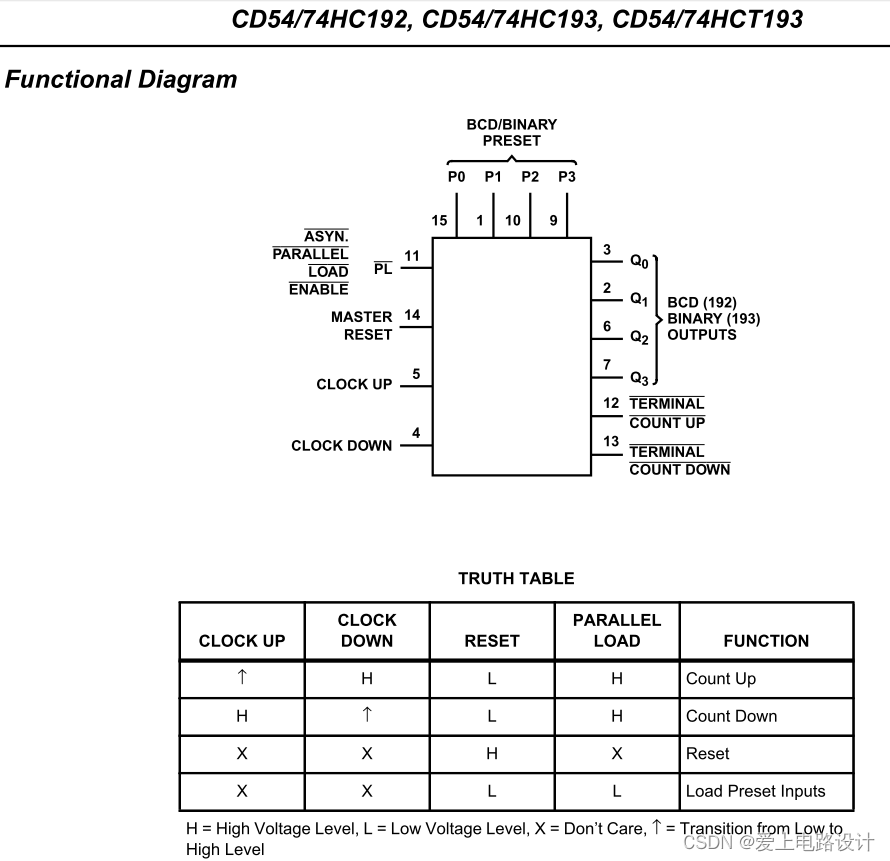

1)计数器由两片74LS192同步十进制可逆计数器构成,真值表如下图所示。

2)利用减计数PARALLEL LOAD = 1,RESET = 0,CLOCK DOWN = 1,实现计数器按8421码递减进行减计数。并且利用借位输出端BO与下一级的CLOCK DOWN连接,实现计数器之间的级联。

3)利用预置数PARALLEL LOAD端实现异步置数。

当RESET = 0,且PARALLEL LOAD = 0时,不管CLOCK UP和CLOCK DOWN时钟输入端的状态如何,将使计数器的输出等于并行输入数据,即Q3Q2Q1Q0 = D3D2D1D0。

3、译码及显示电路

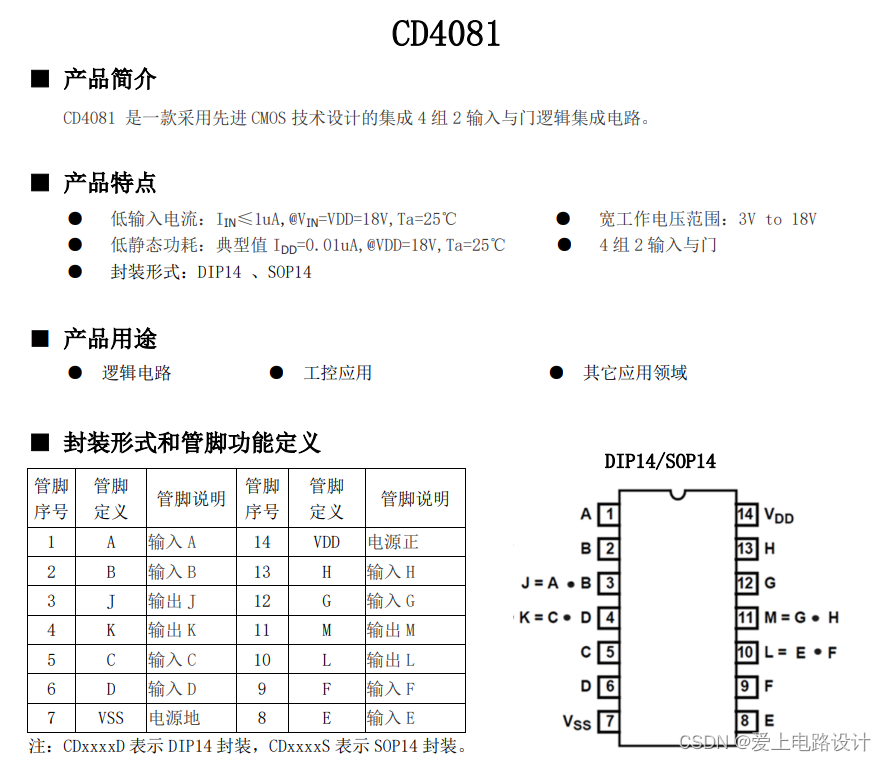

本电路由译码驱动器74LS47D和七段共阳数码管组成,74LS47D集电极开路输出,输出低电平有效。也可以使用74LS48D,二者功能差异如下表。

| 74LS47D | 只提供解码和驱动功能,没有锁存器功能,仅能显示0-9的数字。 |

| 74LS48D | 集成译码器和锁存器功能,能够直接驱动七段数码管并显示0-9的数字以及特殊字符(如A-F) |

4、控制电路

完成倒计时器的开始/预置计时、暂停/继续计时、声光报警等功能。控制电路由U9组成。

1)S1:时间设置拨码开关,99秒内均可预先设置。

2)S2:启动/预置按键。

(1)按动S2,倒计时开始。当计时器递减到0时,控制电路发出声光报警,计时器恢复到预置状态。

(2)当计时器未递减到0时,按动S2,计时器恢复到预置状态。

3)S3:暂停/继续按键。按动S3计时器暂停计时,显示器保持不变;当再次按动S3,计时器继续累计计时。

5、电路的变体

也可以将74LS47D更改为4511,此时数码管更改为七段共阴数码管,部分电路如下图所示。

三、元件功能

四、掌握数字电路的意义

学习数字电路对于理解和掌握FPGA(Field Programmable Gate Array现场可编程门阵列)设计至关重要。

| 基础理解 | 数字电路是构成FPGA设计的基础。用于了解逻辑门、触发器、译码器等基础元件的工作原理,这些元件在FPGA中以可编程逻辑单元的形式实现。 |

| 设计思路 | 数字电路设计培养了一种系统化的思维方式,对于设计FPGA电路非常有用。 |

| 时序分析 | 对数字电路时序的深入理解将帮助你优化FPGA设计,避免时序违规。 |

| 硬件描述语言 | 数字电路的知识将使你能够更有效地编写和理解解硬件描述语言。 |

| 故障排除和调试 | 在调试FPGA设计时将能够更快地识别和解决问题。 |

应用场景列举:比如伺服驱动器,有关内容移步:高创伺服驱动器故障维修(8.闪烁)。

世上无难事,只要肯登攀。觉得不错,动动发财的小手点个赞哦!