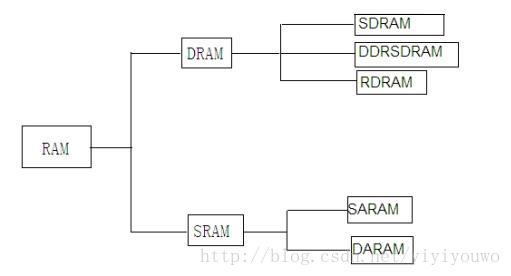

SRAM,DRAM,SDRAM的区别

- SRAM

SRAM,静态的随机存取存储器,又被称为静态RAM,利用双稳态电路进行存储。即使有干扰对稳态电路也没影响,所以有双稳态性,“静态”是指只要不掉电,存储在SRAM中的数据就可以一直保存,只要有电,SRAM中的数据就不会有变化。加电情况下,不需要一直刷新,数据不会丢失。 - DRAM

DRAM,动态随机存取存储器,需要不断的刷新,才能保存数据。主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。由于在现实中电容会有漏电的现象,导致电位差不足而使记忆消失,因此除非电容经常周期性地充电,否则无法确保记忆长存。DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。这一操作称为预充电,是行上的最后一项操作。必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。 - SDRAM

同步动态随机存储器。同步的DRAM

同步和异步的区别是同步方式需要一个专门的片外时钟CLK信号引脚,所有的读写操作都是跟着这个时钟信号走的

SRAM :静态RAM,不用刷新,速度可以非常快,像CPU内部的cache,都是静态RAM,缺点是一个内存单元需要的晶体管数量多,因而价格昂贵,容量不大。

DRAM:动态RAM,需要刷新,容量大。

SDRAM:同步动态RAM,需要刷新,速度较快,容量大。

DDR SDRAM:双通道同步动态RAM,需要刷新,速度快,容量大。

SDRAM

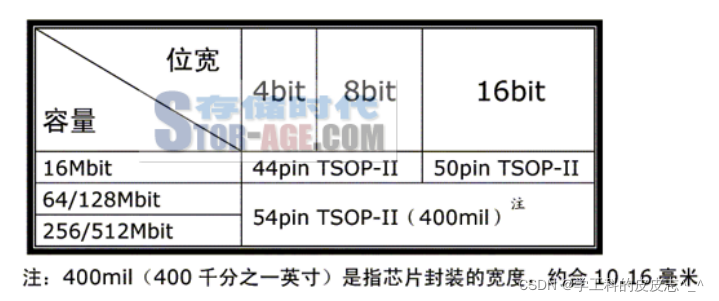

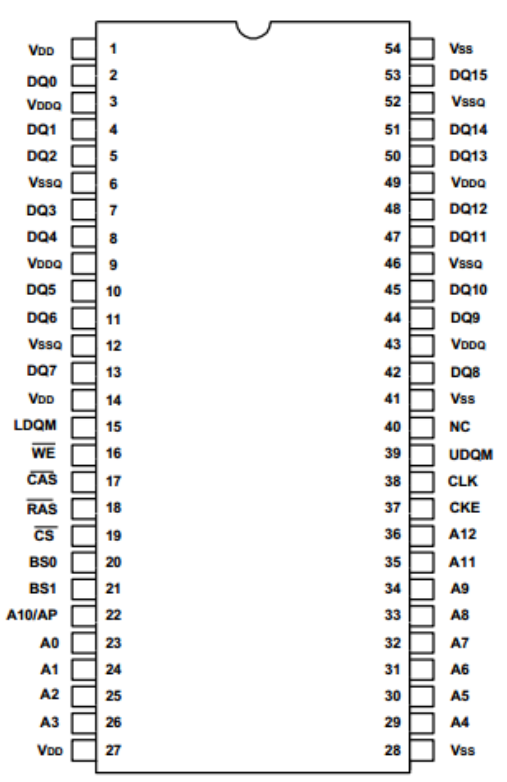

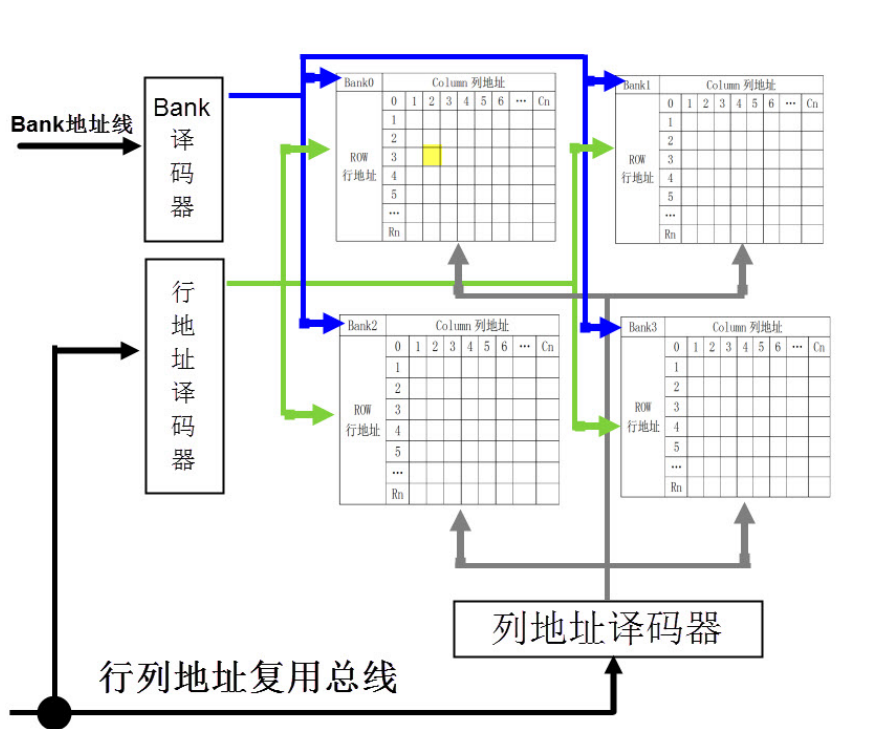

引脚模型

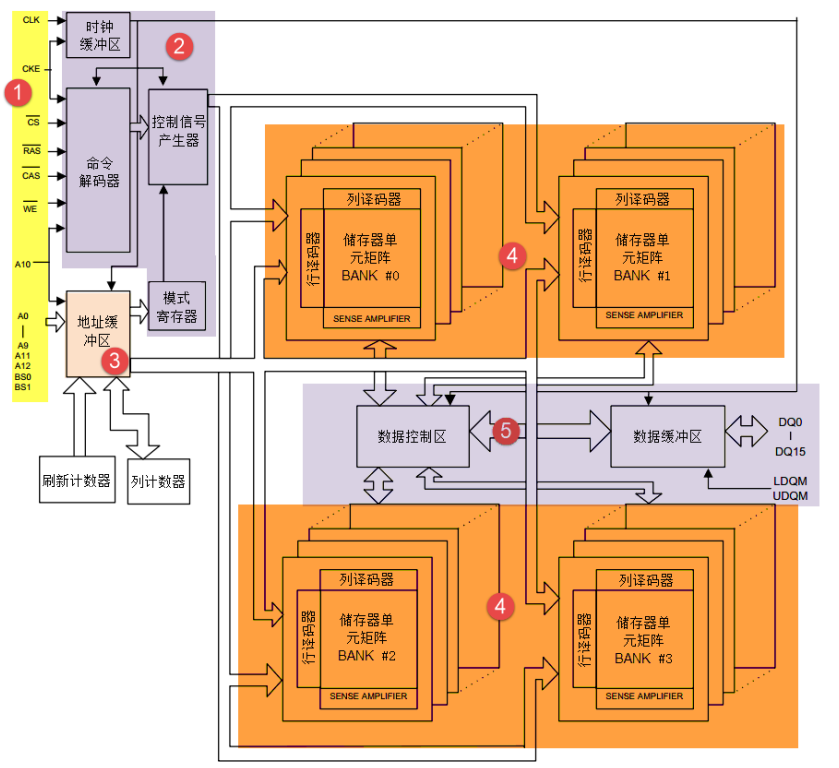

内部结构模型

型号为 W9825GKH-6 的SDRAM 芯片内部结构框图

控制逻辑

外部可通过 CS、WE、CAS、RAS 以及地址线来向控制逻辑输入命令,命令经过“命令器译码器”译码,并将控制参数保存到“模式寄存器中”,控制逻辑依此运行。

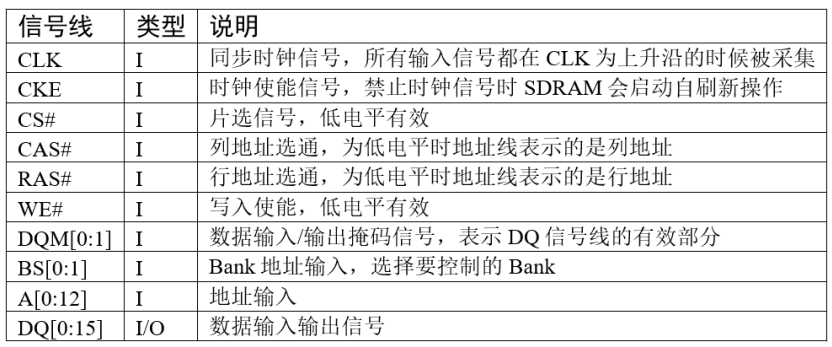

地址控制

SDRAM 包含有“A”以及“BS”两类地址线,A 类地址线是行 (Row) 与列 (Column) 共用的地址总线,BS 地址线是独立的用于指定 SDRAM 内部存储阵列号 (Bank)。在命令模式下,A 类地址线还用于某些命令输入参数。

通讯时当 RAS线为低电平,则“行地址选通器”被选通,地址线 A[12:0] 表示的地址会被输入到“行地址译码及锁存器”中,作为存储阵列中选定的行地址,同时地址线 BS[1:0] 表示的 Bank 也被锁存,选中了要操作的 Bank 号

接着控制 CAS 线为低电平,“列地址选通器”被通,地址线 A[12:0] 表示的地址会被锁存到“列地址译码器”中作为列地址,完成寻址过程。

数据的输入输出

若是写 SDRAM 内容,寻址完成后,DQ[15:0] 线表示的数据经过图一种 SDRAM 芯片的内部结构框图 标号中的输入数据寄存器,然后传输到存储器阵列中,数据被保存;数据输出过程相反。

用 DQM[1:0] 线来配合,每根 DQM 线对应 8 位数据,用来选择通讯数据线的数量 8/16

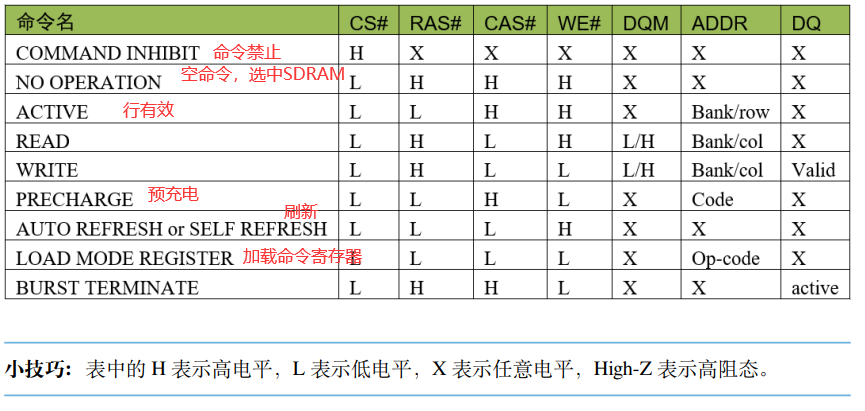

SDRAM 的命令

控制 SDRAM 需要用到一系列的命令,各种信号线状态组合产生不同的控制命令。

命令禁止

只要 CS 引脚为高电平,即表示“命令禁止”(COMMAND INHBIT),它用于禁止 SDRAM 执行新的命令,但它不能停止当前正在执行的命令。

空操作

“空操作”(NO OPERATION),“命令禁止”的反操作,用于选中 SDRAM,以便接下来发送命令。

行有效

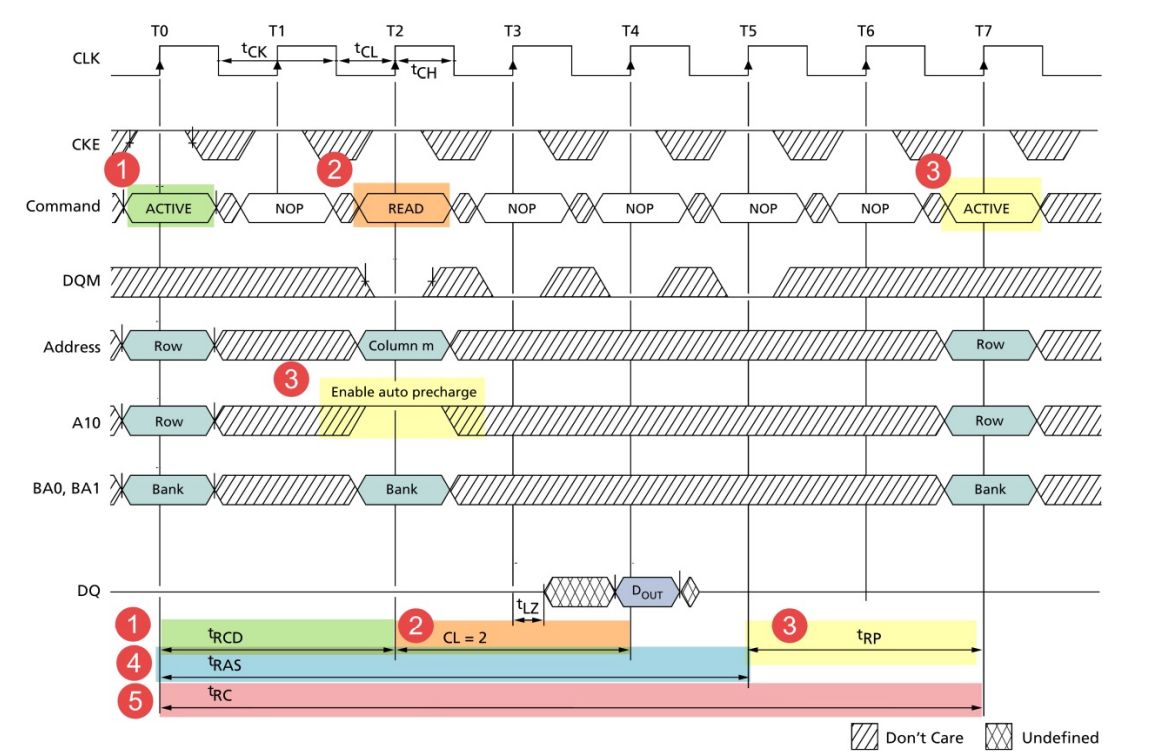

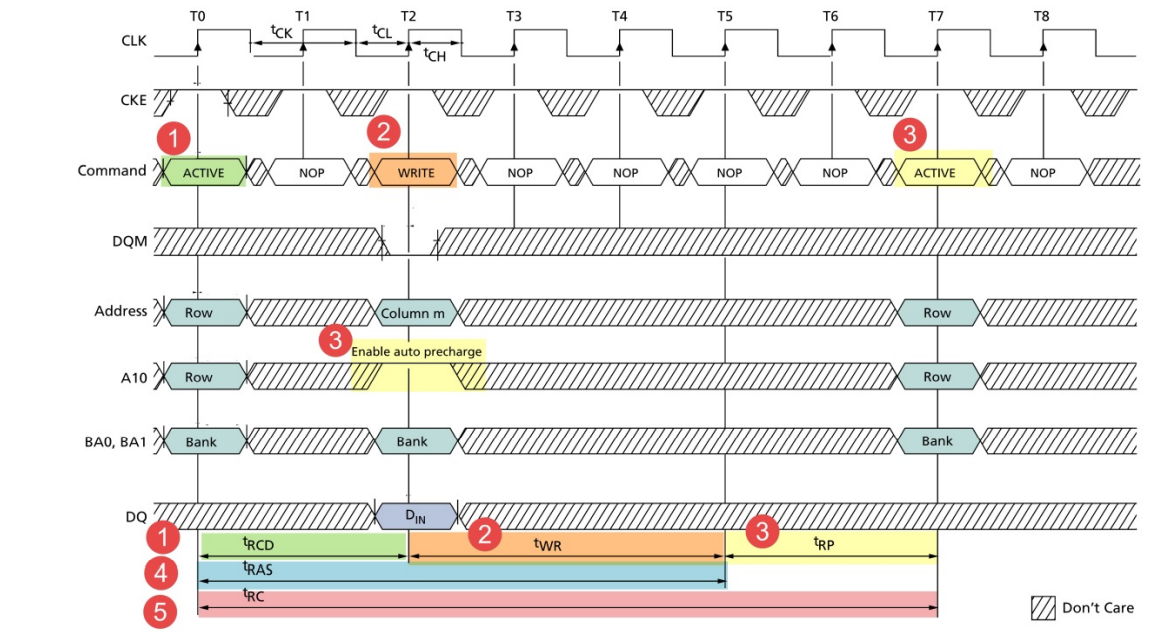

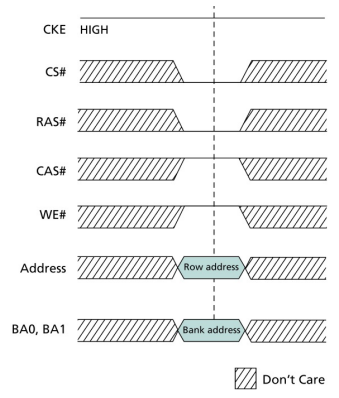

进行存储单元寻址时,需要先选中要访问的 Bank 和行,使它处于激活状态。该操作通过“行有效”(ACTIVE) 命令实现。

发送行有效命令时,RAS 线为低电平,同时通过 BA 线以及 A 线发送 Bank 地址和行地址。

列读写

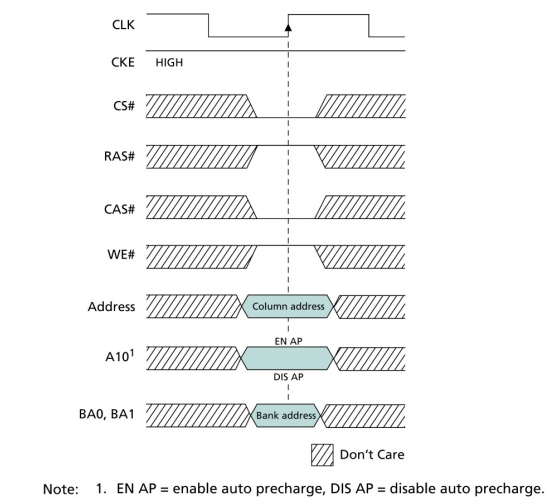

行地址通过“行有效”命令确定后,就要对列地址进行寻址了。“读命令”(READ) 和“写命令”(WRITE) 的时序很相似

通过共用的地址线 A 发送列地址,同时使用 WE

引脚表示读/写方向,WE为低电平时表示写,高电平时表示读。数据读写时,使用 DQM 线表示有效的 DQ 数据线。

而 A10 线用于控制是否“自动预充电”,该线为高电平时使能,低电平时关闭。

预充电

在读操作中会破坏内存单元行中的数据。因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。这一操作称为预充电,是行上的最后一项操作。必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

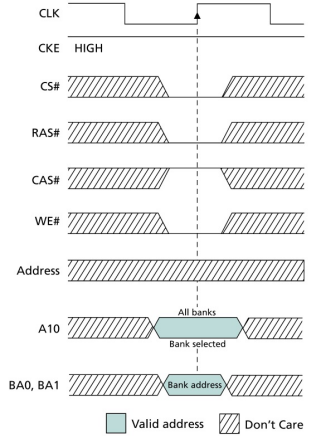

预充电可以通过独立的命令控制,也可以在每次发送读写命令的同时使用“A10”线控制自动进行预充电。

独立的预充电命令时序见图 PRECHARGE 命令时序 。该命令配合使用 A10 线控制,若 A10 为高电平时,所有 Bank 都预充电;A10 为低电平时,使用 BA 线选择要预充电的 Bank。

刷新

SDRAM 要不断进行刷新 (Refresh) 才能保留住数据,因此它是 DRAM 最重要的操作。

刷新操作分为两种:“自动刷新”(Auto Refresh)与“自我刷新”(Self Refresh),发送命令后 CKE时钟为有效时 (低电平),使用自动刷新操作,否则使用自我刷新操作(CKE高电平)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。

对于“自动刷新”,SDRAM 内部有一个行地址生成器(也称刷新计数器)用来自动地依次生成行地址,每收到一次命令刷新一行。

在刷新过程中,所有 Bank 都停止工作,而每次刷新所占用的时间为 N 个时钟周期,在这 N 个时钟期间内,所有工作指令只能等待而无法执行。

这个对同一行刷新操作的时间间隔,称为 SDRAM 的刷新周期,通常为 64ms。

“自我刷新”则主要用于休眠模式低功耗状态下的数据保存,也就是说即使外部控制器不工作了,SDRAM 都能自己确保数据正常。

在发出“自我刷新”命令后,将 CKE 置于无效状态 (低电平),就进入自我刷新模式,此时不再依靠外部时钟工作

在自我刷新期间除了 CKE 之外的所有外部信号都是无效的,只有重新使 CKE 有效才能退出自我刷新模式并进入正常操作状态。

加载命令模式寄存器

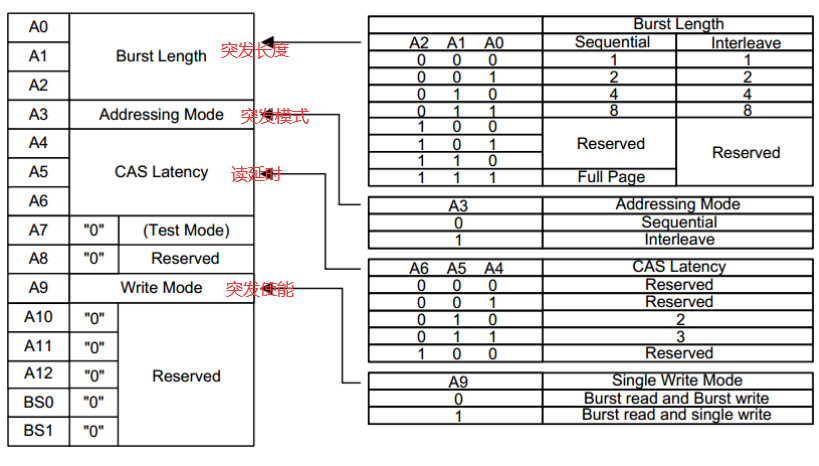

加载模式寄存器”命令 (LOAD MODE REGISTER)

。

发送该命令时,使用地址线表示要存入模式寄存器的参数“OP-Code”

-

Burst Length

突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度

若传输时实际需要数据长度小于设定的 BL 值,则调用“突发停止”(BURSTTERMINATE) 命令结束传输

突发读写是以数据线的位宽为单位的,比如当前位宽为16Bit,突发读写是2,则一次读写的长度是4个字节,也可以说突发长度是读写次数 -

BT

模式寄存器中的 BT 位用于设置突发模式,突发模式分为顺序 (Sequential) 与间隔 (Interleaved) 两种。在顺序方式中,操作按地址的顺序连续执行

一般用顺序模式。顺序访问模式时按照“0-1-2-3-4-5-6-7”的地址序列访问。 -

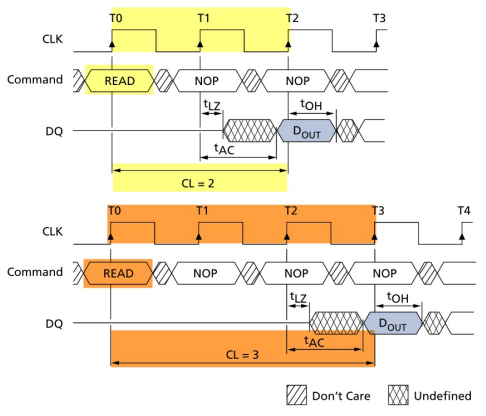

CASLatency

模式寄存器中的 CASLatency 是指列地址选通延迟,简称 CL。在发出读命令 (命令同时包含列地址) 后,需要等待几个时钟周期数据线 DQ 才会输出有效数据

CL 只是针对读命令时的数据延时,在写命令是不需要这个延时的,发出写命令时可同时发送要写入的数据。 -

Op Mode

OP Mode 指 Operating Mode,SDRAM 的工作模式。当它被配置为“00”的时候表示工作在正常模式 -

WB

WB 用于配置写操作的突发特性,可选择使用 BL 设置的突发长度或非突发模式。

一般是非突发模式

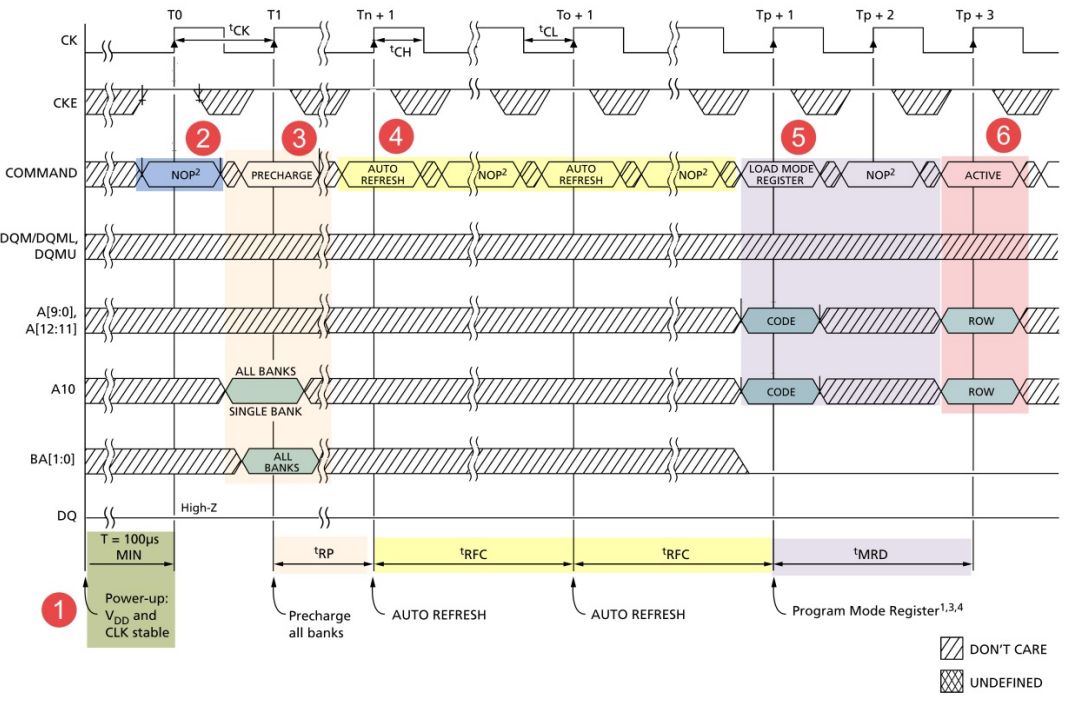

SDRAM初始化流程

SDRAM 并不是上电后立即就可以开始读写数据的,它需要按步骤进行初始化,对存储矩阵进行预充电、刷新并设置模式寄存器

t M R D t_{MRD} tMRD 也可为 t R S C t_{RSC} tRSC

SDRAM读写流程

初始化步骤完成,开始读写数据