一、前言

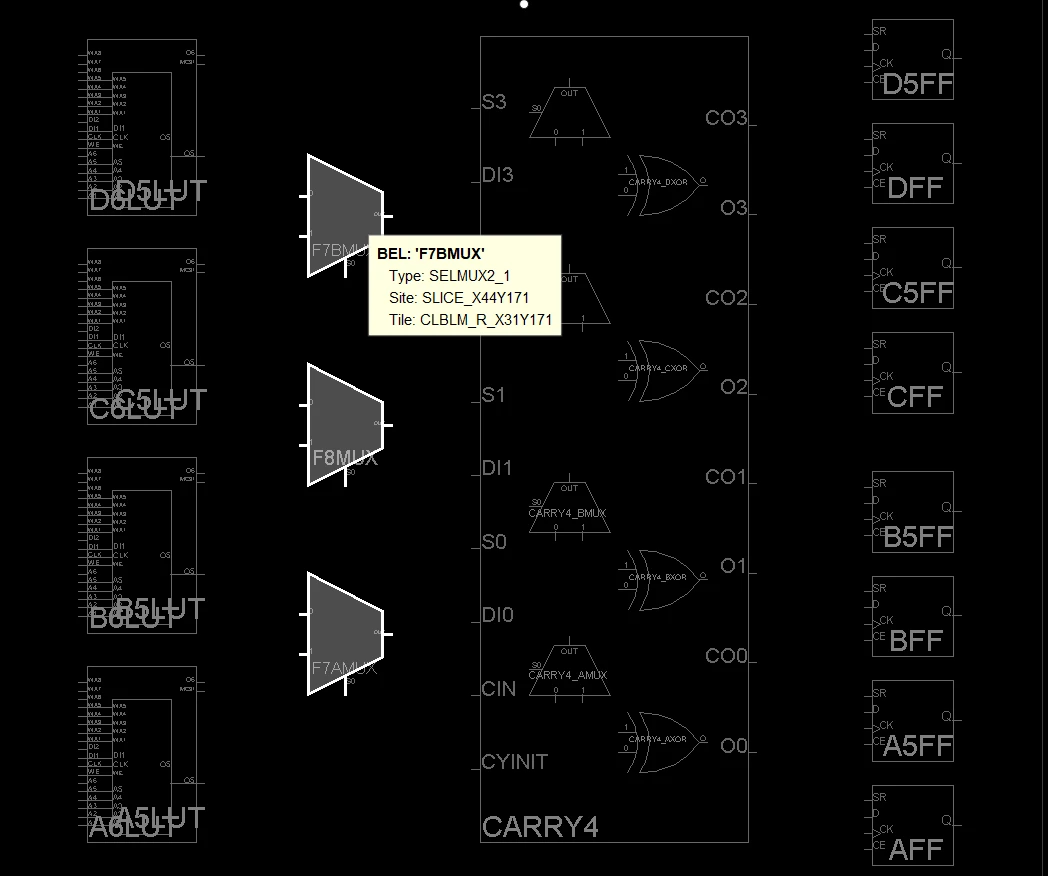

选择器在FPGA中是基础的组成部分,英文全称为Multiplexer,为一个多输入单输出的结构。以器件xc7k480tffv1156为例,在slice中,也可以看到F7AMUX,F8MUX,这两个MUX都是二输入单输出的选择器。

二、工程实现

以8-1选择器,8输入为例进行设计

2.1 设计代码

module MUX( sel,in,out );

input [2:0] sel;

input [7:0] in;

output reg out;

always@(sel)

begin

case(sel)

3'b000: out<=in[0];

3'b001: out<=in[1];

3'b010: out<=in[2];

3'b011: out<=in[3];

3'b100: out<=in[4];

3'b101: out<=in[5];

3'b110: out<=in[6];

3'b111: out<=in[7];

endcase

end

endmodule测试代码,选择变量sel每隔1ns加1,输入in每10ns增加1111。

module MUX_tb;

reg [2:0] sel;

reg [7:0] in;

wire out;

initial

begin

sel=3'b000;

in=8'b0000_0000;

end

always #1 sel=sel+1;

always #10 in=in+8'b1111;

MUX mux_test(.sel(sel),.in(in),.out(out));

endmodule2.2 仿真结果

sel的值可看做in中地址值,sel为0时输出out即为in[0]的值,sel为1时输出out即为in[1]的值,输入in中左边为高位,右边为低位。