收藏一篇关于61580使用的文章,侵删!

原文地址:http://emesjx.spaces.eepw.com.cn/articles/article/item/100023

1、BU-61580有“缓冲”和“透明”2种存储模式,前者使用BU-61580内部4Kx16bit缓冲区,后者使用外部RAM作为数据缓冲区,最大可达64Kx16bit。

2、BU-61580的缓冲模式又分“8-bit”,和“16-bit”2种结构。分别称为“8-bit缓冲模式”与“16-bit缓冲模式”。

3、BU-61580读写模式有“0等待”与“非0等待”2种,与上述缓冲模式组合成4种工作模式:(1)8-bit缓冲、0等待;(2)8-bit缓冲、非0等待;(3)16-bit缓冲、0等待;(4)16-bit缓冲、非0等待。

4、所谓“0等待”就是主控CPU(MCU、ARM、DSP等)存贮61580内部缓冲区时不用插入等待周期,在发出读/写命令(Select、STRBD、RD/WR#)后,61580的数据准备好信号(READYD#)立即有效(为低),因此主控CPU可以不用判断READYD#信号。

要注意一点的是,对于读操作来说,这时D0-D15代表的不是本次读操作地址对应单元的内容,而是上次读操作地址对应单元的内容,这是由61580内部逻辑决定的(即所谓的“输出数据延时”)。

这样,对于连续读操作,第一次读数据无效(空操作),第二次读到的是第一次地址的内容,第三次读到的是第二次地址的内容,依次类推;如果是随机读操作,两次读相同地址即可,第二次数据有效。

5、有一个特例就是“中断状态寄存器”需要读3次才行:第一次读,地址为ISR(0x06),数据无效;第二次读,地址任意(如0x00),数据无效;第三次读,除ISR外的任意地址(如0x00),数据有效。

6、在“0等待”模式,SELECT#和STRBD#负脉冲宽度必须>20ns。例如,主控CPU为DSP6203B时,主频为250MHz,其CPU时钟周期P=4ns,EMIF片选信号CEn脉冲宽度=7xP=28ns,但ARE#、AWE#脉宽只有3xP=12ns,因此,应用时只能用CEn驱动SELECT#和STRBD#。

如果使用主频更高的DSP,如64xx系列,上述脉宽条件再也无法满足,就必须使用“非0等待”模式,在读/写周期中插入相应的等待周期了。

7、“非0等待”就是高速主控CPU(如64xx系列DSP)异步存取61580时,每个读/写周期插入若干个等待周期,直到READYD#信号有效为止。注意61580的READYD#是参考Intel80286 CPU的专用芯片82284设计的,可与82284的ARDY#直接连接,经其同步处理后送给80286的READY#;但如用在TI的DSP中,必须做相应处理才能与其ARDY相连,即:ARDY=CEn or(not READYD#)。

8、BU-61580是5V供电,接口电平为TTL,与3.3V供电(LVTTL)的DSP和FPGA连接时,由于LVTTL向上兼容TTL,DSP/FPGA送给61580的地址、控制信号可直接连接,但61580送给DSP/FPGA的状态信号以及双向数据总线必须经过电平转换(例如使用TI的SN74LVT245),否则会形成电流倒灌损坏芯片。

1553B总线控制器61580使用

news/2024/12/29 19:11:06/

相关文章

超全总线控制方式总结

总线控制

看了网络上的文章,质量真的不太行,就自己结合着整理一下。

总线控制主要是两个大方面,总线判优控制和总线通信控制。

一、总线判优控制

总线上同一时刻只允许一个设备进行占用,为了防止冲突,我们引入了判…

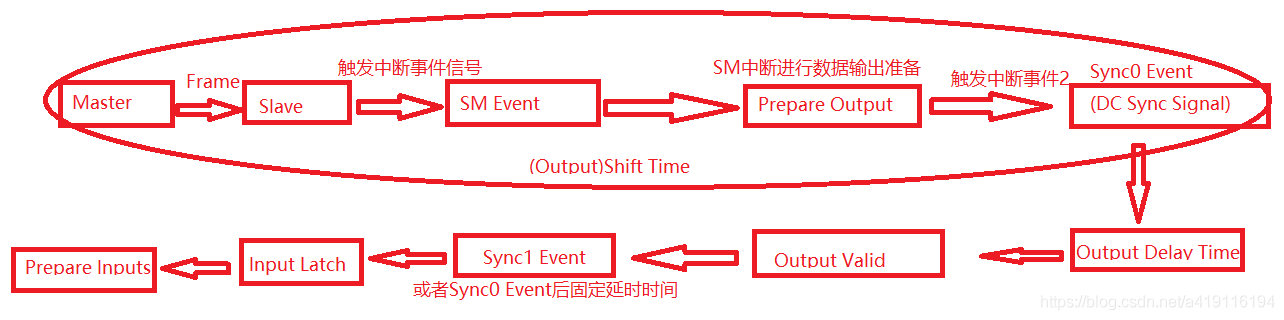

EtherCAT总线通信Freerun、SM、DC三种同步模式分析

EtherCAT总线三种同步模式分析

一、 分布式时钟作用

使所有EtherCAT设备使用相同的系统时间,从而控制各设备任务的同步执行。

二、 名词解析

1、 现场总线高速数据传递:即主站周期的向从站发送输出信息并周期地读取从站的输入信息 2、 Output Valid&…

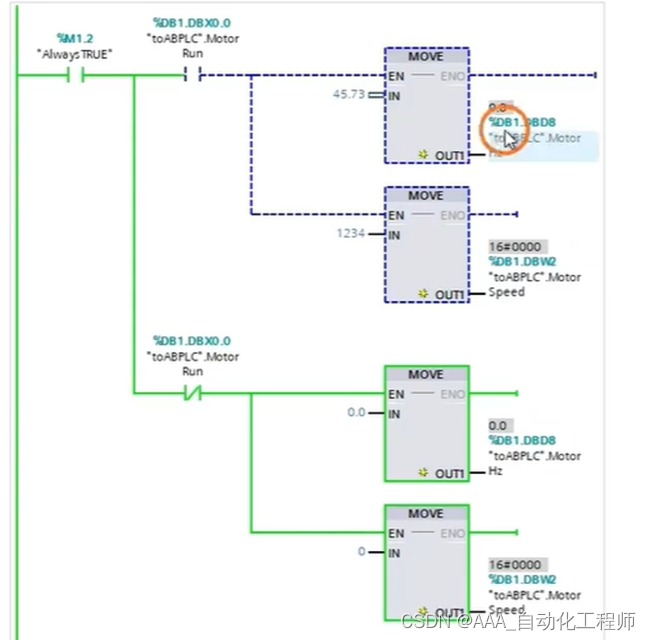

罗克韦尔AB PLC 通过KEPServer实现与西门子1200PLC的以太网通信

罗克韦尔AB PLC 通过KEPServer实现与西门子1200PLC的以太网通信 环境搭建: 软件: Studio 5000 V33.01.01 KEPServerEX 6.4 TIA PORTAL V17

整体架构如下图所示:

打开博途软件,如下图所示,新建2个DB块,分别添加如下变量,

如下图所示,在FC1中编写测试程序

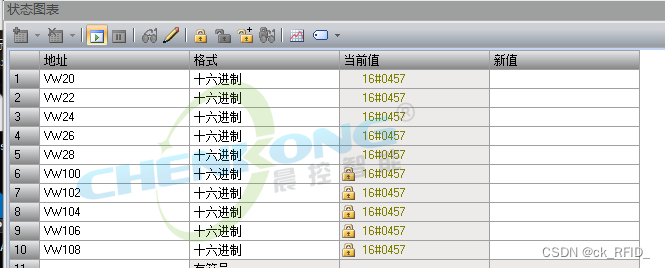

西门子S7-200 SMART(6ES7 288-1ST40-0AA0)相关与晨控智能CK-FR08-E00关于modbus tcp 通信配置指南

西门子S7-200 SMART(6ES7 288-1ST40-0AA0)相关与晨控智能CK-FR08-E00关于modbus tcp 通信配置指南 准备阶段

软件:STEP 7-MicroWIN SMART

PLC:S7-200 SMATR (6ES7 288-1ST40-OAAO)

读卡器:CK-FR08-E00

交换机:标准POE交换机

电源&#x…

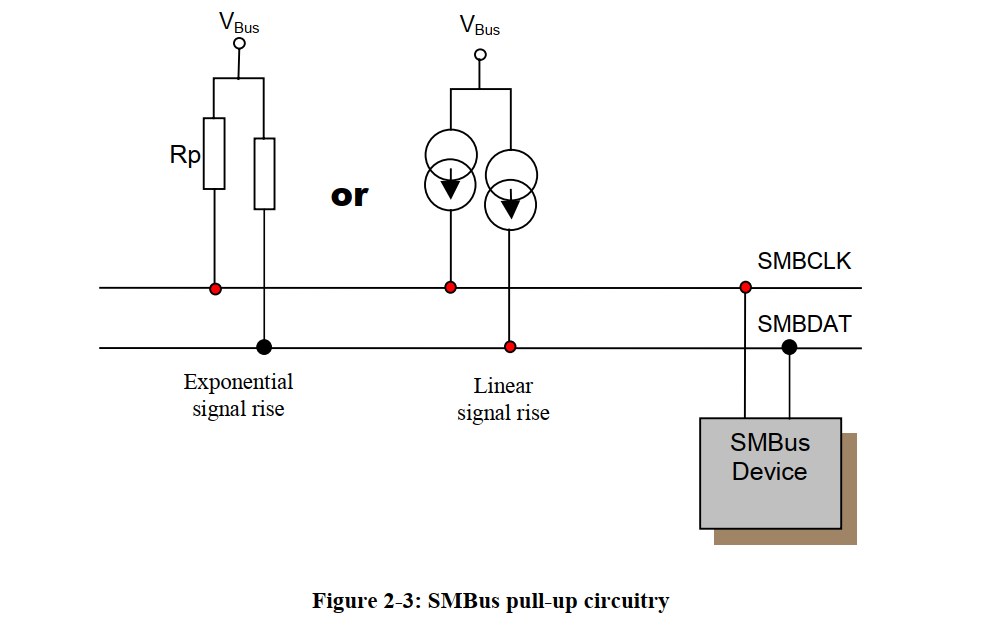

12.嵌入式控制器EC实战 SMBus概述

文章目录 SMBus概述ACPI规范中的函数返回值含义SMBus.h中的宏定义含义EC中SMBus各个读写函数分析bRWSMBus读写函数在嵌入式控制器EC中,SMBus的起到的作用有两个,第一个是通过SMBus读取智能电池中的相关信息,第二个则是通过SMBus总线读取CPU、GPU或者主板上其他位置的温度传感…

SMART PLC运动超驰功能编程应用(含V2.7版本固件下载)

什么是运动控制超驰功能,运动超驰功能如何开启,请参看下面的导图部分: 下面一步步教大家如何更新CPU固件版本。

S7-200 SMART PLC自定义脉冲控制功能块相关详细组态设置,请参看下面的博客。链接如下:

S7-200 SMART PLC自定义脉冲轴控功能块AxisControl_FB(梯形图)_RXX…

详细的组态王软件与200 Smart PLC网口通信教程

1、下载驱动

组态王软件是北京亚控科技有限公司的产品,也是比较常用的,今天就讲一下怎么与西门子200smartPLC的通信,我们知道,组态王安装之后,相关的设备驱动软件里面是没有的,所以我们需要去官网上下载相…

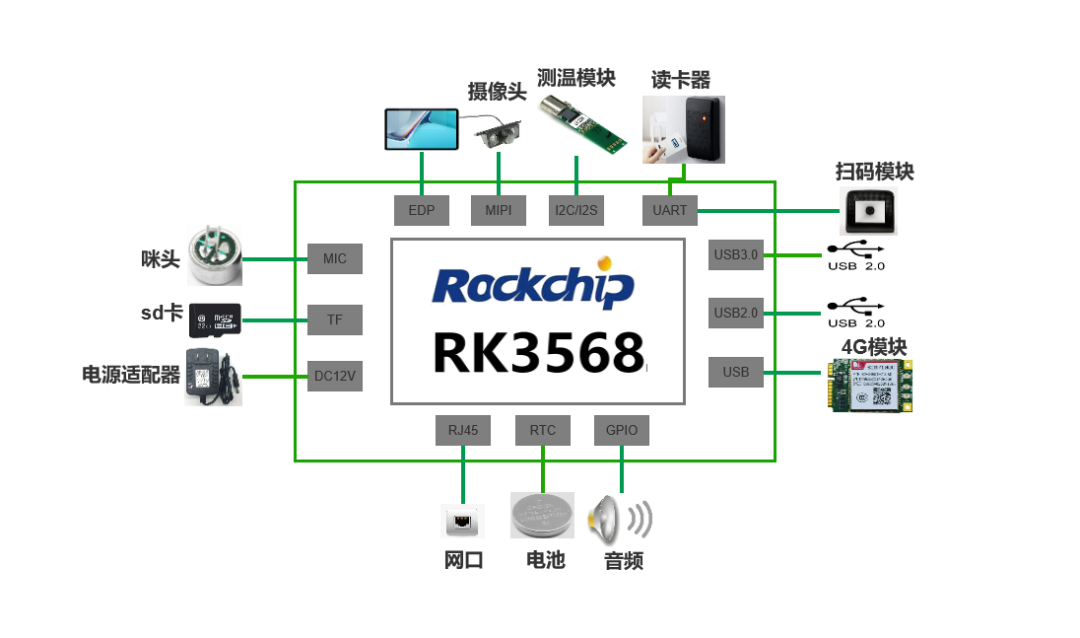

RK3568+Codesys ARM+LINUX硬件平台的软PLC解决方案

CODESYS Control Linux ARM SL

符合IEC 61131-3标准且适用于ARM & Linux硬件平台的软PLC。 产品描述

CODESYS Control Linux ARM SL是适用于ARM & Linux硬件平台的CODESYS Runtime。Runtime的功能可以通过系统的硬件属性进行扩展。CODESYS IDE安装过附带的CODESYS部署…