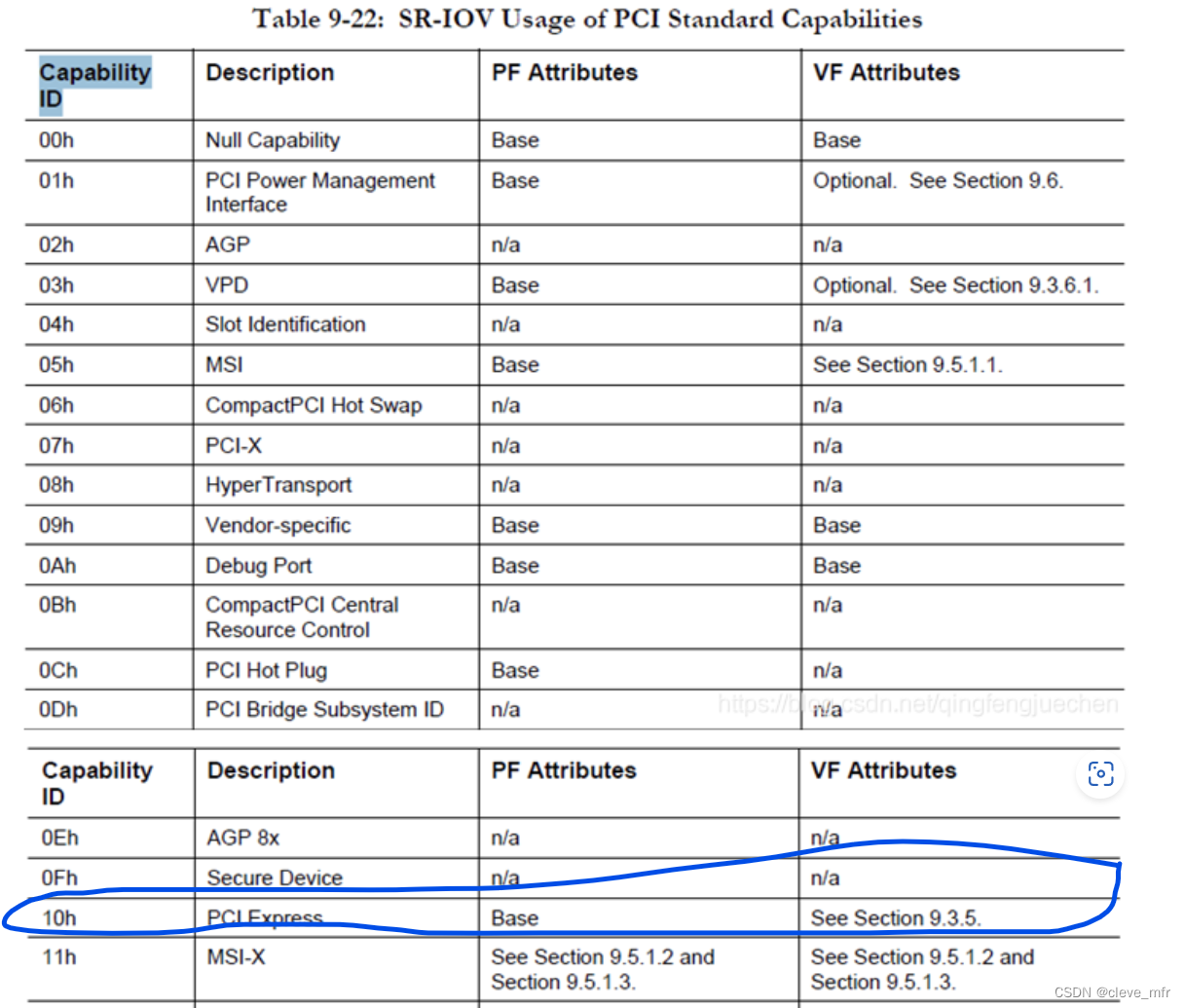

1、Capability id link:https://blog.csdn.net/qingfengjuechen/article/details/113104827(具体参考PCIE规范手册)

intel有清晰的结构定义:

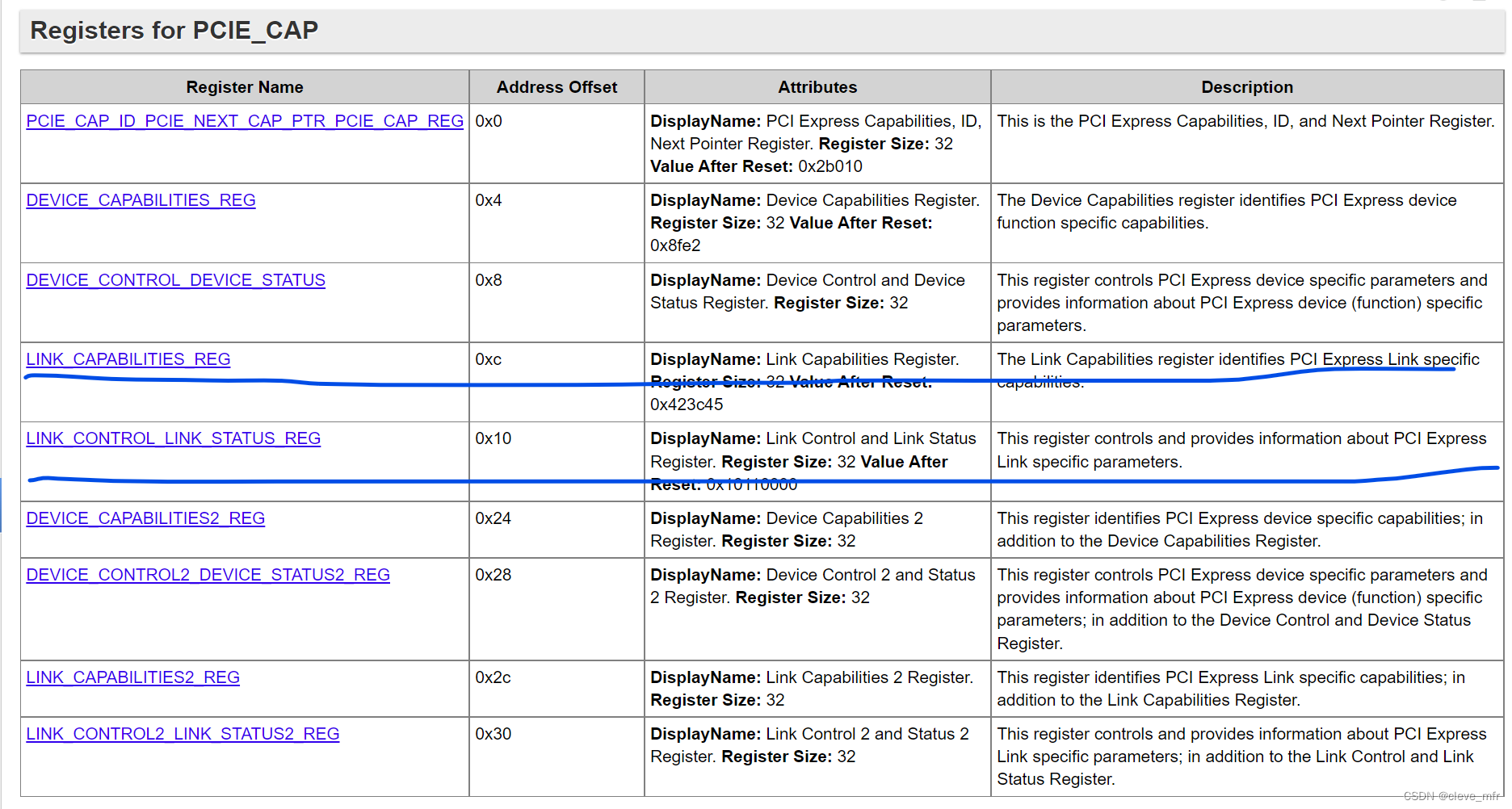

6.1.3. PCI Express Capability结构 (intel.cn)![]() https://www.intel.cn/content/www/cn/zh/docs/programmable/683527/19-3/pci-express-capability-structures.html

https://www.intel.cn/content/www/cn/zh/docs/programmable/683527/19-3/pci-express-capability-structures.html

其中Capability ID为0x10,表示该设备某一function的pcie基本寄存器参数。

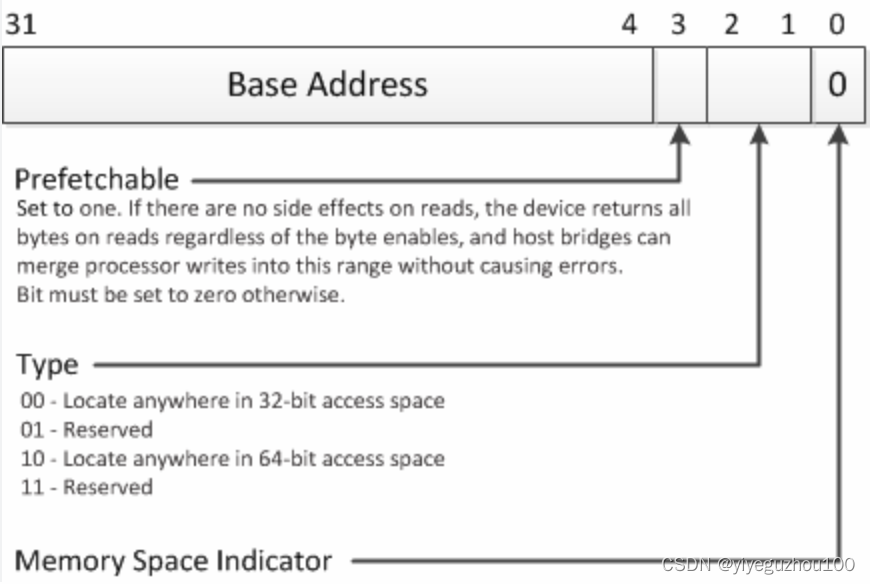

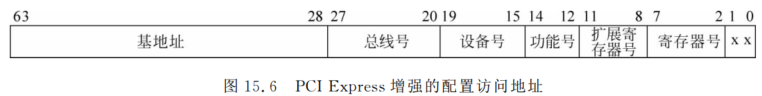

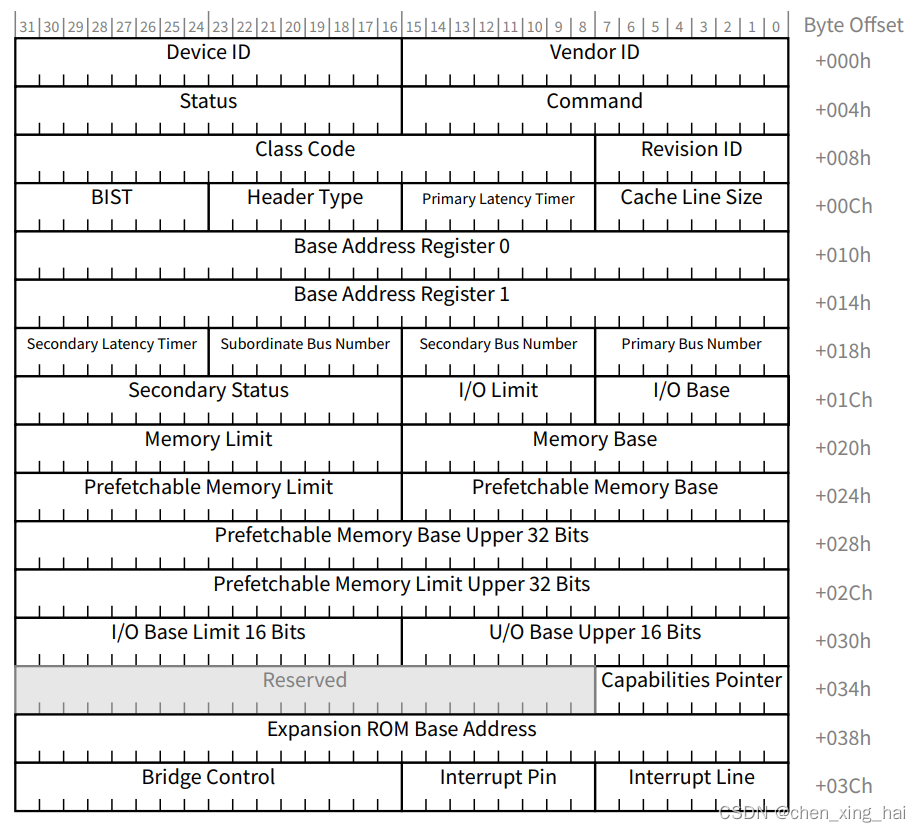

2、address offset:Configuration Space Registers(具体细节可以参考pcie手册)

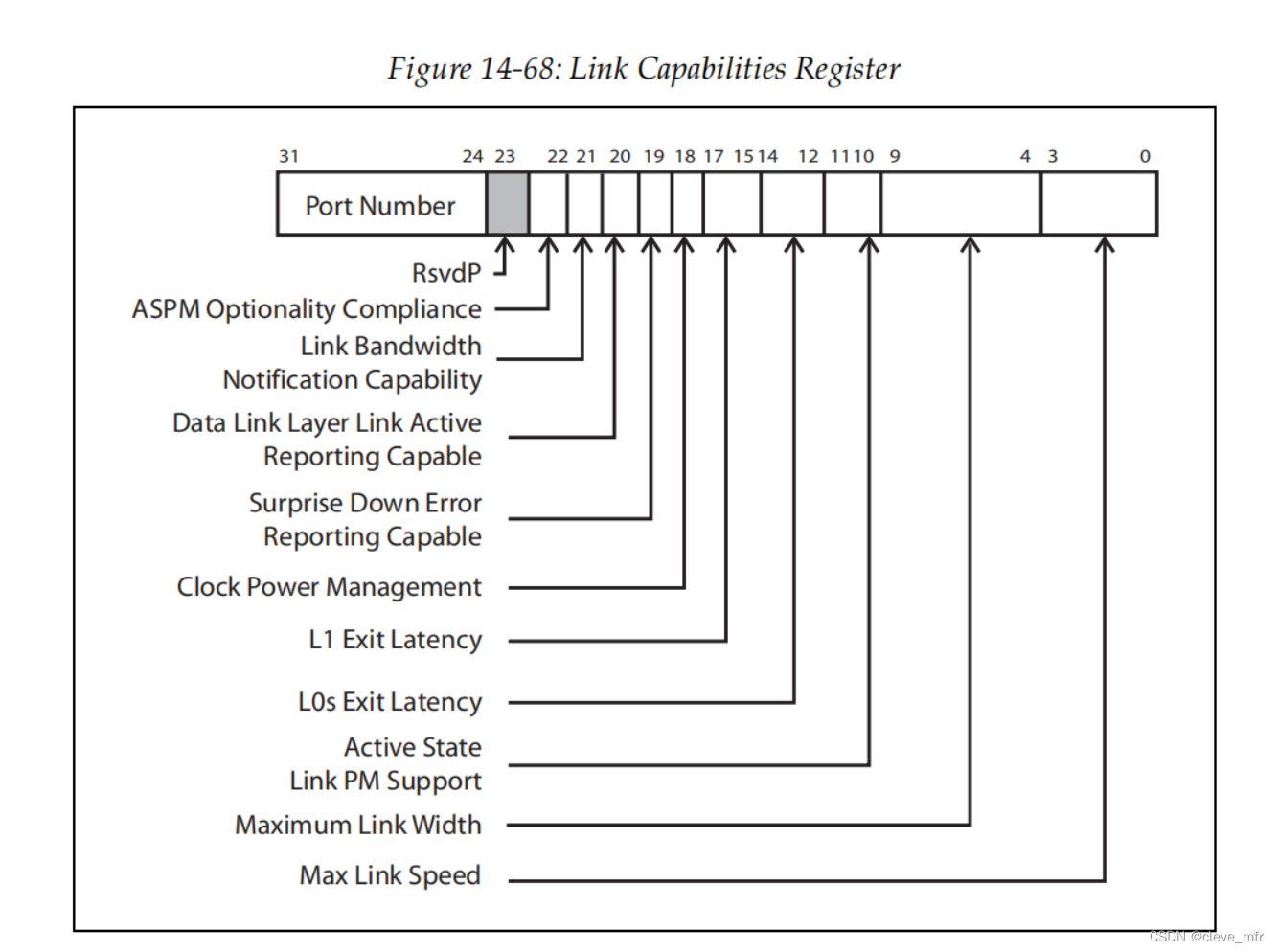

相对Capability偏移量0xC处为Link_Capabilities_Reg,偏移量为0x10Link_Control_Link

_Status_reg。

3、附几个寄存器具体定义

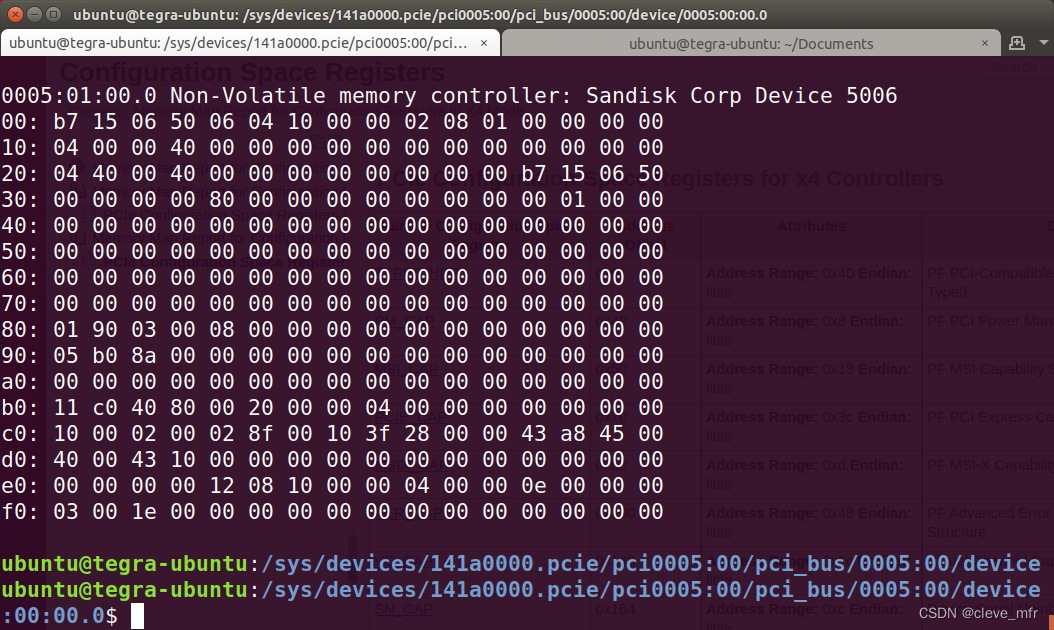

4、PCIe Configuration Space Registers for x4 Controllers:

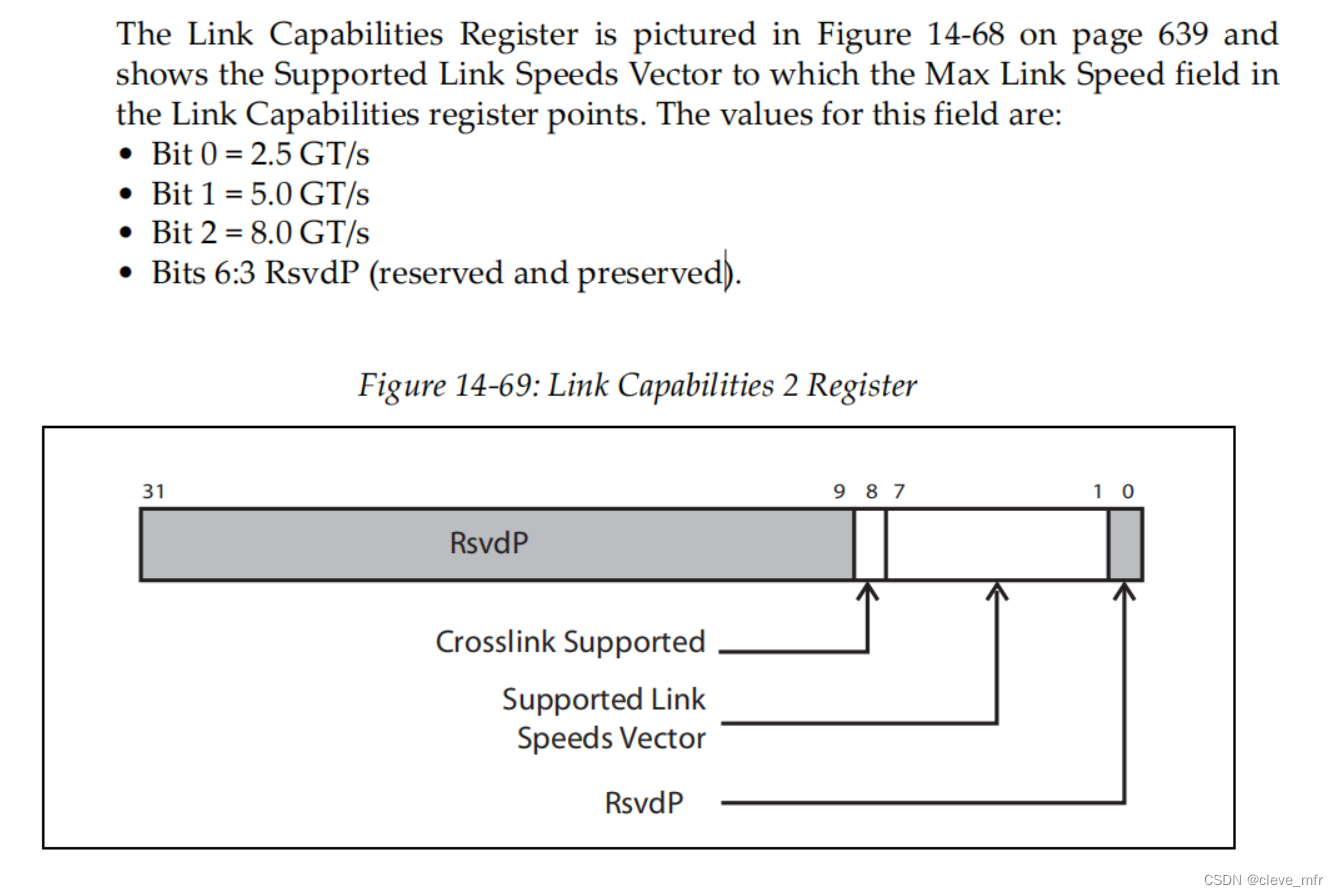

拿nvme x4 3.0硬盘为例,0xC0为PCIE Capability ID Reg space起始地址,0xCC为Link_Capabilities_Reg,值为0x00458a43,表示该设备最大支持PCIE3.0 和 X4;0xD2为Link_Status_Reg,值为0x1043,表示经过链路训练后,设备协商为PCIE X4工作模式。