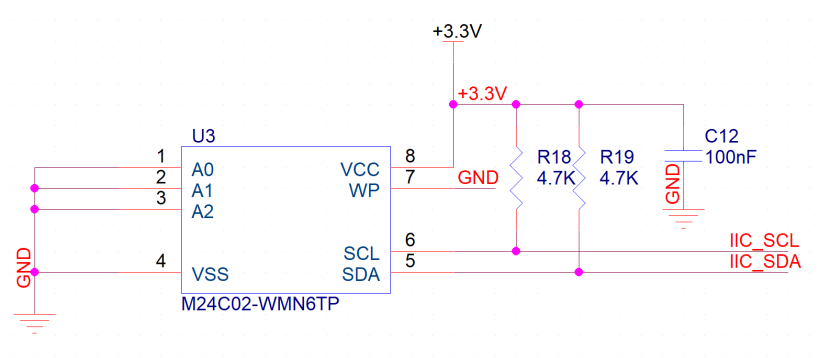

明德扬 Kintex-7 系 列MP5650 核 心 板M24C02-WMN6TP 是基于 I2C 总线的 EEPROM 存储器件,遵循二线制协议,它具有接口方便,体积小,数据掉电不丢失等特点。EEPROM 硬件连接的示意图:

产品手册

产品手册

明德扬XILINX-K7-325T/410T核心板数据手册

news/2025/2/7 10:53:16/

相关文章

关于K7中是否每一组MGT接口都可以接10G SFP的试验

在做新的一版SDR平台时候有一个疑问就是,就是关于K7高速口的分配,要用到6组高速口接SFP,其中QSFP占用4对,单路SFP两个占用两对。这些高速对是否可以任意分配到高速口上呢,这就是接下来试验要解决的问题。

首先从已经有的经验&…

Xilinx K7_Microblaze的Tmrintc定时器中断使用(ISE14.7)

在软核中加入Axi_timer和Axi_intc的IP核,然后完成连线,axi_intc的中断信号要接到软核的中断引脚上。 axi_timer的中断信号要和axi_intc的中断信号相连,这样才能保证定时器中断的触发。

注意,axi_intc的Intr引脚是一个输入类型的信…

【原创】Xilinx:K7 DDR3 IP核配置教程

【原创】Xilinx:K7 DDR3 IP核配置教程

本文为明德扬原创文章,转载请注明出处!

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制和读写时序的情况下,也能通过MIG IP控制器读写…

半高半长 PCIe 20G 以太网实 存储卡 K7

PCIE731-1 是一款基于 PCI Express 总线架构的 20G 以太网实时抓包存储卡,该产品为半高半长 PCIe 卡。 板卡采用 FPGA 控制器,可以实现 20G 以太网数据的实时收发能力,对以太网数据包进行分析、过滤、加密处理等算法,并将数据实时…

XILINX K7 DDR3引脚验证总结

最近做了一个FPGA引脚验证,搞的很不顺利,各种坑人的问题,在这里分享一下遇到的问题和解决方法;希望能帮到大家。如果有问题欢迎交流,QQ1823167315

先介绍背景

XILINX FPGA型号:xc7k325t ffg900-2

工具版…

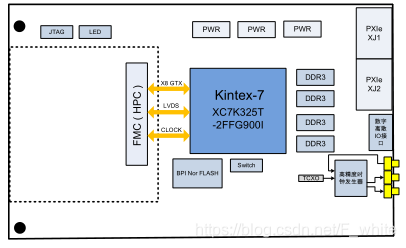

K7 PXIE数据处理板(Kintex-7 FMC载板)

PXIE301是一款基于PXI Express总线架构的高性能数据预处理FMC 载板,板卡具有 1 个 FMC(HPC)接口,1 个 X8 PCIe 主机接口,板卡采用 Xilinx 的高性能 Kintex-7 系列 FPGA 作为实时处理器,实现 FMC 接口数据的…

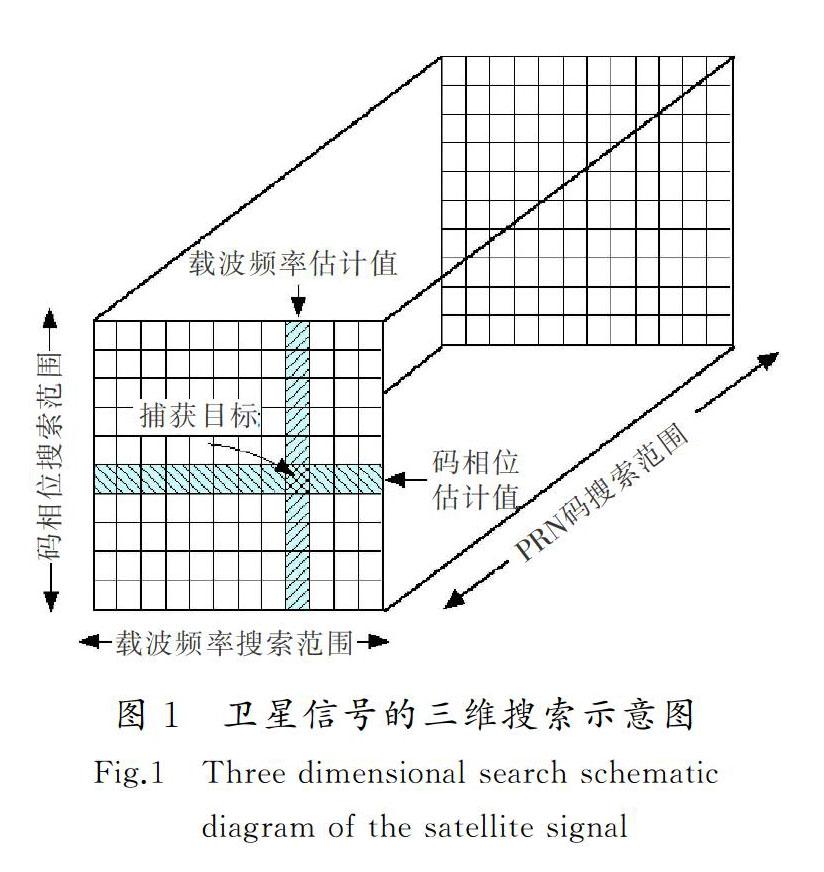

C6678/C6657+ZYNQ/K7/A7 FPGA+AD+北斗的软硬件设计方案

针对当前北斗导航定位接收机在高动态和复杂电磁环境下定位精度不高的问题,本文在了解卫星导航原理的基础上,介绍了一种基于DSPFPGA 的嵌入式北斗导航接收机的设计,以满足在高动态和复杂电磁环境下无人机、单兵、机器人等高精度导航定位的要求…

PCIE于 总线架构高性能数据预处理板 / K7 325T FMC接口数据采集传输卡

PCIE701 一款基于 PCI Express 总线的高性能 FMC 接口 PCIe 总线验证平台,板卡具有 1 个 FMC(HPC)接口,1 个 X8 PCIe 主机接口,板卡采用 Xilinx 的高性能 Kintex-7 系列 FPGA 作为主控制器,实现 FMC 接口数…