开发板:Xilinx K7 KC705

软件:ISE14.7

1.由于应用需求,我们要将开发板作为主机端,通过PCIe接口转接板外接一个NVMe PCIe SSD。并由FPGA控制SSD的数据读写。

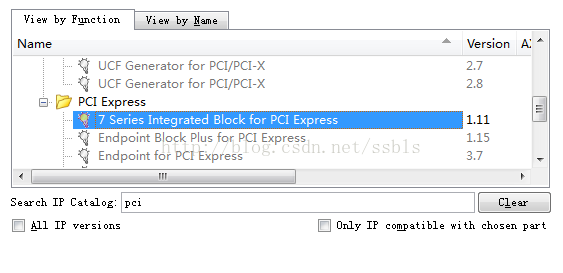

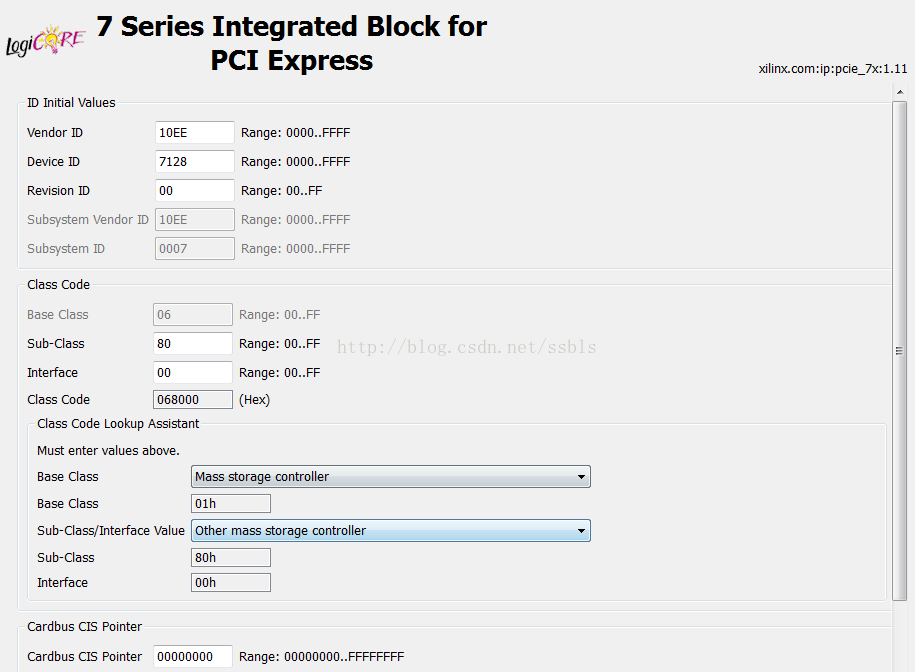

因此我们例化生成了一个作为主机端的 PCIe IP核。

类型选择为Root Complex

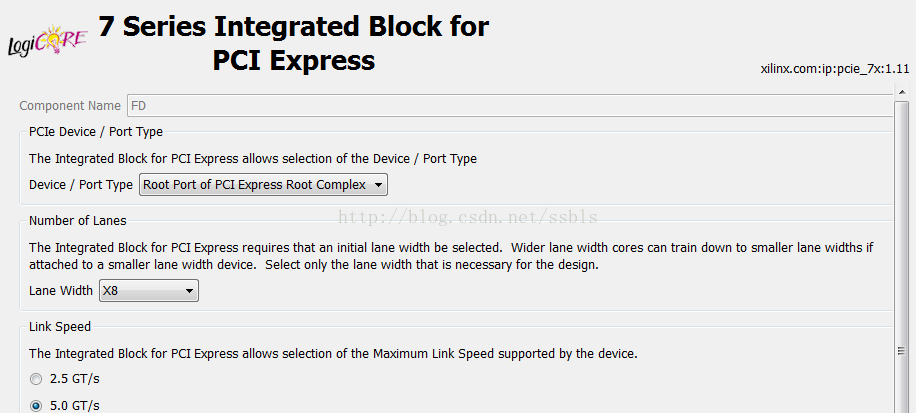

这里我们将可设置的几项配置成抓取到的PCIe NVMe SSD的内部相应参数。

生成pcie核之后,在其目录下将example文件夹中的例程导入ISE中。

阅读其ucf文件,发现其中并没有约束sys_clk_p和sys_clk_n这一组差分时钟信号。取而代之的是如下的代码:

# SYS clock 100 MHz (input) signal. The sys_clk_p and sys_clk_n

# signals are the PCI Express reference clock. Virtex-7 GT

# Transceiver architecture requires the use of a dedicated clock

# resources (FPGA input pins) associated with each GT Transceiver.

# To use these pins an IBUFDS primitive (refclk_ibuf) is

# instantiated in user's design.

# Please refer to the Virtex-7 GT Transceiver User Guide

# (UG) for guidelines regarding clock resource selection.

#

INST "refclk_ibuf" LOC = IBUFDS_GTE2_X0Y3;

这样的配置就可以了吗?还需要添加或修改什么代码吗?

参考网上的一些类似问题:如http://www.newsmth.net/nForum/#!article/FPGATech/45472?au=biscuit123。

我们推断,这里约束了buffer "refclk_ibuf"的位置,即同时将sys_clk_p和sys_clk_n的LOC确定了。因为在顶层文件xilinx_pcie_2_1_rport_7x中例化了

IBUFDS_GTE2 refclk_ibuf (.O(sys_clk), .ODIV2(), .I(sys_clk_p), .CEB(1'b0), .IB(sys_clk_n));

ucf中的上述约束即为将refclk_ibuf确定为IBUFDS_GTE2_X0Y3,而这个buffer的位置是固定的,因而输入端的sys_clk_p和sys_clk_n也就确定了,不需要再进行约束。

上述分析纯属个人推断,如有误,还请留言指出。

同时在综合之后,打开PlanAhead以查看管脚映射:

发现sys_clk_p的管脚位置确实已经配置。并且修改IBUFDS_GTE2_X0Y3的值,综合后得到的管脚映射位置不一样,如下:

FPGA管脚号 Bank 时钟来源位置

IBUFDS_GTE2_X0Y0:sys_clk_p R8 未连接

IBUFDS_GTE2_X0Y1:sys_clk_p V8 115 PCIE_8LANE_EDGE

IBUFDS_GTE2_X0Y2:sys_clk_p L8 116 SI5324C-C-GM

IBUFDS_GTE2_X0Y3:sys_clk_p N8 116 FMC接口

IBUFDS_GTE2_X0Y4:sys_clk_p G8 117

IBUFDS_GTE2_X0Y5:sys_clk_p J8 117 FPGA管脚J16

IBUFDS_GTE2_X0Y6:sys_clk_p C8 117 HPC接口

IBUFDS_GTE2_X0Y7:sys_clk_p E8

具体连接位置可参照开发板的原理图。

在这里我们应该写成INST "refclk_ibuf" LOC = IBUFDS_GTE2_X0Y1;

这样两个输入时钟信号将接到金手指上,其输入来源是PCIe插槽转接板上的100MHz时钟。

具体PCIe接口信息可参见博文:http://blog.csdn.net/michaelcao1980/article/details/42778405

2.PCIe和NVMe的初始化完成,CSTS.RDY信号拉高,按照协议要求,我们想发送第一个指令:Identify。按照要求,我们修改了Admin SQ Doorbell寄存器。想要等待SSD给主机返回 读TLP包,但是在PCIe核的数据返回接口并没有抓到数据,过了一段时间之后,收到一个MXI中断包。

这是什么问题?