ARM V8 SPEC A1.1 ARM V8 架构的简介

第一节:ARM 架构基本概念

第二节:ARM架构提供的数据类型

第三节:高级SIMD和浮点

第四节:ARM的memory model引言

文章目录

- ARM V8 SPEC A1.1 ARM V8 架构的简介

- 前言

- 第一节:ARM架构基本概念

- 第二节:ARM架构支持的数据类型

- 第三节:高级SIMD和浮点

- (1)SMID支持的指令

- (2) 浮点的标准和术语

- (3)ARM标准的浮点输入和输出值

- (4)Flush to zero

- (5)NaN handling and default NaN

- (6)Round to odd mode

- 第四节 ARM memory model引言

- 总结

前言

平时做ARM cpu性能分析,国内ARM相关的新资料很少,所以在学习的过程中,将自己的理解记录下,供ARM新人参考

第一节:ARM架构基本概念

arm reference 是对processing element简称(PE)行为的定义, PE可以理解为处理单元,重点是行为的定义,而不是具体设计的定义或者限制,此外也对软件开发者使用ARM PE进行了说明。

此外ARM还有用于debug的架构,trace(追踪)架构,后面章节介绍.

由于ARM架构具有:1,统一的寄存器文件;2.load,store的架构,数据的运算仅在寄存器上进行;3,简单的地址模式,所有的地址来源于寄存器的内容和指令的filed.所以arm架构属于精简指令集。

此外架构还定义了PE和memory的交互行为,其中包括了cache, memory translation。

【关键名字释义】

- AArch64: 64-bit execution state; 地址保存在64-bit registers;31 个通用寄存器,X30是程序链接寄存器,提供了64 bit的PC, SP,以及异常链接寄存器,提供了32个128bit的SIMD向量和浮点寄存器;定义了ARM8的异常模型;支持64bit的虚拟地址;定义了一些PSTATE的寄存器来存储PE state;定义了不同级别的系统寄存器;仅支持一个指令集:A64

- AArch32: 32-bit execution state; 地址保存在32-bit registers;13个32bit 的通用寄存器;32个64bit的SMID寄存器和浮点寄存器;…etc;支持两个指令集:A32和T32(32和16bit混用的指令编码)

- ARM: Application profile(VMSA); Real-time profile(PMSA); Microcontroller profile;

- Excution state:执行环境,包括:支持的寄存器位宽,支持的指令集,其中最重要的部分包括:异常模型,VMSA,程序员的模型,其中很重要的一种环境是是执行在AArch64还是32,对于AArch64:

- system register: 提供了控制和info;系统寄存器主要包含以下三个部分:1.系统通用控制寄存器;2.debug寄存器;3;时钟寄存器;4.pmr,性能监测寄存器;5.活动检测寄存器;6,trace 寄存器;7,GIC(General interrupt control)系统寄存器

- ARM V8 debug :ARM V8支持self-host debug(PE自己产生debug exception) 以及 external debug(debug event 自己产生debug state, PE是被外部控制下产生debug expection;这两者的使用场景不同,前者一般使用在应用后期维护中,后者使用在开发阶段。

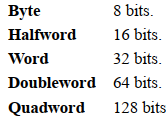

第二节:ARM架构支持的数据类型

此外还支持:

半精度,单精度,双精度,四精度 以及定点数据类型,向量这些数据类型都存储在通用系统寄存器以及SIMD&FP 寄存器(128bit),那如何判断某个时刻某个寄存器的数据宽度,或者说数据类型呢?

通过execution state可以判断:

对于AArch64:

通用寄存器一般作为64bit或者低32bit,SMID和浮点寄存器,四精度仅在SMID中,AArch64支持128Bit,有效位是64还是128取决于A64指令集的

对于AArch32:

通用寄存器支持32bit, 支持向量格式,不支持128bit的四精度

- 向量格式:

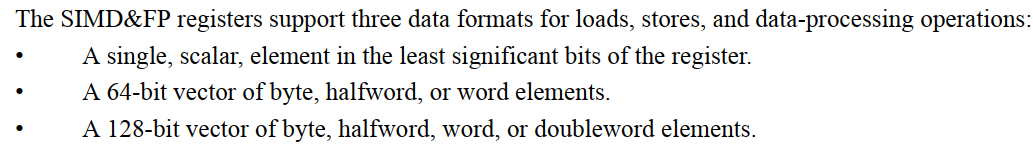

SMID&FP的寄存器可以包含1个或多个元素,类型和大小一样。寄存器和数据类型综合起来形成了这个向量元素,这样的向量被看作数组;

在AArch64的支持三种:

对于AArch32:

邻近的两个64double word的寄存器可以组成一个四word的寄存器; - 半精度浮点格式

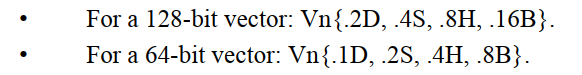

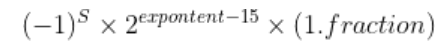

这里有两种格式一种是IEEE的格式,一种是ARM自定义的格式,其中FPCR.AHP控制AArch64 state, FPSCR.AHP控制AArch32 state.两种state下,16bit的半精度的格式相同都是

在这些值取不同的范围时,在架构上的取值有不同的定义:exponent为5位的二进制,其最大值为11111=0x1F

当0<expoent<0x1F 时该值为

这种格式下的最小值是:2的14次方 即 expontent 为1expo, S=0 fraction=0 等于6.104*10^-5

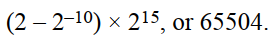

最大值为:

当exponent为0时,

当exponent = 0x1F时:(为什么?)

- 单精度浮点格式

- 双精度浮点格式

- BFloat16 floating-point format

- FIX-point format

主要用于浮点和定点间的转换,可以是sign或者unsign …

第三节:高级SIMD和浮点

在AArch32状态下,在SIMD和FP寄存器上运行的SIMD指令被描述为高级SIMD指令,以区别于在32位通用寄存器上运行的基本指令集,A64不提供任何在通用寄存器上运行的SIMD指令,因此,一些AARch64上描述的SIMD即指的是运行在SIMD寄存器和FP寄存器上的SIMD指令。

| AArch64 | AArch32 |

|---|---|

| 单精度,双精度 | 仅单精度 |

| 当FEAT_FP16配置时,可以有half-precision arithmetic | 当FEAT_FP16配置时,可以有half-precision arithmetic |

对于SIMD浮点计算指令,仍然遵从IEEE754浮点计算的规范:

- 非标准格式的会被flush to zero

- 只有默认格式的NaN会被支持

- 舍入到最近数的模式启用

- 未限制浮点异常处理用于所有的浮点异常

如何系统支持浮点异常trapping,例如溢出,除零,可以被处理without trapping,这可以应用于SIMD和浮点操作

在AArch64的状态下,以下这些寄存器用于控制浮点计算并返回浮点状态信息:

- FPCR

AHP用于控制半精度计算

DN用于控制NAN

{FZ,FZ16}用于控制Flush-to-ZERO的行为

Rmode用于控制Rounding mode

此外还有其他的异常tarp的控制寄存器field - FPSR(浮点状态寄存器)

累计浮点异常flag,AArch32 浮点异常flags

(1)SMID支持的指令

- 单个element的load和store,以及向量的多个element

- 数据处理指令

- 复数运算

- 不同精度浮点转换

- 浮点,定点,以及整数类型

- 浮点rounding

(2) 浮点的标准和术语

RM round toward Minus Infinity 向负无穷的舍入

RP round toward Plus Infinity 向正无穷的舍入

RZ 向0舍入

RN向最近舍入

(3)ARM标准的浮点输入和输出值

- input:

zeros,Nornalized number,denormalized的数据会被flush到0,NAN,无穷 - output:

zeros,normalized number, 小于最小值的数会被flush to zero,default NaN

(4)Flush to zero

暂不详述

(5)NaN handling and default NaN

暂不详述

(6)Round to odd mode

暂不详述

第四节 ARM memory model引言

ARM memory model 支持以下特性:

1.非对其地址访问产生异常

2.限制不同应用的访问权限

3.将VA转换为PA

4.切换大小端

5.控制访问memory的顺序

6.控制cache 和地址转换的结构

7.多个PE时对共享memory 的访问进行同步和协调

8.用于阻止投机访问的Barriers机制

虚拟地址的空间由AARCH64/32 以及EL0/1共同决定,不同的EL级别是分开控制的。PA(物理地址)是由实际设计决定的。

以下章节讲解了 AArch64的memory model:

B2(The AArch64 Application level model),

D4(The AArch64 System level memmory model),

D5(The AArch64 Virtual memory System Architecture)

总结

ARM spec 第一章主要是一些简介,包括对INT,SMID, FP 以及memory model 的目录式的介绍,可以理解为一本引言

![[游戏开发][Unity]Assetbundle加载篇(11)](/images/no-images.jpg)