首先,“嵌入式”这是个概念,没有准确的定义。但是主要思想是一样的,就是相比较PC机台式电脑这种通用系统来说,嵌入式系统是个系统可裁剪(基于OS(winCE、linux、vxworks等)),结构精简,在硬件和软件上都只保留需要的部分,而将不需要的部分裁去,实时性要求高???。所以嵌入式系统一般都具有便携、低功耗、性能单一等特性。如示波器,手机,平板电脑,全自动洗衣机,路由器、数码相机,这些设备中,虽然看不到台式机的存在,但是都有一个或多个嵌入式系统在工作。

然后,MCU、DSP、FPGA这些都属于嵌入式系统的范畴,是为了实现某一目的而使用的工具。

MCU经过这么多年的发展,早已不单单只有冯诺依曼/普林斯顿结构的51了,性能也已得到了很大的提升。因为MCU必须顺序执行程序,所以适于做控制,较多地应用于工业。

而ARM本是一家专门设计MCU的公司,由于技术先进加上策略得当,这两年独霸单片机市场。ARM的单片机有很多种类,从低端M0(小家电)到高端A8、A9(手机、平板电脑)都很吃香,所以也不是ARM的单片机不一定上操作系统。

单片机和DSP都有自己的精简指令集???,不加操作系统也可以跑。

DSP叫做数字信号处理器digital signal processor,它的结构与MCU不同,加快了运算速度(由于硬件乘法器和哈弗总线),突出了运算能力。可以把它看成一个超级快的MCU。低端的DSP,如C2000系列,主要是用在电机控制上,不过TI公司好像称其为DSC(数字信号控制器)一个介于MCU和DSP之间的东西。高端的DSP,如C5000/C6000系列,一般都是做视频图像处理和通信设备这些需要大量运算的地方。

为什么DSP硬件乘法器和哈弗总线运算速度快?

?????

FPGA叫做现场可编程逻辑阵列,本身没有什么功能,就像一张白纸,想要它有什么功能完全靠编程人员设计。你可以把它变成MCU,也可以变成DSP。由于MCU和DSP的内部结构都是设计好的,所以只能通过软件编程来进行顺序处理,而FPGA则可以并行处理和顺序处理???所以比较而言速度最快。

FPGA和CPLD的内部结构稍有不同。通常FPGA中的寄存器资源比较丰富,适介同步时序电路较多的数字系统;CPLD中的组合逻辑资源比较丰富,适合组合电路较多的控制应用。在这两类可编程逻辑器件中,CPLD提供的逻辑资源较少,而FPGA提供了最高的逻辑密度、丰富的特性和极高的性能。

fpga以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。

为什么MCU、DSP和FPGA会同时存在?

因为MCU、DSP的内部结构都是由IC设计人员精心设计的,在完成相同功能时功耗和价钱都比FPGA要低的多。而且FPGA的开发本身就比较复杂,完成相同功能耗费的人力财力也要多。所以三者之间各有各的长处,各有各的用武之地。但是目前三者之间已经有融合的态势,ARM的M4系列里多加了一个精简的DSP核,TI的达芬奇系列本身就是ARM+DSP结构,ALTERA和XINLIX新推出的FPGA都包含了ARM的核在里面。所以三者之间的关系是越来越像三基色的三个圆了。

一句话以蔽之“你中有我,我中有你”。

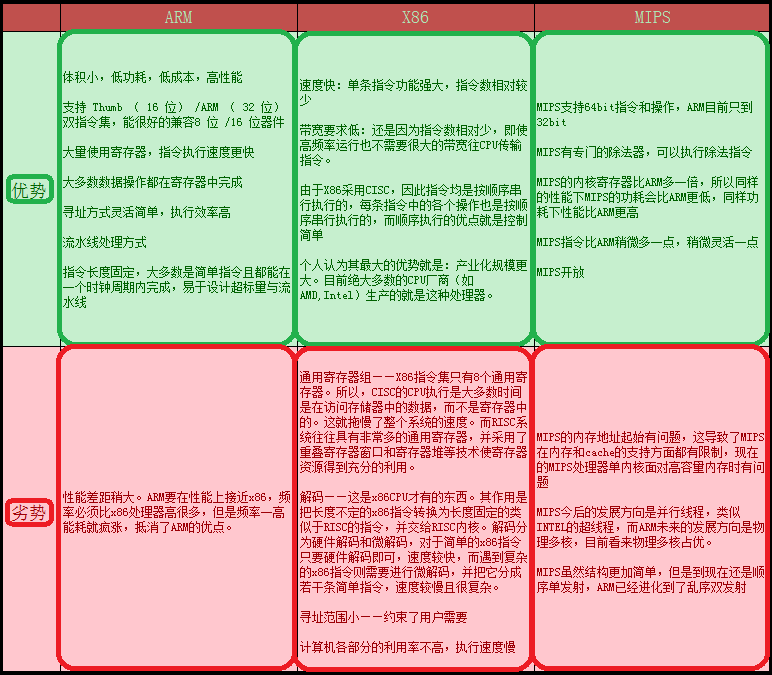

目前市面上的CPU指令集分类主要分有两大阵营,一个是intel、AMD为首的复杂指令集CPU,另一个是以IBM、ARM为首的精简指令集CPU。不同品牌的CPU,其产品的架构也不相同,例如,Intel、AMD的CPU是X86架构的,而IBM公司的CPU是PowerPC架构,ARM公司是ARM架构。

单片机通指8位、16位、32位CPU含常用外围设备如RAM、Timer、AD、UART等通信接口的控制器MCU,一般主频在100M以下,有几十个厂家生产,型号数万种。通常无操作系统,用于简单的控制,如电梯,空调等。

【硬核】如何从零打造一款操作系统,给单片机写个RTOS_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili https://www.bilibili.com/video/av58774412

80x86是intel公司的微处理器系列。

价格:Intel 奔腾 G4560报价500人民币;英特尔(Intel) i5 8400 酷睿六核报价1800人民币。

晶体管数量:8086有29K个晶体管;Pentium有3.1M个晶体管;Corei7有1.3亿个晶体管。

寄存器数量:8086有8个16位通用寄存器。后来扩展,8个32位的寄存器

The 80386 contains a total of sixteen registers that are of interest to the applications programmer. these registers may be grouped into these basic categories:

1. General registers. These eight 32-bit general-purpose registers are used primarily to contain operands for arithmetic and logical operations.

2. Segment registers. These special-purpose registers permit systems software designers to choose either a flat or segmented model of memory organization. These six registers determine, at any given time, which segments of memory are currently addressable.

3. Status and instruction registers. These special-purpose registers are used to record and alter certain aspects of the 80386 processor state.

在80x86 CPU中进行的所有计算几乎都和寄存器有关。例如,将两个变量相加,把它们的和存入第3个变量中,必须先将其中一个变量装入一个寄存器中,并将第2个操作数和寄存器的值相加,然后将寄存器中的值存入目的变量。寄存器在每次计算中都充当媒介。因此,在80x86汇编语言程序中寄存器是非常重要的。

逻辑运算单元:注意到x86上也有很多硬件运算资源(FPGA的主要资源),如ALU???

内存:“PC系列微机内存在性质上不完全一致”,80286有24根地址线,内存为2^24=16MB,80386有32根地址线,内存为2^32=4096MB,

CPU由运算器(ALU)、控制器(CU)和内部寄存器(R)三部分组成?

https://blog.csdn.net/the_scent_of_th_soul/article/details/51925440

控制器是全机的指挥中心,它负责把指令逐条从存储器中取出,经译码分析后向全机发出取数、执行、存数等控制命令,以完成程序所要求的功能。控制器包括以下几个部分:

a.指令寄存器IR:用来存放从存储器取出的将要执行的指令码。

b.指令译码器ID:对指令寄存器IR中的指令操作码字段进行译码,以确定该指令执行什么操作。指令通常由操作码和操作数两部分组成。操作码表示该指令完成的操作,操作数表示参加操作的数本身或操作数所在地址。

c.可编程逻辑阵列PLA:用于产生取指令和执行指令所需要的各种微操作控制信号,并经过控制总线CB送往有关部件,使计算机完成相应的操作。

---------------------

PC三种总线:

地址总线AB:在对存储器或I/O端口进行访问时,传送由CPU提供的要访问的存储单元或I/O端口的地址信息。AB是单向总线。

一个CPU有N根地址线,则可以说这个CPU的地址总线宽度为N,这样的CPU可以寻找2的N次方个内存单元。

数据总线DB:CPU与内存或其他器件之间的数据传送是通过数据总线来完成的,数据总线的宽度决定了CPU和外界的数据传送速度。8根数据总线一次可传送一个字节。8088CPU的数据总线宽度为8,8086CPU的数据总线宽度为16。例如,CPU想向内存中写入数据89D8。 因为8088要分两次传送,第一次传送D8,第二次传送89。8086可一次性将数据传入内存。DB是双向总线

控制总线CB:控制总线是一些不同的控制线的集合。有多少根控制总线就意味着CPU提供了对外部器件的多少种控制,控制总线的宽度决定了CPU对外部器件的控制能力。

“主存(内存)是x86CPU外的存储区域,堆栈是在主存(内存)中开辟的一片数据存储区”

推论:寄存器是CPU中的资源,没有地址??

“在x86列机中, 8086只有20根地址线, 直接寻址能力为2^20B=1MB, 物理地址编号从0~0FFFFF H。CPU与存储器交换信息必须使用20位的物理地址。 但是,8086 内部却是16位结构, 它里面与地址有关的寄存器全部都是16 位的,因此,它只能进行 16位地址运算, 表示16位地址, 寻找操作数的范围最多也只能是64KB。 为了能表示20位物理地址,8086 的设计人员提出了将主存分段使用的方案: 将 1MB 的存储器按64KB分段, 设置 4 个段寄存器保存当前可使用段的段首址。访问存储单元时,CPU选择某一适当的段寄存器,与本段中某一待访问存储单元的偏移地址相加, 则得到该单元的20位物理地址。寻找操作数的范围就可达到 1MB。

随着x86系列机的发展, 特别是32位CPU的推出, 它已能全面支持32位的数据、指令和寻址方式, 可访问 4GB 的存储空间。 但为了与8086兼容, 一直保留了主存的分段使用技术, 段寄存器也由4个增加至 6个并提供了实方式。”

DSP

DSP(digital signal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。其最大特点是内部有专用的硬件乘法器和哈佛总线结构对大量的数字信号处理的速度快。一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。根据数字信号处理的要求,DSP芯片一般具有如下主要特点:

(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

下图为DSP芯片典型结构,以及典型定点型乘法器data path

关键部件:乘法器、ALU、(移位)寄存器

注意DSP功能划分,其CPU中不包含存储和总线,core是什么???

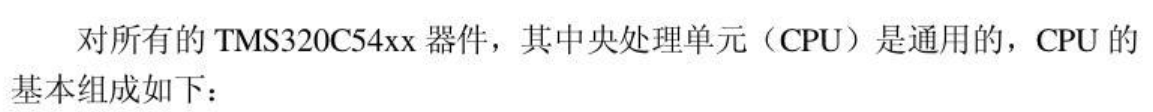

典型DSP的CPU参数(TI公司):

典型DSP芯片参数:

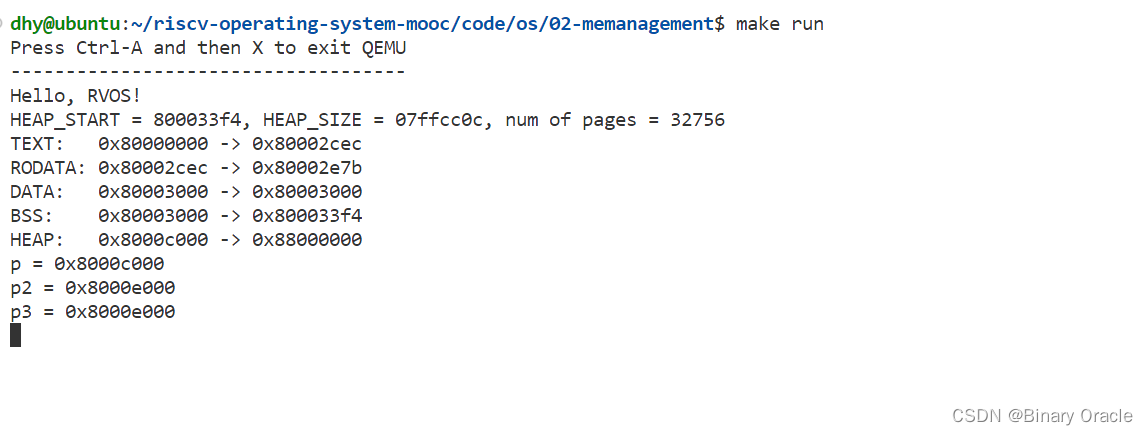

DSP存储:

存储空间使用权限:

DSP芯片兼容、一致性问题:同厂商产品可能兼容。

FPGA

Altera公司官网:https://www.intel.com/content/www/us/en/products/programmable.html,了解芯片、产品、配套软件、解决方案,及资料下载。

EEVblog #635 - FPGA vs 单片机_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili https://www.bilibili.com/video/av35690794

其他公司(Xilinx和Altera)FPGA芯片不同型号资源:

其中,基本单元分别为CLB(configurable logic block)和EAB(embedded array block)

在FPGA芯片上搭建一个处理器:《Advanced FPGA Design - Architecture, Implementation, and Optimization-IEEE (2007)》17章

FPGA是(Field ProgrammableGate Array)现场可编程门阵列的缩写,它是在PAL、GAL、PLD等可编程器件的基础上进一步发展的产物,是专用集成电路(ASIC)中集成度最高的一种。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(ConfigurableLogic Block)、输出输入模块IOB(InputOutput Block)和内部连线(Interconnect)三个部分。用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的逻辑。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。作为专用集成电路(ASIC)领域中的一种半定制电路,FPGA既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。可以毫不夸张的讲,FPGA能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用FPGA的在线修改能力,随时修改设计而不必改动硬件电路。使用FPGA来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。FPGA的编程无须专用的FPGA 编程器,只须用通用的EPROM、PROM编程器即可。当需要修改FPGA功能时,只需换一片EPROM即可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。因此,FPGA的使用非常灵活。可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。目前FPGA的品种很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FIEX系列等。2006年工艺达到65nm。

FPGA以并行运算为主,以硬件描述语言(Verilog 或 VHDL)来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别。

FPGA与指令集微处理器的区别:《Reconfigurable computing_ the theory and practice of FPGA-based computation(2007)》19章

FPGA通常与定制ASIC形成对比:

但是,如果由于应用要求或其他因素的变化而要求使用可编程解决方案,则必须仔细研究应用程序,以确定是否可以使用可编程处理器微处理器或DSP满足性能要求。可编程处理器的代码开发比FPGA或ASIC所需的工作量要小得多,因为用C语言或Java语言开发的软件比用Verilog或VHDL编写并行描述要少得多。

此外,可编程处理器的编码和调试环境要比它们的HDL对应环境丰富得多。微处理器通常也比FPGA便宜得多。如果微处理器能够满足应用要求(性能、功率等),它几乎总是最好的选择。

一般来说,fpgas非常适合于要求极高性能和可重编程性的应用,用于与许多其他设备(所谓的胶逻辑)通信的接口组件,以及用于实现批量硬件系统,使其规模经济可行。它们不太适合将以尽可能大的产量生产的产品,也不适合必须以尽可能小的功率运行的系统。

详解FPGA的四大设计要点

FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

早期的FPGA相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM构建而成,LE由LUT(查找表)和D触发器构成,RAM也往往容量非常小。

现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元,包括:

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPU core:分为2种,软core和硬core.软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

不过,FPGA还是有缺点。对于某些高主频的应用,FPGA就无能为力了。现在虽然理论上FPGA可以支持的500MHz,但在实际设计中,往往200MHz以上工作频率就很难实现了。

FPGA设计要点之一:时钟树

对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。

同步设计的第一个关键,也是关键中的关键,就是时钟树。

一个糟糕的时钟树,对FPGA设计来说,是一场无法弥补的灾难,是一个没有打好地基的大楼,崩溃是必然的。

具体一些的设计细则:

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心;

3)跨时钟域的信号一定要做同步处理。对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo.需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处。

5)对于特殊的IO接口,需要仔细计算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管脚可设置的delay等多种工具来实现。简单对管脚进行Tsu、Tco、Th的约束往往是不行的。

可能说的不是很确切。这里的时钟树实际上泛指时钟方案,主要是时钟域和PLL等的规划,一般情况下不牵扯到走线时延的详细计算(一般都走全局时钟网络和局部时钟网络,时延固定),和ASIC中的时钟树不一样。对于ASIC,就必须对时钟网络的设计、布线、时延计算进行仔细的分析计算才行。

FPGA设计要点之二:FSM

FSM:有限状态机。这个可以说是逻辑设计的基础。几乎稍微大一点的逻辑设计,几乎都能看得到FSM.

FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。实际使用中大部分都采用merly型。

FSM通常有2种写法:单进程、双进程。

初学者往往喜欢单进程写法,格式如下:

always @( posedge clk or posedge rst )beginif ( rst == 1'b1 )FSM_status <= ……;elsecase( FSM_status )……;endcaseend简单的说,单进程FSM就是把所有的同步、异步处理都放入一个always中。

优点:

1)看起来比较简单明了,写起来也不用在每个case分支或者if分支中写全对各个信号和状态信号的处理。也可以简单在其中加入一些计数器进行计数处理。

2)所有的输出信号都已经是经过D触发器锁存了。

缺点:

1)优化效果不佳。由于同步、异步放在一起,编译器一般对异步逻辑的优化效果最好。单进程FSM把同步、异步混杂在一起的结果就是导致编译器优化效果差,往往导致逻辑速度慢、资源消耗多。

2)某些时候需要更快的信号输出,不必经过D触发器锁存,这时单进程FSM的处理就比较麻烦了。

双进程FSM,格式如下:

always @( posedge clk or posedge rst )beginif ( rst == 1'b1 )FSM_status_current <= …;elseFSM_status_current <= FSM_status_next;always @(*)begincase ( FSM_status_current )FSM_status_next = ……;endcaseend

从上面可以看到,同步处理和异步处理分别放到2个always中。其中FSM状态变量也采用2个来进行控制。双进程FSM的原理我这里就不多说了,在很多逻辑设计书中都有介绍。这里描述起来太费劲。

优点:

1)编译器优化效果明显,可以得到很理想的速度和资源占用率。

2)所有的输出信号(除了FSM_status_current)都是组合输出的,比单进程FSM快。

缺点:

1)所有的输出信号(除了FSM_status_current)都是组合输出的,在某些场合需要额外写代码来进行锁存。

2)在异步处理的always中,所有的if、case分支必须把所有的输出信号都赋值,而且不能出现在FSM中的输出信号回送赋值给本FSM中的其他信号的情况,否则会出现 latch.

latch会导致如下问题:

1)功能仿真结果和后仿不符;

2)出现无法测试的逻辑;

3)逻辑工作不稳定,特别是latch部分对毛刺异常敏感;

4)某些及其特殊的情况下,如果出现正反馈,可能会导致灾难性的后果。

这不是恐吓也不是开玩笑,我就亲眼见过一个小伙把他做的逻辑加载上去后,整个FPGA给炸飞了。后来怀疑可能是出现正反馈导致高频振荡,最后导致芯片过热炸掉(这个FPGA芯片没有安装散热片)。

FPGA设计要点之三:latch

首先回答一下:

1)stateCAD没有用过,不过我感觉用这个东东在构建大的系统的时候似乎不是很方便。也许用systemC或者system Verilog更好一些。

2)同步、异步的叫法是我所在公司的习惯叫法,不太对,不过已经习惯了,呵呵。

这次讲一下latch.

latch的危害已经说过了,这里不再多说,关键讲一下如何避免。

1)在组合逻辑进程中,if语句一定要有else!并且所有的信号都要在if的所有分支中被赋值。

always @( * ) beginif ( sig_a == 1'b1 ) sig_b = sig_c;end这个是绝对会产生latch的。正确的应该是always @( * ) beginif ( sig_a == 1'b1 ) sig_b = sig_c;else sig_b = sig_d;end

另外需要注意,下面也会产生latch.也就是说在组合逻辑进程中不能出现自己赋值给自己或者间接出现自己赋值给自己的情况。

always @( * ) beginif ( rst == 1'b1 ) counter = 32'h00000000;else counter = counter + 1;end

但如果是时序逻辑进程,则不存在该问题。

2)case语句的default一定不能少!

原因和if语句相同,这里不再多说了。

需要提醒的是,在时序逻辑进程中,default语句也一定要加上,这是一个很好的习惯。

3)组合逻辑进程敏感变量不能少也不能多。

这个问题倒不是太大,verilog2001语法中可以直接用 * 搞定了。

顺便提一句,latch有弊就一定有利。在FPGA的LE中,总存在一个latch和一个D触发器,在支持DDR的IOE(IOB)中也存在着一个latch来实现DDIO.不过在我们平时的设计中,对latch还是要尽可能的敬而远之。

FPGA设计要点之四:逻辑仿真

仿真是FPGA设计中必不可少的一步。没有仿真,就没有一切。

仿真是一个单调而繁琐的工作,很容易让人产生放弃或者偷工减料的念头。这时一定要挺住!

仿真分为单元仿真、集成仿真、系统仿真。

单元仿真:针对每一个最小基本模块的仿真。单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%!这三种覆盖率都可以通过MODELSIM来查看,不过需要在编译该模块时要在Compile option中设置好。

集成仿真:将多个大模块合在一起进行仿真。覆盖率要求尽量高。

系统仿真:将整个硬件系统合在一起进行仿真。此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。系统仿真是逻辑设计的一个大分支,是一门需要专门学习的学科。

ARM

全世界99%的智能手机和平板电脑都采用ARM架构。ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,一个英国的芯片设计公司,但是不生产芯片。只卖知识产权。设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备市场占有90%以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。ARM是32位的单片机,其内部硬件资源的性能较高,可以加载操作系统成为其主要特点,有了操作系统,就可以像pc机那样多任务实时处理,就是同一时间内能完成多个任务,而且不会互相影响。 ARM公司在经典处理器ARM11以后的产品改用Cortex命名。

例如:iPhone 5s,CPU是A7

寄存器有6000多位(31个64位寄存器,加上32个128位寄存器)

iPhone 5s的内存是1GB,约为80亿位(bit)。这意味着,高性能、高成本、高耗电的设计可以用在寄存器上,反正只有6000多位,而不能用在内存上。因为每个位的成本和能耗只要增加一点点,就会被放大80亿倍。

ARM微处理器的在较新的体系结构中支持两种指令集:ARM指令集和Thumb指令集。其中,ARM指令为32位的长度,Thumb指令为16位长度。Thumb指令集为ARM指令集的功能子集,但与等价的ARM代码相比较,可节省30%~40%以上的存储空间,同时具备32位代码的所有优点。

系统的工作频率在很大程度上决定了ARM微处理器的处理能力。ARM7系列微处理器的典型处理速度为0.9MIPS/MHz,常见的ARM7芯片系统主时钟为20MHz-133MHz,ARM9系列微处理器的典型处理速度为1.1MIPS/MHz,常见的ARM9的系统主时钟频率为100MHz- 233MHz,ARM10最高可以达到700MHz.不同芯片对时钟的处理不同,有的芯片只需要一个主时钟频率,有的芯片内部时钟控制器可以分别为ARM 核和USB、UART、DSP、音频等功能部件提供不同频率的时钟。

单片机(以51为例)

“51单片机是对所有兼容Intel 8031指令系统的单片机的统称。该系列单片机的始祖是Intel的8004单片机,后来随着Flash rom技术的发展,8004单片机取得了长足的进展,成为应用最广泛的8位单片机之一,其代表型号是ATMEL公司的AT89系列,它广泛应用于工业测控系统之中。很多公司都有51系列的兼容机型推出,今后很长的一段时间内将占有大量市场。51单片机是基础入门的一个单片机,还是应用最广泛的一种。需要注意的是51系列的单片机一般不具备自编程能力。”

8051:第二代单片机代表,属MCS-51系列;AT89C51:是ATMEL公司推出的与MCS-51兼容的单片机,为第三代单片机。

MCS-51单片机是指美国Intel公司生产的一系列单片机的总称。这一系列包含8031 8051 8751 8032 8052 8752。8051单片机是最早也是最典型的产品。而AT89C51是以8051的核心电路为基础后来由ATMEL开发出来的,还有类似的STC51单片机,功能都是一样的只不过生产公司不同因而冠以的前面英文字母不同。就是说8051与AT89C51功能是完全一样的,不过8051是不是市面上已经不出售了。

ROM、RAM、flash、时钟晶振、接口资源

“”

PC、单片机、DSP、FPGA、ARM 对比

区别:

ARM具有比较强的事务管理功能,可以用来跑界面以及应用程序等,其优势主要体现在控制方面;ARM是32位的单片机,其内部硬件资源的性能较高,可以加载操作系统成为其主要特点,有了操作系统,就可以像pc机那样多任务实时处理,就是同一时间内能完成多个任务,而且不会互相影响。

DSP主要是用来计算的,比如进行加密解密、调制解调等,优势是强大的数据处理能力和较高的运行速度;

FPGA可以用VHDL或verilog HDL来编程,灵活性强,由于能够进行编程、除错、再编程和重复操作,因此可以充分地进行设计开发和验证。当电路有少量改动时,更能显示出FPGA的优势,其现场编程能力可以延长产品在市场上的寿命,而这种能力可以用来进行系统升级或除错。

DSP VS FPGA

DSP是通用的信号处理器,用软件实现数据处理;FPGA用硬件实现数据处理。DSP成本低,算法灵活,功能性强,而FPGA的实时性好,成本较高,FPGA适合于控制功能算法简单且含有大量重复计算的工程使用,DSP适合于控制功能复杂且含有大量计算任务的工程应用。

DSP是软件实现算法,FPGA是硬件实现算法,所以FPGA的处理速度会更高;FPGA比DSP快的一个重要原因是FPGA可以实现并行运算,而DSP由于硬件结构条件限制,主要还是依靠软件来提取指令执行,理解为还是串行执行的【大嘴说说:DSP所谓的并行执行主要还是得自己开通软件流水,或者说是自己写并行代码,而非硬件结构本身】。

集成电路设计等级:

应用对于芯片的不同要求

手机、台式电脑、服务器、集群式计算机、嵌入式

MSP430系列单片机是美国德州仪器(TI)1996年开始推向市场的一种16位超低功耗、具有精简指令集(RISC)的混合信号处理器(Mixed Signal Processor)。MSP430单片机称之为混合信号处理器,是由于其针对实际应用需求,将多个不同功能的模拟电路、数字电路模块和微处理器集成在一个芯片上,以提供“单片机”解决方案。该系列单片机多应用于需要电池供电的便携式仪器仪表中。

参考文献:

1、《80x86汇编语言程序设计教程(清华黑皮版)》;

2、[80X86汇编语言程序设计].王元珍.文字版

3、《DSP-Processor-Fundamentals-Architectures-and-Features》

4、《深入理解计算机系统》第三版 第四章

5、《新概念51单片机C语言教程.入门、提高、开发》

6、《DOS原理与结构》

7、《INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986》

8、《Dsp-Digital-Signal-Processing-With-Fpga》

9、《DSP-Processor-Fundamentals-Architectures-and-Features》

10、《Advanced FPGA Design - Architecture, Implementation, and Optimization-IEEE (2007)》

11、《Reconfigurable computing_ the theory and practice of FPGA-based computation(2007)》

12、《计算机体系结构—量化研究方法(第5版) - Computer Architecture_ A Quantitative Approach. 5-Elsevier (2011)》

13、https://mp.weixin.qq.com/s/A6E9vDE2Ga7ipR3ivP0iCw 详解FPGA的四大设计要点

14、ARM Cortex-A系列(A53、A57、A73等)处理器性能分类与对比_夜风的博客-CSDN博客_cortex-a53 https://blog.csdn.net/u014470361/article/details/85988772

| 价格rmb | 速度指标(MIPS百万条指令每秒,晶振频率) | 寄存器 | 存储器 | 应用 | 特色 | 功耗/芯片寿命 | |

| 80x86 | PC | 冯诺依曼结构 | |||||

| ARM | 主频百M~几G | 手机、平板电脑 | 哈佛总线 | 比x86功耗低 | |||

| DSP | 50~200MIPS | 图像处理 | |||||

| 8051 | 1~10MIPS | 工业控制 | |||||

| FPGA | flash,EEPROM | 原型设计,相对ASIC价格低 | FPGA对半导体产业最大的贡献创立了无生产线(Fabless)模式 | FPGA功耗高/CPLD相对功耗低 |

MIPS计算公式:

如果说的是CPU、GPU这样的芯片,寿命其实是非常长的,但它也不是一个可以永久工作的芯片,因为即使是在正常使用中,CPU中的电子通过动能不断冲击着电路中的金属原子,这个过程中会导致其一小部分脱离,也就是常说的“电子迁移”。尽管很长一段时间来看这种影响很微小,但是随着CPU工作时间的增长,电子迁移就会开始导致电路变形,发生短路漏电和干扰等现象,再接下来可能就会导致CPU运算出错、功能异常进而彻底报销。电子迁移现象会随着CPU工作频率和工作温度的提高更加严重,也就是说为了CPU的寿命和稳定,厂商一般不推荐用户对CPU芯片大幅度超频,超频所带来的频率增加和温度提高都会折损CPU的寿命。对于品质合格的CPU芯片来说8-10年。

如果说是SSD上用的闪存芯片,那就有相对有限的寿命了,闪存芯片主要分为SLC、MLC和TLC三种,SLC寿命最长,速度最快,但是成本最高,TLC则相反。闪存的寿命磨损就在于闪存单元的写入-擦除,一般来说,SLC闪存可进行100000次写入-擦除循环,MLC可进行10000次左右。不要觉得可怕,得益于越来越先进的主控芯片,日常使用下正常的闪存芯片没那么容易用坏,即使是TLC闪存,寿命达到8年以上也没有问题,使用几年后一般都会掉速,不过实际影响并不大。其实相比闪存芯片,SSD上的主控反而更有可能先坏掉。所以我们不用太在意闪存芯片的寿命,一般在你换下一个SSD或者手机时,它就直接淘汰掉了。不过对于7*24小时工作的服务器来说,非常不建议用SSD,因为在这种高强度工作环境下的闪存芯片寿命会大打折扣,即使是机械硬盘,用个两三年挂掉的几率也很高。

至于电脑上的内存芯片(RAM),由于其电容存储机制,只要是正常没有缺陷的芯片,寿命非常长,要不然绝大多数内存条都是终身保,只要不是不当超频,静电损坏,人为破坏,正常的内存寿命几乎不用担心。

其实相比电脑各类芯片的寿命,我们更应该关心主板和显卡上电容电感的寿命,电源的品质和整体散热水平,这些往往才是影响电脑寿命的关键。