1、高速电路DDR信号和设计例程和原理图

2、DDR3信号组控制

其实从外观上就可以看出来小张的内存条由很多海力士的内存颗粒组成。从内存控制器到内存颗粒内部逻辑,笼统上讲从大到小为:channel>DIMM>rank>chip>bank>row/column,如下图:

一个现实的例子是:

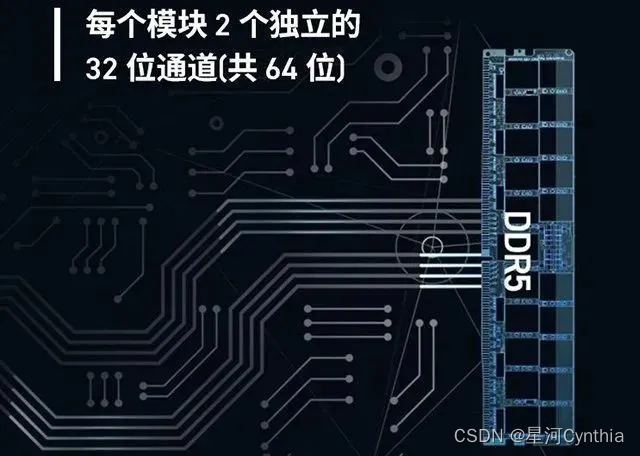

在这个例子中,一个i7 CPU支持两个Channel(双通道),每个Channel上可以插两个DIMM,而每个DIMM由两个rank构成,一个rank由8个chip组成。由于现在多数内存颗粒的位宽是8bit,而CPU带宽是64bit,所以经常是8个颗粒可以组成一个rank。所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒(为啥我们以后讲)。由于整个内存是4GB,我们可以算出单个内存颗粒是256MB。

这次我们来看看rank和Chip里面有什么,如下图:

这是个DDR3一个Rank的示意图。我们把左边128MB Chip拆开来看,它是由8个Bank组成,每个Bank核心是个一个存储矩阵,就像一个大方格子阵。这个格子阵有很多列(Column)和很多行(Row),这样我们想存取某个格子,只需要告知是哪一行哪一列就行了,这也是为什么内存可以随机存取而硬盘等则是按块存取的原因。

实际上每个格子的存储宽度是内存颗粒(Chip)的位宽,在这里由8个Chip组成一个Rank,而CPU寻址宽度是64bit,所以64/8=8bit,即每个格子是1个字节。选择每个格子也不是简单的两组信号,是由一系列信号组成,以这个2GB DDR3为例:

电源、地、配置信号的功能很简单,在此不赘述。控制信号主要是用来完成DDR4与DDR4 Controller之间的状态切换。DDR4中最重要的信号就是地址信号和数据信号。

3、DDR3信号组-知乎

CAS#和RAS#只有一根信号线。实际上每个格子的存储宽度是内存颗粒(Chip)的位宽,在这里由8个Chip组成一个Rank,而CPU寻址宽度是64bit,所以64/8=8bit,即每个格子是1个字节。选择每个格子也不是简单的两组信号,是由一系列信号组成,以这个2GB DDR3为例:

1. 片选(Chip Select)信号,S0#和S1#,每个用于选择是哪个Rank。

2. Bank地址线,BA0-BA2, 2^3=8,可以选择8个Bank

3. 列选 (Column Address Select), CAS#,用于指示现在要选通列地址。

4. 行选(Row Address Select),RAS#用于指示现在要选通行地址。

5. 地址线,A0-A13,用于行和列的地址选择(可并不都用于地址,本处忽略)。

6. 数据线,DQ0-DQ63,用于提供全64bit的数据。

7. 命令,COMMAND,用于传输命令,如读或者写等等。

注意这里没有内存颗粒的选择信号线,只有Rank的选择信号。在Rank选择好后,8个内存颗粒一起被选中,共提供64bit的数据。

读取和写入数据也稍微复杂点,简单来说分为以下三步:

1. 行有效。RAS#低电平,CAS#高电平。意味着现在行地址有效,同时在A0-A13传送地址信号,即2^13个Row可以选择。

2. 列有效。RAS#高电平,CAS#低电平。意味着列地址有效,这时在A0-A13上传送的是列地址。没错,A0-A13是行列共用的,所以每个格子选择需要有1和2两步才能唯一确定。

3. 数据读出或写入。根据COMMAND进行读取或者写入。在选定好小方格后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。