XC7VX690T-2FFG1761_PCIe 系列之三

关键词:PCIE FPGA Virtex-7 XC7VX690T XILINX DMA

参考资料:

UG475 - 7 Series FPGAs Packaging and Pinout Product SpecificationsUser Guide( ver1.15, 26062 KB ) [PDF]

UG476 - 7 Series FPGAs GTX/GTH Transceivers UserGuide ( ver1.12, 13883 KB ) [PDF]

PG023 - Virtex-7 FPGA Gen3 Integrated Block for PCIExpress v4.3 LogiCORE IP Product Guide (PG023),Virtex-7 FPGA Gen3 IntegratedBlock for PCI Express v4.2 LogiCORE IP Product Guide(PG023) ( ver4.3, 5788 KB ) [PDF]

PG054 - 7 Series FPGAs Integrated Block for PCIExpress v3.3 Product Guide (PG054) ( ver3.3, 9635 KB ) [PDF]

PG055 - AXI Memory Mapped to PCI Express (PCIe) Gen2v2.8 Product Guide (PG055) ( ver2.8, 2290 KB ) [PDF]

PG168 - 7 Series FPGAs Transceivers Wizard v3.6Product Guide ( ver3.6, 11604 KB )[PDF]

PG194 - AXI Bridge for PCI Express Gen3 Subsystemv3.0 Product Guide( ver3.0, 2943 KB ) [PDF]

PG195 - DMA Subsystem for PCI Express v4.0 ProductGuide ( ver4.0, 2244 KB ) [PDF]

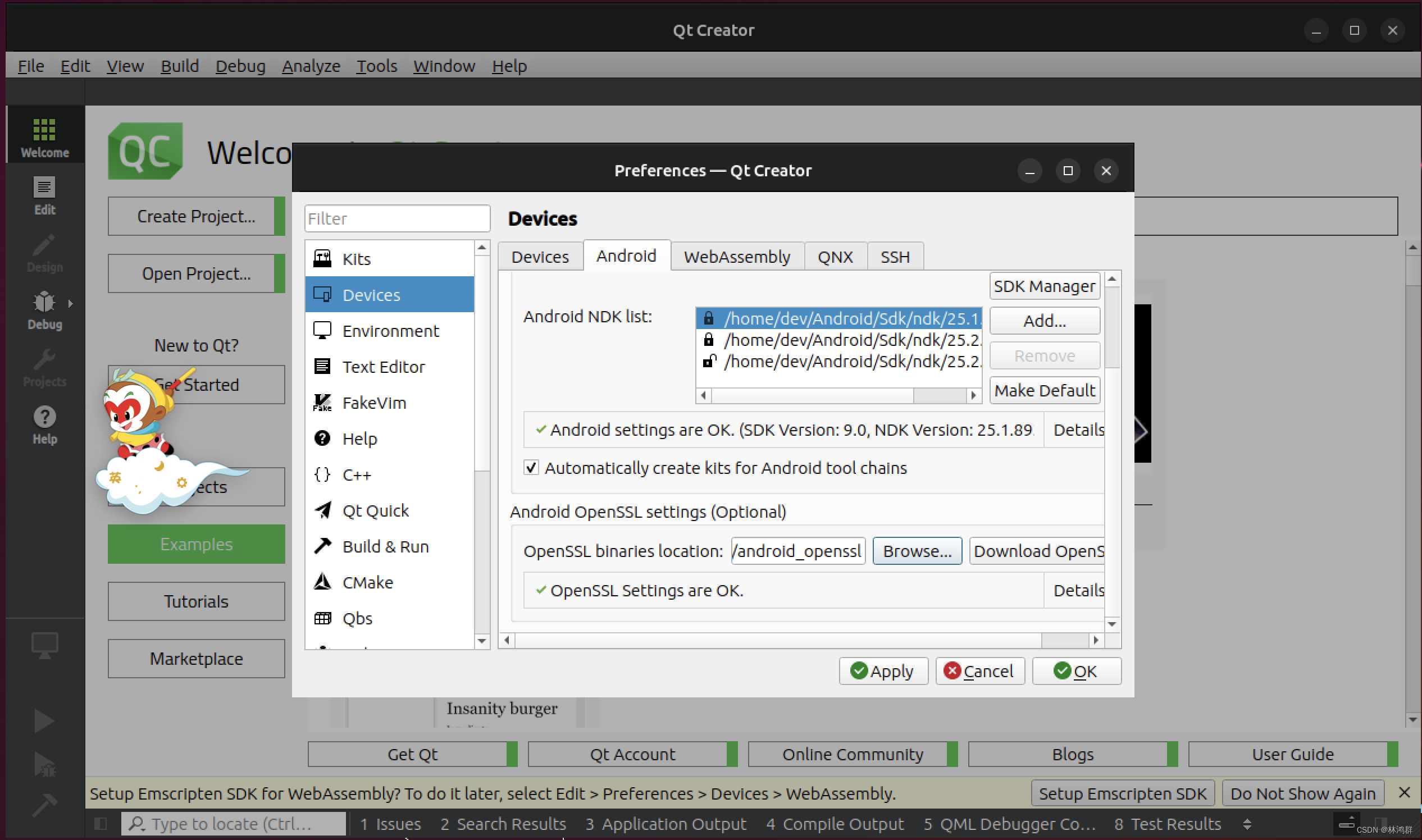

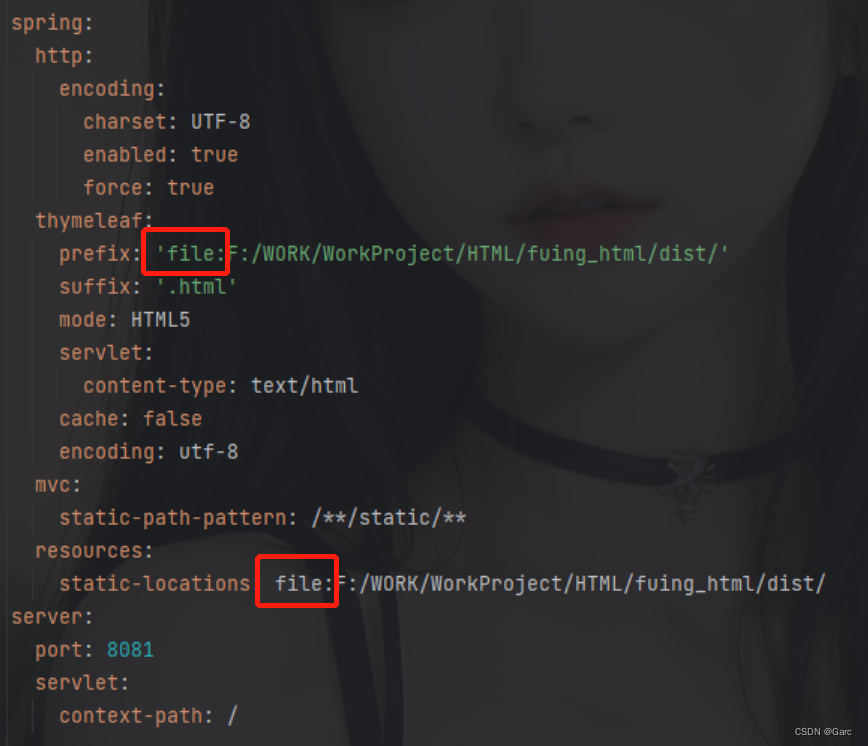

3、XC7VX690T-2FFG1761 PCIEcore

4、XC7VX690T-2FFG1761 3个PCIE core的约束文件

##-----------------------------------------------------------------------------

##

## Project :Virtex-7 FPGA Gen3 Integrated Block for PCI Express

## File :design_1_pcie3_7x_0_0-PCIE_X0Y0.xdc

## Version : 4.2

#

###############################################################################

# User Time Names / User Time Groups / Time Specs

###############################################################################

###############################################################################

# User Physical Constraints

###############################################################################

###############################################################################

# Pinout and Related I/O Constraints

###############################################################################

#

# Transceiver instance placement. This constraint selects the

# transceivers to be used, which also dictates the pinoutfor the

# transmit and receive differential pairs. Please refer to the

# Virtex-7 GT Transceiver User Guide (UG) for moreinformation.

#

###############################################################################

# PCIe Lane 0

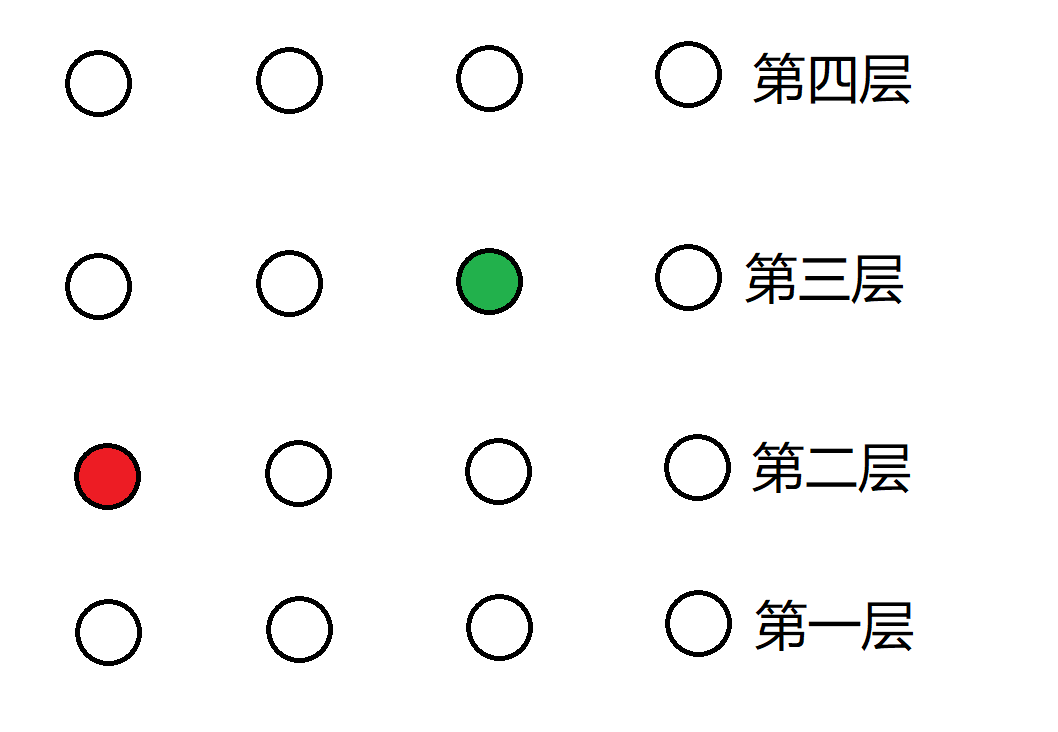

set_property LOC GTHE2_CHANNEL_X1Y11 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[0].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 1

set_property LOC GTHE2_CHANNEL_X1Y10 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[1].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 2

set_property LOC GTHE2_CHANNEL_X1Y9 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[2].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 3

set_property LOC GTHE2_CHANNEL_X1Y8 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[3].gt_wrapper_i/gth_channel.gthe2_channel_i}]

###############################################################################

#

# PCI Express Block placement. This constraint selects thePCI Express

# Block to be used.

#

###############################################################################

set_property LOCPCIE3_X0Y0 [get_cells pcie_top_i/pcie_7vx_i/PCIE_3_0_i]

##-----------------------------------------------------------------------------

##

## Project :Virtex-7 FPGA Gen3 Integrated Block for PCI Express

## File :design_1_pcie3_7x_1_0-PCIE_X0Y1.xdc

## Version : 4.2

#

###############################################################################

# User Time Names / User Time Groups / Time Specs

###############################################################################

###############################################################################

# User Physical Constraints

###############################################################################

###############################################################################

# Pinout and Related I/O Constraints

###############################################################################

#

# Transceiver instance placement. This constraint selects the

# transceivers to be used, which also dictates the pinoutfor the

# transmit and receive differential pairs. Please refer to the

# Virtex-7 GT Transceiver User Guide (UG) for moreinformation.

#

###############################################################################

# PCIe Lane 0

set_property LOC GTHE2_CHANNEL_X1Y23 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[0].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 1

set_property LOC GTHE2_CHANNEL_X1Y22 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[1].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 2

set_property LOC GTHE2_CHANNEL_X1Y21 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[2].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 3

set_property LOC GTHE2_CHANNEL_X1Y20 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[3].gt_wrapper_i/gth_channel.gthe2_channel_i}]

###############################################################################

#

# PCI Express Block placement. This constraint selects thePCI Express

# Block to be used.

#

###############################################################################

set_property LOCPCIE3_X0Y1 [get_cells pcie_top_i/pcie_7vx_i/PCIE_3_0_i]

## Project :Virtex-7 FPGA Gen3 Integrated Block for PCI Express

## File :design_1_pcie3_7x_2_0-PCIE_X0Y2.xdc

## Version : 4.2

#

###############################################################################

# User Time Names / User Time Groups / Time Specs

###############################################################################

###############################################################################

# User Physical Constraints

###############################################################################

###############################################################################

# Pinout and Related I/O Constraints

###############################################################################

#

# Transceiver instance placement. This constraint selects the

# transceivers to be used, which also dictates the pinoutfor the

# transmit and receive differential pairs. Please refer to the

# Virtex-7 GT Transceiver User Guide (UG) for moreinformation.

#

###############################################################################

# PCIe Lane 0

set_property LOC GTHE2_CHANNEL_X1Y35 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[0].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 1

set_property LOC GTHE2_CHANNEL_X1Y34 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[1].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 2

set_property LOC GTHE2_CHANNEL_X1Y33 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[2].gt_wrapper_i/gth_channel.gthe2_channel_i}]

# PCIe Lane 3

set_property LOC GTHE2_CHANNEL_X1Y32 [get_cells{gt_top_i/pipe_wrapper_i/pipe_lane[3].gt_wrapper_i/gth_channel.gthe2_channel_i}]

###############################################################################

#

# PCI Express Block placement. This constraint selects thePCI Express

# Block to be used.

#

###############################################################################

set_property LOC PCIE3_X0Y2 [get_cellspcie_top_i/pcie_7vx_i/PCIE_3_0_i]

###############################################################################