最近准备绘制xilinx的xc7z020clg400-2电路,需要准备前期的引脚、封装、电路的资料,再此汇总便于查阅。

主要参考:

···········1. ug865-Zynq-7000-Pkg-Pinout

···········2. ug933

···········3. ds187

···········4. ug471

补充与更新:2022.11 ----- 15.LVDS接口使用时注意事项

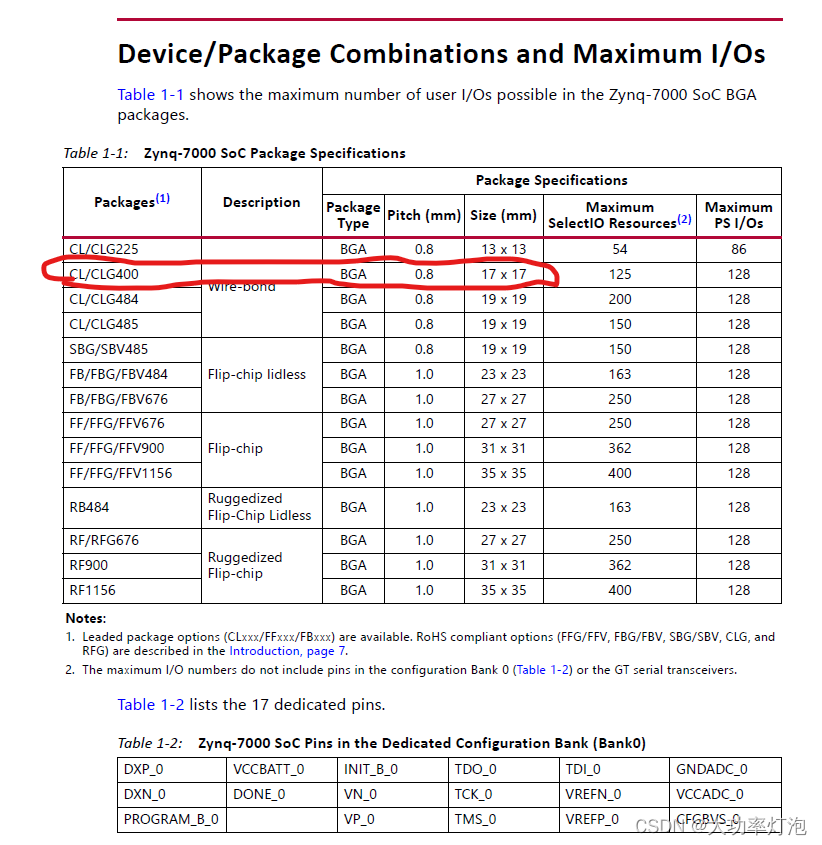

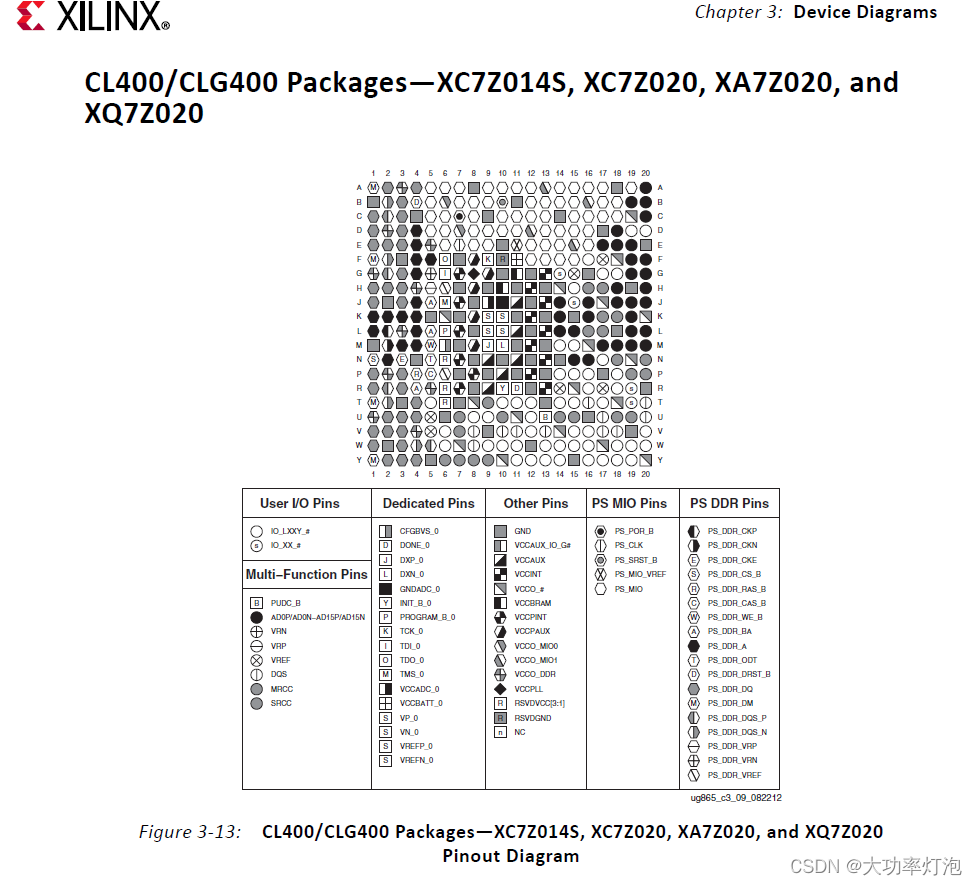

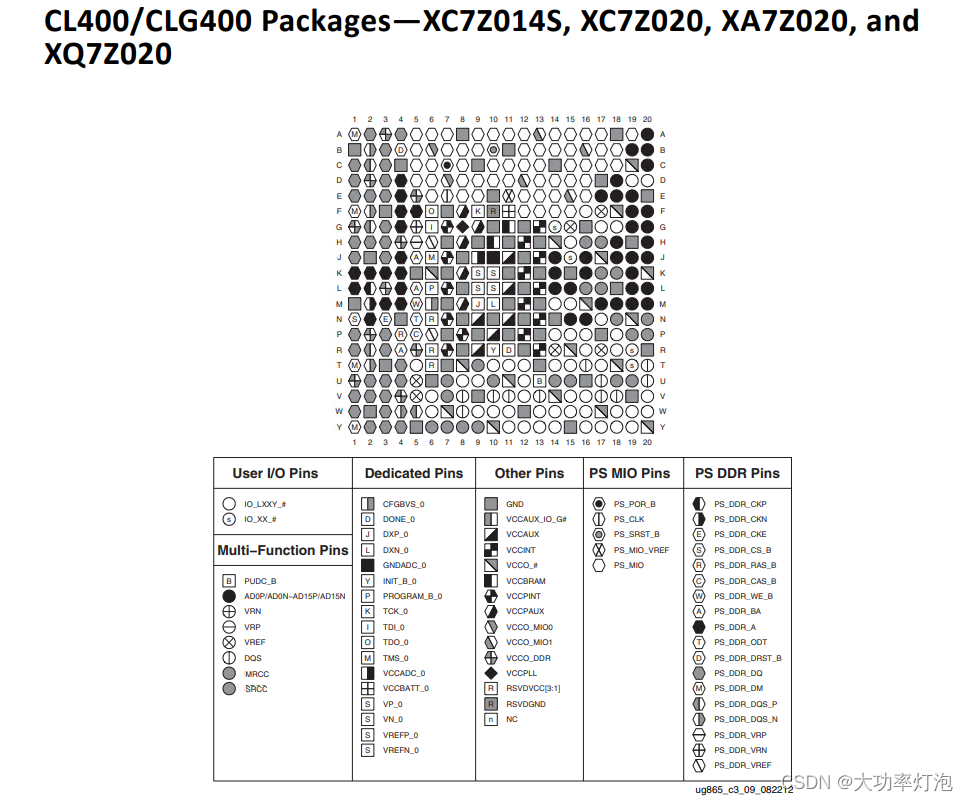

1. 封装预览

2. 焊球尺寸与chip尺寸

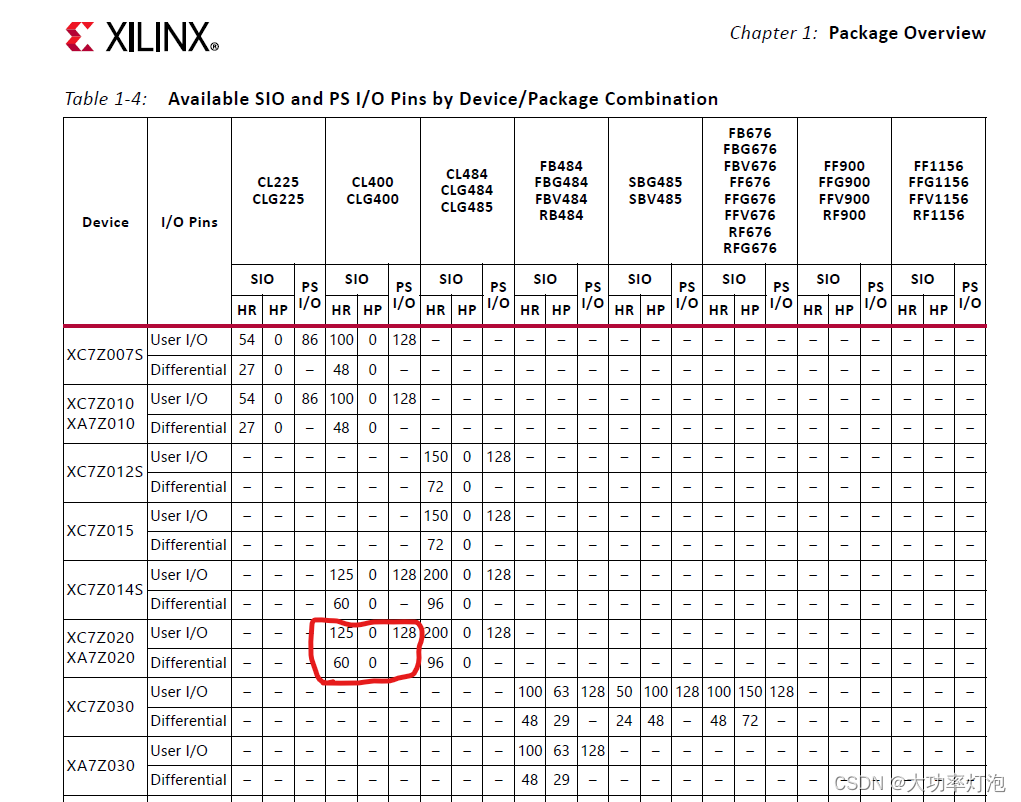

3. IO overview

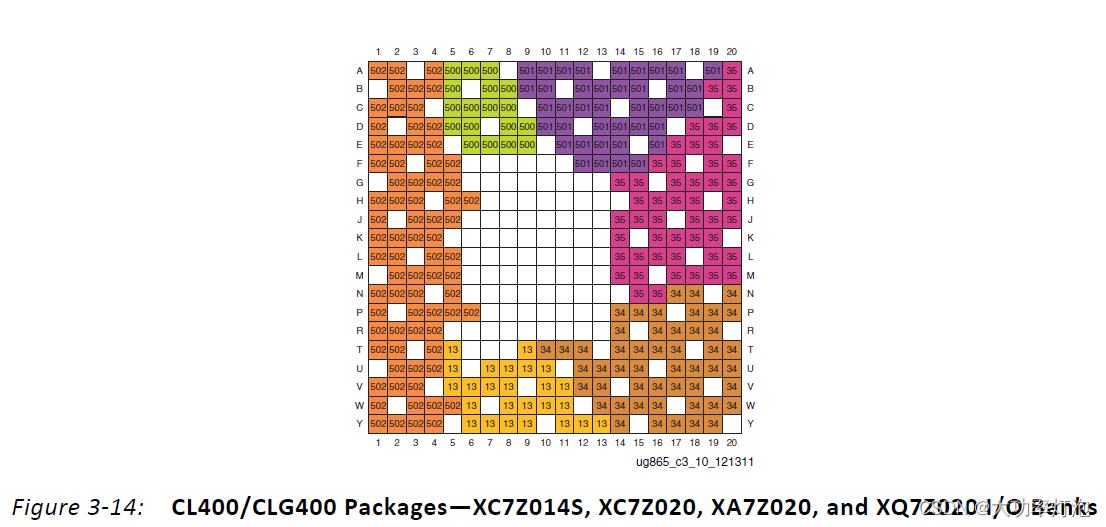

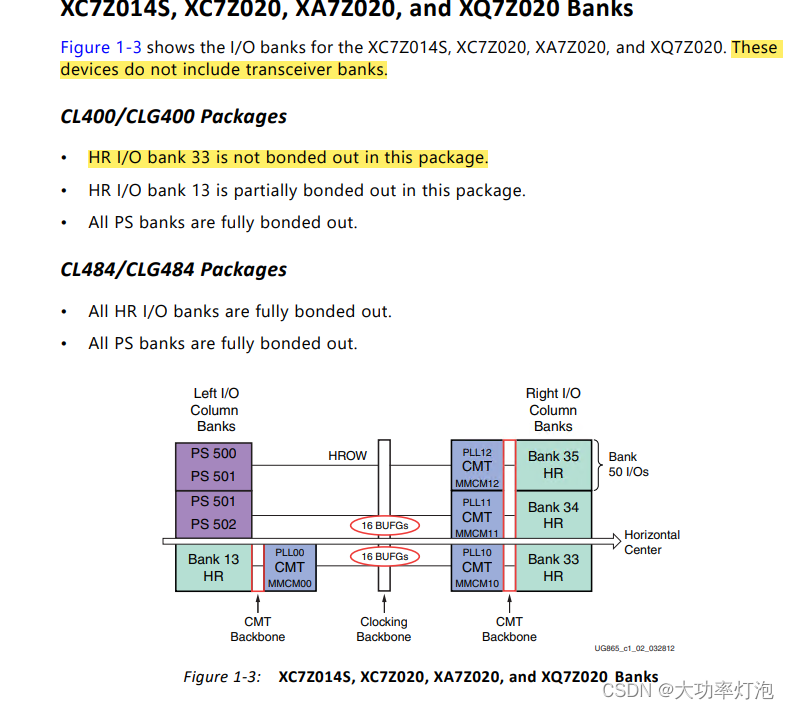

4. IO bank

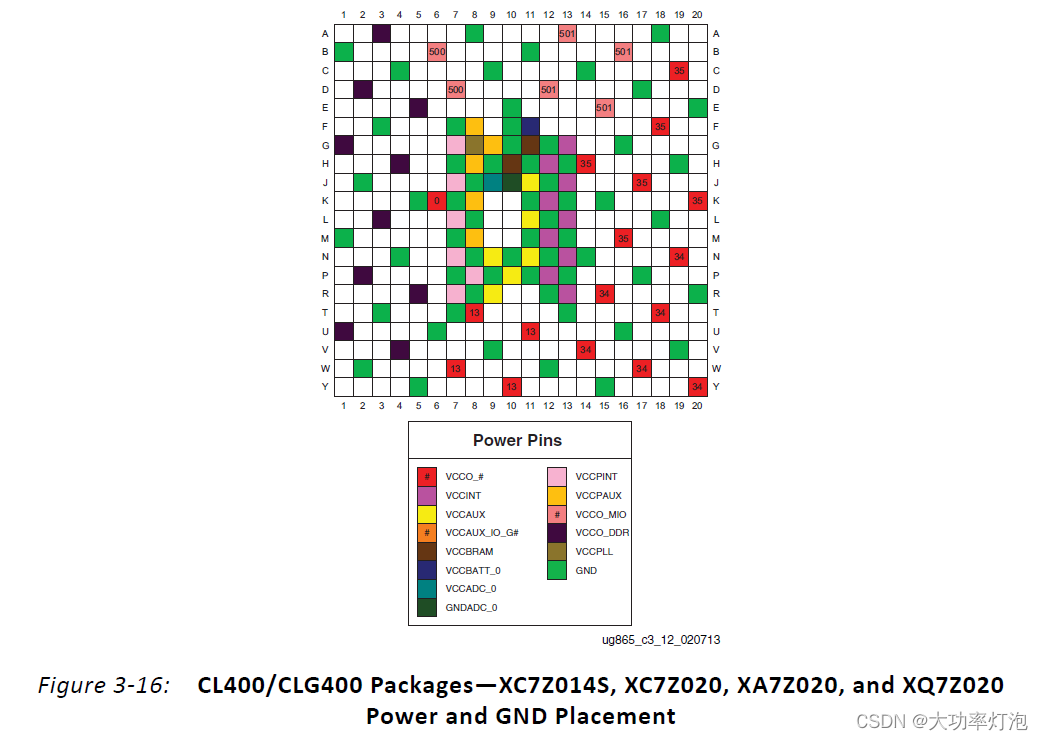

5. power IOs

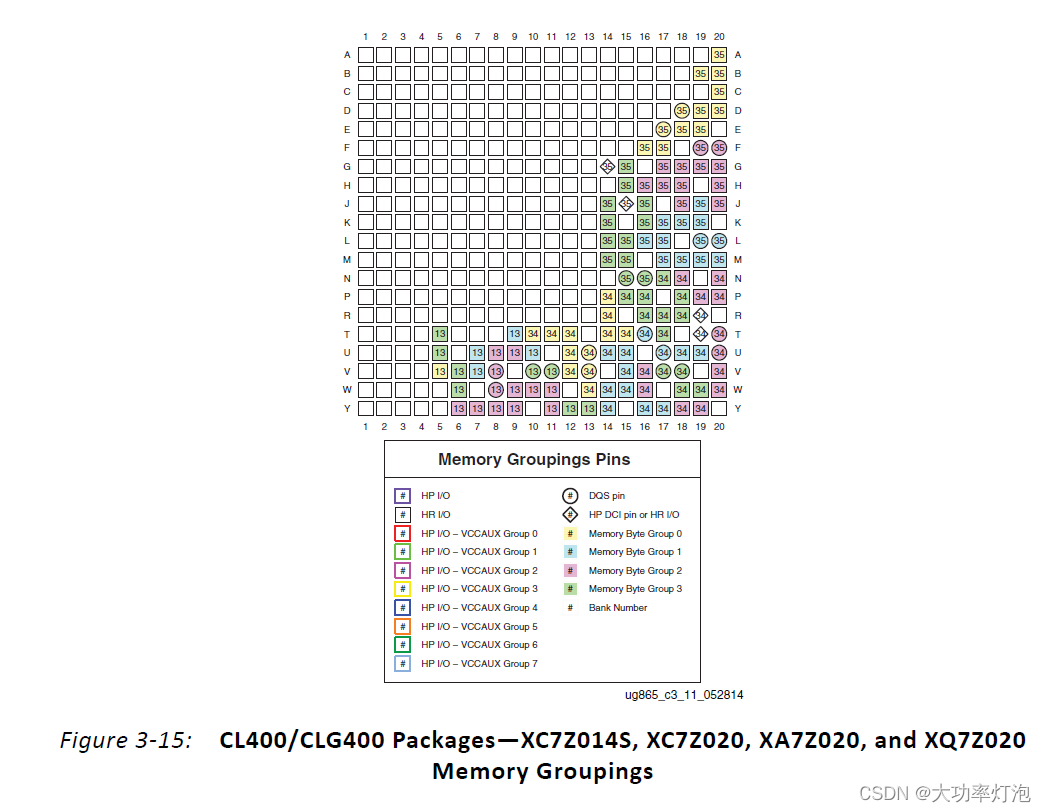

6. memory IOs

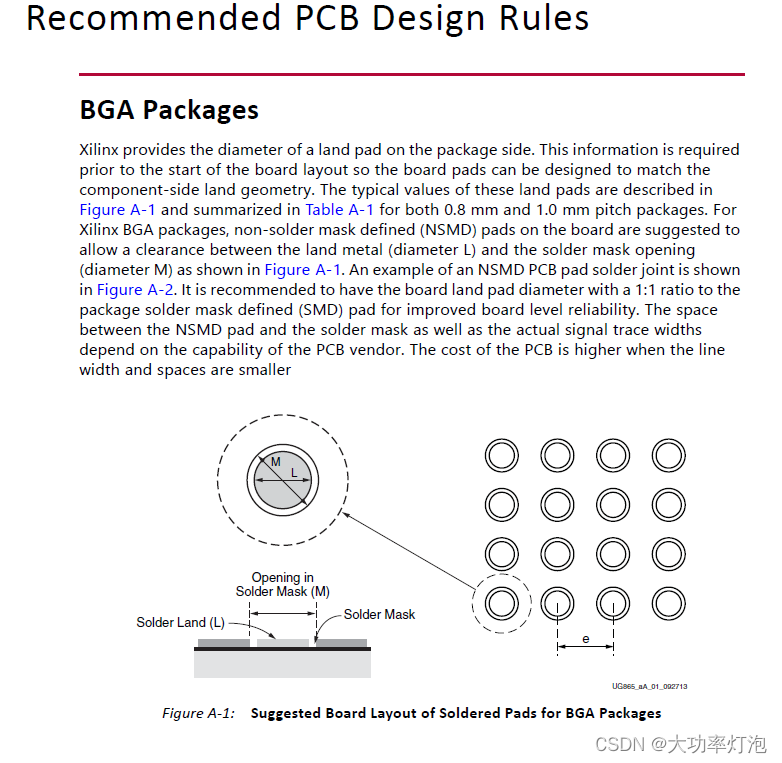

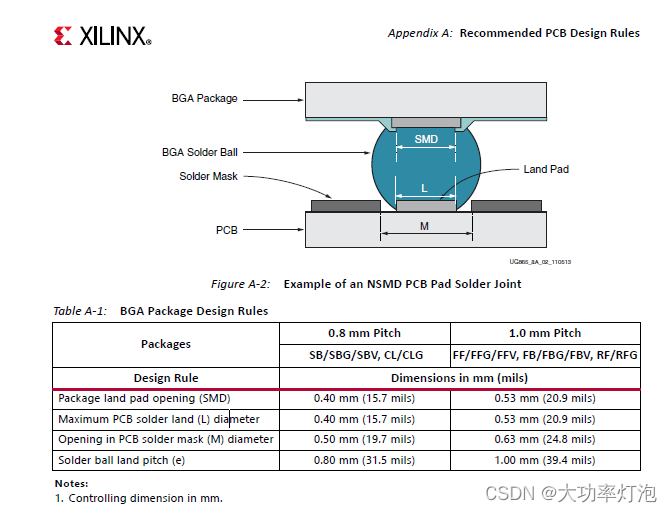

7. BGA焊盘

8. 引脚 ascii

Device/Package xc7z020clg400 9/18/2012 09:51:09 Pin Pin Name Memory Byte Group Bank VCCAUX Group Super Logic Region I/O Type No-Connect

R11 DONE_0 NA 0 NA NA CONFIG NA

M9 DXP_0 NA 0 NA NA CONFIG NA

J10 GNDADC_0 NA 0 NA NA CONFIG NA

J9 VCCADC_0 NA 0 NA NA CONFIG NA

L9 VREFP_0 NA 0 NA NA CONFIG NA

L10 VN_0 NA 0 NA NA CONFIG NA

F11 VCCBATT_0 NA 0 NA NA CONFIG NA

F9 TCK_0 NA 0 NA NA CONFIG NA

M10 DXN_0 NA 0 NA NA CONFIG NA

K10 VREFN_0 NA 0 NA NA CONFIG NA

K9 VP_0 NA 0 NA NA CONFIG NA

F10 RSVDGND NA 0 NA NA CONFIG NA

N6 RSVDVCC3 NA 0 NA NA CONFIG NA

R6 RSVDVCC2 NA 0 NA NA CONFIG NA

R10 INIT_B_0 NA 0 NA NA CONFIG NA

G6 TDI_0 NA 0 NA NA CONFIG NA

F6 TDO_0 NA 0 NA NA CONFIG NA

T6 RSVDVCC1 NA 0 NA NA CONFIG NA

M6 CFGBVS_0 NA 0 NA NA CONFIG NA

L6 PROGRAM_B_0 NA 0 NA NA CONFIG NA

J6 TMS_0 NA 0 NA NA CONFIG NA

V5 IO_L6N_T0_VREF_13 0 13 NA NA HR 7Z010

U7 IO_L11P_T1_SRCC_13 1 13 NA NA HR 7Z010

V7 IO_L11N_T1_SRCC_13 1 13 NA NA HR 7Z010

T9 IO_L12P_T1_MRCC_13 1 13 NA NA HR 7Z010

U10 IO_L12N_T1_MRCC_13 1 13 NA NA HR 7Z010

Y7 IO_L13P_T2_MRCC_13 2 13 NA NA HR 7Z010

Y6 IO_L13N_T2_MRCC_13 2 13 NA NA HR 7Z010

Y9 IO_L14P_T2_SRCC_13 2 13 NA NA HR 7Z010

Y8 IO_L14N_T2_SRCC_13 2 13 NA NA HR 7Z010

V8 IO_L15P_T2_DQS_13 2 13 NA NA HR 7Z010

W8 IO_L15N_T2_DQS_13 2 13 NA NA HR 7Z010

W10 IO_L16P_T2_13 2 13 NA NA HR 7Z010

W9 IO_L16N_T2_13 2 13 NA NA HR 7Z010

U9 IO_L17P_T2_13 2 13 NA NA HR 7Z010

U8 IO_L17N_T2_13 2 13 NA NA HR 7Z010

W11 IO_L18P_T2_13 2 13 NA NA HR 7Z010

Y11 IO_L18N_T2_13 2 13 NA NA HR 7Z010

T5 IO_L19P_T3_13 3 13 NA NA HR 7Z010

U5 IO_L19N_T3_VREF_13 3 13 NA NA HR 7Z010

Y12 IO_L20P_T3_13 3 13 NA NA HR 7Z010

Y13 IO_L20N_T3_13 3 13 NA NA HR 7Z010

V11 IO_L21P_T3_DQS_13 3 13 NA NA HR 7Z010

V10 IO_L21N_T3_DQS_13 3 13 NA NA HR 7Z010

V6 IO_L22P_T3_13 3 13 NA NA HR 7Z010

W6 IO_L22N_T3_13 3 13 NA NA HR 7Z010

R19 IO_0_34 NA 34 NA NA HR NA

T11 IO_L1P_T0_34 0 34 NA NA HR NA

T10 IO_L1N_T0_34 0 34 NA NA HR NA

T12 IO_L2P_T0_34 0 34 NA NA HR NA

U12 IO_L2N_T0_34 0 34 NA NA HR NA

U13 IO_L3P_T0_DQS_PUDC_B_34 0 34 NA NA HR NA

V13 IO_L3N_T0_DQS_34 0 34 NA NA HR NA

V12 IO_L4P_T0_34 0 34 NA NA HR NA

W13 IO_L4N_T0_34 0 34 NA NA HR NA

T14 IO_L5P_T0_34 0 34 NA NA HR NA

T15 IO_L5N_T0_34 0 34 NA NA HR NA

P14 IO_L6P_T0_34 0 34 NA NA HR NA

R14 IO_L6N_T0_VREF_34 0 34 NA NA HR NA

Y16 IO_L7P_T1_34 1 34 NA NA HR NA

Y17 IO_L7N_T1_34 1 34 NA NA HR NA

W14 IO_L8P_T1_34 1 34 NA NA HR NA

Y14 IO_L8N_T1_34 1 34 NA NA HR NA

T16 IO_L9P_T1_DQS_34 1 34 NA NA HR NA

U17 IO_L9N_T1_DQS_34 1 34 NA NA HR NA

V15 IO_L10P_T1_34 1 34 NA NA HR NA

W15 IO_L10N_T1_34 1 34 NA NA HR NA

U14 IO_L11P_T1_SRCC_34 1 34 NA NA HR NA

U15 IO_L11N_T1_SRCC_34 1 34 NA NA HR NA

U18 IO_L12P_T1_MRCC_34 1 34 NA NA HR NA

U19 IO_L12N_T1_MRCC_34 1 34 NA NA HR NA

N18 IO_L13P_T2_MRCC_34 2 34 NA NA HR NA

P19 IO_L13N_T2_MRCC_34 2 34 NA NA HR NA

N20 IO_L14P_T2_SRCC_34 2 34 NA NA HR NA

P20 IO_L14N_T2_SRCC_34 2 34 NA NA HR NA

T20 IO_L15P_T2_DQS_34 2 34 NA NA HR NA

U20 IO_L15N_T2_DQS_34 2 34 NA NA HR NA

V20 IO_L16P_T2_34 2 34 NA NA HR NA

W20 IO_L16N_T2_34 2 34 NA NA HR NA

Y18 IO_L17P_T2_34 2 34 NA NA HR NA

Y19 IO_L17N_T2_34 2 34 NA NA HR NA

V16 IO_L18P_T2_34 2 34 NA NA HR NA

W16 IO_L18N_T2_34 2 34 NA NA HR NA

R16 IO_L19P_T3_34 3 34 NA NA HR NA

R17 IO_L19N_T3_VREF_34 3 34 NA NA HR NA

T17 IO_L20P_T3_34 3 34 NA NA HR NA

R18 IO_L20N_T3_34 3 34 NA NA HR NA

V17 IO_L21P_T3_DQS_34 3 34 NA NA HR NA

V18 IO_L21N_T3_DQS_34 3 34 NA NA HR NA

W18 IO_L22P_T3_34 3 34 NA NA HR NA

W19 IO_L22N_T3_34 3 34 NA NA HR NA

N17 IO_L23P_T3_34 3 34 NA NA HR NA

P18 IO_L23N_T3_34 3 34 NA NA HR NA

P15 IO_L24P_T3_34 3 34 NA NA HR NA

P16 IO_L24N_T3_34 3 34 NA NA HR NA

T19 IO_25_34 NA 34 NA NA HR NA

G14 IO_0_35 NA 35 NA NA HR NA

C20 IO_L1P_T0_AD0P_35 0 35 NA NA HR NA

B20 IO_L1N_T0_AD0N_35 0 35 NA NA HR NA

B19 IO_L2P_T0_AD8P_35 0 35 NA NA HR NA

A20 IO_L2N_T0_AD8N_35 0 35 NA NA HR NA

E17 IO_L3P_T0_DQS_AD1P_35 0 35 NA NA HR NA

D18 IO_L3N_T0_DQS_AD1N_35 0 35 NA NA HR NA

D19 IO_L4P_T0_35 0 35 NA NA HR NA

D20 IO_L4N_T0_35 0 35 NA NA HR NA

E18 IO_L5P_T0_AD9P_35 0 35 NA NA HR NA

E19 IO_L5N_T0_AD9N_35 0 35 NA NA HR NA

F16 IO_L6P_T0_35 0 35 NA NA HR NA

F17 IO_L6N_T0_VREF_35 0 35 NA NA HR NA

M19 IO_L7P_T1_AD2P_35 1 35 NA NA HR NA

M20 IO_L7N_T1_AD2N_35 1 35 NA NA HR NA

M17 IO_L8P_T1_AD10P_35 1 35 NA NA HR NA

M18 IO_L8N_T1_AD10N_35 1 35 NA NA HR NA

L19 IO_L9P_T1_DQS_AD3P_35 1 35 NA NA HR NA

L20 IO_L9N_T1_DQS_AD3N_35 1 35 NA NA HR NA

K19 IO_L10P_T1_AD11P_35 1 35 NA NA HR NA

J19 IO_L10N_T1_AD11N_35 1 35 NA NA HR NA

L16 IO_L11P_T1_SRCC_35 1 35 NA NA HR NA

L17 IO_L11N_T1_SRCC_35 1 35 NA NA HR NA

K17 IO_L12P_T1_MRCC_35 1 35 NA NA HR NA

K18 IO_L12N_T1_MRCC_35 1 35 NA NA HR NA

H16 IO_L13P_T2_MRCC_35 2 35 NA NA HR NA

H17 IO_L13N_T2_MRCC_35 2 35 NA NA HR NA

J18 IO_L14P_T2_AD4P_SRCC_35 2 35 NA NA HR NA

H18 IO_L14N_T2_AD4N_SRCC_35 2 35 NA NA HR NA

F19 IO_L15P_T2_DQS_AD12P_35 2 35 NA NA HR NA

F20 IO_L15N_T2_DQS_AD12N_35 2 35 NA NA HR NA

G17 IO_L16P_T2_35 2 35 NA NA HR NA

G18 IO_L16N_T2_35 2 35 NA NA HR NA

J20 IO_L17P_T2_AD5P_35 2 35 NA NA HR NA

H20 IO_L17N_T2_AD5N_35 2 35 NA NA HR NA

G19 IO_L18P_T2_AD13P_35 2 35 NA NA HR NA

G20 IO_L18N_T2_AD13N_35 2 35 NA NA HR NA

H15 IO_L19P_T3_35 3 35 NA NA HR NA

G15 IO_L19N_T3_VREF_35 3 35 NA NA HR NA

K14 IO_L20P_T3_AD6P_35 3 35 NA NA HR NA

J14 IO_L20N_T3_AD6N_35 3 35 NA NA HR NA

N15 IO_L21P_T3_DQS_AD14P_35 3 35 NA NA HR NA

N16 IO_L21N_T3_DQS_AD14N_35 3 35 NA NA HR NA

L14 IO_L22P_T3_AD7P_35 3 35 NA NA HR NA

L15 IO_L22N_T3_AD7N_35 3 35 NA NA HR NA

M14 IO_L23P_T3_35 3 35 NA NA HR NA

M15 IO_L23N_T3_35 3 35 NA NA HR NA

K16 IO_L24P_T3_AD15P_35 3 35 NA NA HR NA

J16 IO_L24N_T3_AD15N_35 3 35 NA NA HR NA

J15 IO_25_35 NA 35 NA NA HR NA

E7 PS_CLK_500 NA 500 NA NA MIO NA

E11 PS_MIO_VREF_501 NA 501 NA NA MIO NA

C7 PS_POR_B_500 NA 500 NA NA MIO NA

C8 PS_MIO15_500 NA 500 NA NA MIO NA

E14 PS_MIO17_501 NA 501 NA NA MIO NA

D10 PS_MIO19_501 NA 501 NA NA MIO NA

F14 PS_MIO21_501 NA 501 NA NA MIO NA

D11 PS_MIO23_501 NA 501 NA NA MIO NA

F15 PS_MIO25_501 NA 501 NA NA MIO NA

D13 PS_MIO27_501 NA 501 NA NA MIO NA

C13 PS_MIO29_501 NA 501 NA NA MIO NA

E16 PS_MIO31_501 NA 501 NA NA MIO NA

D15 PS_MIO33_501 NA 501 NA NA MIO NA

F12 PS_MIO35_501 NA 501 NA NA MIO NA

E13 PS_MIO38_501 NA 501 NA NA MIO NA

D14 PS_MIO40_501 NA 501 NA NA MIO NA

E12 PS_MIO42_501 NA 501 NA NA MIO NA

F13 PS_MIO44_501 NA 501 NA NA MIO NA

D16 PS_MIO46_501 NA 501 NA NA MIO NA

B12 PS_MIO48_501 NA 501 NA NA MIO NA

B13 PS_MIO50_501 NA 501 NA NA MIO NA

C10 PS_MIO52_501 NA 501 NA NA MIO NA

B10 PS_SRST_B_501 NA 501 NA NA MIO NA

C5 PS_MIO14_500 NA 500 NA NA MIO NA

A19 PS_MIO16_501 NA 501 NA NA MIO NA

B18 PS_MIO18_501 NA 501 NA NA MIO NA

A17 PS_MIO20_501 NA 501 NA NA MIO NA

B17 PS_MIO22_501 NA 501 NA NA MIO NA

A16 PS_MIO24_501 NA 501 NA NA MIO NA

A15 PS_MIO26_501 NA 501 NA NA MIO NA

C16 PS_MIO28_501 NA 501 NA NA MIO NA

C15 PS_MIO30_501 NA 501 NA NA MIO NA

A14 PS_MIO32_501 NA 501 NA NA MIO NA

A12 PS_MIO34_501 NA 501 NA NA MIO NA

A11 PS_MIO36_501 NA 501 NA NA MIO NA

A10 PS_MIO37_501 NA 501 NA NA MIO NA

C18 PS_MIO39_501 NA 501 NA NA MIO NA

C17 PS_MIO41_501 NA 501 NA NA MIO NA

A9 PS_MIO43_501 NA 501 NA NA MIO NA

B15 PS_MIO45_501 NA 501 NA NA MIO NA

B14 PS_MIO47_501 NA 501 NA NA MIO NA

C12 PS_MIO49_501 NA 501 NA NA MIO NA

B9 PS_MIO51_501 NA 501 NA NA MIO NA

C11 PS_MIO53_501 NA 501 NA NA MIO NA

E8 PS_MIO13_500 NA 500 NA NA MIO NA

D9 PS_MIO12_500 NA 500 NA NA MIO NA

C6 PS_MIO11_500 NA 500 NA NA MIO NA

E9 PS_MIO10_500 NA 500 NA NA MIO NA

B5 PS_MIO9_500 NA 500 NA NA MIO NA

D5 PS_MIO8_500 NA 500 NA NA MIO NA

D8 PS_MIO7_500 NA 500 NA NA MIO NA

A5 PS_MIO6_500 NA 500 NA NA MIO NA

A6 PS_MIO5_500 NA 500 NA NA MIO NA

B7 PS_MIO4_500 NA 500 NA NA MIO NA

D6 PS_MIO3_500 NA 500 NA NA MIO NA

B8 PS_MIO2_500 NA 500 NA NA MIO NA

A7 PS_MIO1_500 NA 500 NA NA MIO NA

E6 PS_MIO0_500 NA 500 NA NA MIO NA

B4 PS_DDR_DRST_B_502 NA 502 NA NA DDR NA

C3 PS_DDR_DQ0_502 NA 502 NA NA DDR NA

B3 PS_DDR_DQ1_502 NA 502 NA NA DDR NA

A2 PS_DDR_DQ2_502 NA 502 NA NA DDR NA

A4 PS_DDR_DQ3_502 NA 502 NA NA DDR NA

A1 PS_DDR_DM0_502 NA 502 NA NA DDR NA

C2 PS_DDR_DQS_P0_502 NA 502 NA NA DDR NA

B2 PS_DDR_DQS_N0_502 NA 502 NA NA DDR NA

D3 PS_DDR_DQ4_502 NA 502 NA NA DDR NA

D1 PS_DDR_DQ5_502 NA 502 NA NA DDR NA

C1 PS_DDR_DQ6_502 NA 502 NA NA DDR NA

E1 PS_DDR_DQ7_502 NA 502 NA NA DDR NA

E2 PS_DDR_DQ8_502 NA 502 NA NA DDR NA

E3 PS_DDR_DQ9_502 NA 502 NA NA DDR NA

G3 PS_DDR_DQ10_502 NA 502 NA NA DDR NA

H3 PS_DDR_DQ11_502 NA 502 NA NA DDR NA

F1 PS_DDR_DM1_502 NA 502 NA NA DDR NA

G2 PS_DDR_DQS_P1_502 NA 502 NA NA DDR NA

F2 PS_DDR_DQS_N1_502 NA 502 NA NA DDR NA

J3 PS_DDR_DQ12_502 NA 502 NA NA DDR NA

H2 PS_DDR_DQ13_502 NA 502 NA NA DDR NA

H1 PS_DDR_DQ14_502 NA 502 NA NA DDR NA

J1 PS_DDR_DQ15_502 NA 502 NA NA DDR NA

F4 PS_DDR_A14_502 NA 502 NA NA DDR NA

D4 PS_DDR_A13_502 NA 502 NA NA DDR NA

E4 PS_DDR_A12_502 NA 502 NA NA DDR NA

G4 PS_DDR_A11_502 NA 502 NA NA DDR NA

F5 PS_DDR_A10_502 NA 502 NA NA DDR NA

J4 PS_DDR_A9_502 NA 502 NA NA DDR NA

K1 PS_DDR_A8_502 NA 502 NA NA DDR NA

K4 PS_DDR_A7_502 NA 502 NA NA DDR NA

L4 PS_DDR_A6_502 NA 502 NA NA DDR NA

L1 PS_DDR_A5_502 NA 502 NA NA DDR NA

M4 PS_DDR_A4_502 NA 502 NA NA DDR NA

K3 PS_DDR_A3_502 NA 502 NA NA DDR NA

G5 PS_DDR_VRN_502 NA 502 NA NA DDR NA

H5 PS_DDR_VRP_502 NA 502 NA NA DDR NA

L2 PS_DDR_CKP_502 NA 502 NA NA DDR NA

M2 PS_DDR_CKN_502 NA 502 NA NA DDR NA

M3 PS_DDR_A2_502 NA 502 NA NA DDR NA

K2 PS_DDR_A1_502 NA 502 NA NA DDR NA

N2 PS_DDR_A0_502 NA 502 NA NA DDR NA

J5 PS_DDR_BA2_502 NA 502 NA NA DDR NA

R4 PS_DDR_BA1_502 NA 502 NA NA DDR NA

L5 PS_DDR_BA0_502 NA 502 NA NA DDR NA

N5 PS_DDR_ODT_502 NA 502 NA NA DDR NA

N1 PS_DDR_CS_B_502 NA 502 NA NA DDR NA

N3 PS_DDR_CKE_502 NA 502 NA NA DDR NA

M5 PS_DDR_WE_B_502 NA 502 NA NA DDR NA

P5 PS_DDR_CAS_B_502 NA 502 NA NA DDR NA

P4 PS_DDR_RAS_B_502 NA 502 NA NA DDR NA

P1 PS_DDR_DQ16_502 NA 502 NA NA DDR NA

P3 PS_DDR_DQ17_502 NA 502 NA NA DDR NA

R3 PS_DDR_DQ18_502 NA 502 NA NA DDR NA

R1 PS_DDR_DQ19_502 NA 502 NA NA DDR NA

T1 PS_DDR_DM2_502 NA 502 NA NA DDR NA

R2 PS_DDR_DQS_P2_502 NA 502 NA NA DDR NA

T2 PS_DDR_DQS_N2_502 NA 502 NA NA DDR NA

T4 PS_DDR_DQ20_502 NA 502 NA NA DDR NA

U4 PS_DDR_DQ21_502 NA 502 NA NA DDR NA

U2 PS_DDR_DQ22_502 NA 502 NA NA DDR NA

U3 PS_DDR_DQ23_502 NA 502 NA NA DDR NA

V1 PS_DDR_DQ24_502 NA 502 NA NA DDR NA

Y3 PS_DDR_DQ25_502 NA 502 NA NA DDR NA

W1 PS_DDR_DQ26_502 NA 502 NA NA DDR NA

Y4 PS_DDR_DQ27_502 NA 502 NA NA DDR NA

Y1 PS_DDR_DM3_502 NA 502 NA NA DDR NA

W5 PS_DDR_DQS_P3_502 NA 502 NA NA DDR NA

W4 PS_DDR_DQS_N3_502 NA 502 NA NA DDR NA

Y2 PS_DDR_DQ28_502 NA 502 NA NA DDR NA

W3 PS_DDR_DQ29_502 NA 502 NA NA DDR NA

V2 PS_DDR_DQ30_502 NA 502 NA NA DDR NA

V3 PS_DDR_DQ31_502 NA 502 NA NA DDR NA

A8 GND NA NA NA NA NA NA

A18 GND NA NA NA NA NA NA

B1 GND NA NA NA NA NA NA

B11 GND NA NA NA NA NA NA

C4 GND NA NA NA NA NA NA

C14 GND NA NA NA NA NA NA

K11 GND NA NA NA NA NA NA

D17 GND NA NA NA NA NA NA

E10 GND NA NA NA NA NA NA

E20 GND NA NA NA NA NA NA

F3 GND NA NA NA NA NA NA

F7 GND NA NA NA NA NA NA

G10 GND NA NA NA NA NA NA

G12 GND NA NA NA NA NA NA

G16 GND NA NA NA NA NA NA

H7 GND NA NA NA NA NA NA

H9 GND NA NA NA NA NA NA

H11 GND NA NA NA NA NA NA

H13 GND NA NA NA NA NA NA

H19 GND NA NA NA NA NA NA

J2 GND NA NA NA NA NA NA

J8 GND NA NA NA NA NA NA

J12 GND NA NA NA NA NA NA

K5 GND NA NA NA NA NA NA

K7 GND NA NA NA NA NA NA

C9 GND NA NA NA NA NA NA

K13 GND NA NA NA NA NA NA

K15 GND NA NA NA NA NA NA

L8 GND NA NA NA NA NA NA

L12 GND NA NA NA NA NA NA

L18 GND NA NA NA NA NA NA

M1 GND NA NA NA NA NA NA

M7 GND NA NA NA NA NA NA

M11 GND NA NA NA NA NA NA

M13 GND NA NA NA NA NA NA

N4 GND NA NA NA NA NA NA

N8 GND NA NA NA NA NA NA

N10 GND NA NA NA NA NA NA

N12 GND NA NA NA NA NA NA

N14 GND NA NA NA NA NA NA

P7 GND NA NA NA NA NA NA

P9 GND NA NA NA NA NA NA

P11 GND NA NA NA NA NA NA

P13 GND NA NA NA NA NA NA

P17 GND NA NA NA NA NA NA

R8 GND NA NA NA NA NA NA

R12 GND NA NA NA NA NA NA

R20 GND NA NA NA NA NA NA

T3 GND NA NA NA NA NA NA

T7 GND NA NA NA NA NA NA

T13 GND NA NA NA NA NA NA

U6 GND NA NA NA NA NA NA

U16 GND NA NA NA NA NA NA

V9 GND NA NA NA NA NA NA

V19 GND NA NA NA NA NA NA

W2 GND NA NA NA NA NA NA

W12 GND NA NA NA NA NA NA

Y5 GND NA NA NA NA NA NA

Y15 GND NA NA NA NA NA NA

G13 VCCINT NA NA NA NA NA NA

H12 VCCINT NA NA NA NA NA NA

J13 VCCINT NA NA NA NA NA NA

K12 VCCINT NA NA NA NA NA NA

L13 VCCINT NA NA NA NA NA NA

M12 VCCINT NA NA NA NA NA NA

N13 VCCINT NA NA NA NA NA NA

P12 VCCINT NA NA NA NA NA NA

R13 VCCINT NA NA NA NA NA NA

J11 VCCAUX NA NA NA NA NA NA

L11 VCCAUX NA NA NA NA NA NA

N9 VCCAUX NA NA NA NA NA NA

P10 VCCAUX NA NA NA NA NA NA

R9 VCCAUX NA NA NA NA NA NA

N11 VCCAUX NA NA NA NA NA NA

K6 VCCO_0 NA 0 NA NA NA NA

T8 VCCO_13 NA 13 NA NA NA NA

U11 VCCO_13 NA 13 NA NA NA NA

W7 VCCO_13 NA 13 NA NA NA NA

Y10 VCCO_13 NA 13 NA NA NA NA

N19 VCCO_34 NA 34 NA NA NA NA

R15 VCCO_34 NA 34 NA NA NA NA

T18 VCCO_34 NA 34 NA NA NA NA

V14 VCCO_34 NA 34 NA NA NA NA

W17 VCCO_34 NA 34 NA NA NA NA

Y20 VCCO_34 NA 34 NA NA NA NA

C19 VCCO_35 NA 35 NA NA NA NA

F18 VCCO_35 NA 35 NA NA NA NA

H14 VCCO_35 NA 35 NA NA NA NA

J17 VCCO_35 NA 35 NA NA NA NA

K20 VCCO_35 NA 35 NA NA NA NA

M16 VCCO_35 NA 35 NA NA NA NA

G11 VCCBRAM NA NA NA NA NA NA

H10 VCCBRAM NA NA NA NA NA NA

A3 VCCO_DDR_502 NA 502 NA NA NA NA

D2 VCCO_DDR_502 NA 502 NA NA NA NA

E5 VCCO_DDR_502 NA 502 NA NA NA NA

G1 VCCO_DDR_502 NA 502 NA NA NA NA

H4 VCCO_DDR_502 NA 502 NA NA NA NA

L3 VCCO_DDR_502 NA 502 NA NA NA NA

P2 VCCO_DDR_502 NA 502 NA NA NA NA

R5 VCCO_DDR_502 NA 502 NA NA NA NA

U1 VCCO_DDR_502 NA 502 NA NA NA NA

V4 VCCO_DDR_502 NA 502 NA NA NA NA

G8 VCCPLL NA NA NA NA NA NA

G9 VCCPAUX NA NA NA NA NA NA

F8 VCCPAUX NA NA NA NA NA NA

H8 VCCPAUX NA NA NA NA NA NA

K8 VCCPAUX NA NA NA NA NA NA

M8 VCCPAUX NA NA NA NA NA NA

G7 VCCPINT NA NA NA NA NA NA

J7 VCCPINT NA NA NA NA NA NA

L7 VCCPINT NA NA NA NA NA NA

N7 VCCPINT NA NA NA NA NA NA

P8 VCCPINT NA NA NA NA NA NA

R7 VCCPINT NA NA NA NA NA NA

B6 VCCO_MIO0_500 NA 500 NA NA NA NA

D7 VCCO_MIO0_500 NA 500 NA NA NA NA

A13 VCCO_MIO1_501 NA 501 NA NA NA NA

B16 VCCO_MIO1_501 NA 501 NA NA NA NA

D12 VCCO_MIO1_501 NA 501 NA NA NA NA

E15 VCCO_MIO1_501 NA 501 NA NA NA NA

H6 PS_DDR_VREF0_502 NA 502 NA NA DDR NA

P6 PS_DDR_VREF1_502 NA 502 NA NA DDR NATotal Number of Pins, 400 2020215 继续补充

9. 正点原子开源了其核心板的原理图、原理图器件库、PCB库,可以自行去参考参考。

http://www.openedv.com/docs/index.html

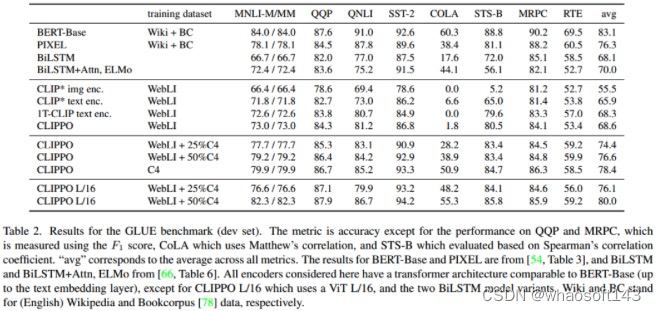

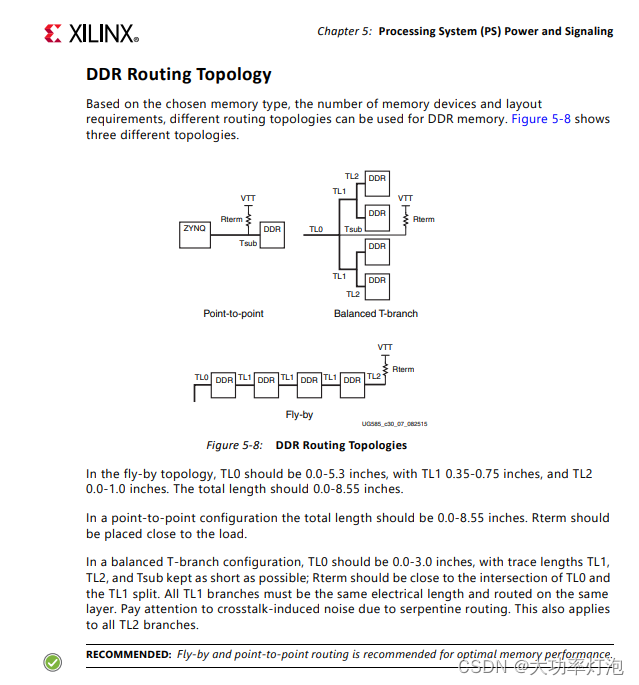

10. zynq7020的DDR3支持fly-by拓扑吗?----------支持

参考xilinx官方手册ug933:

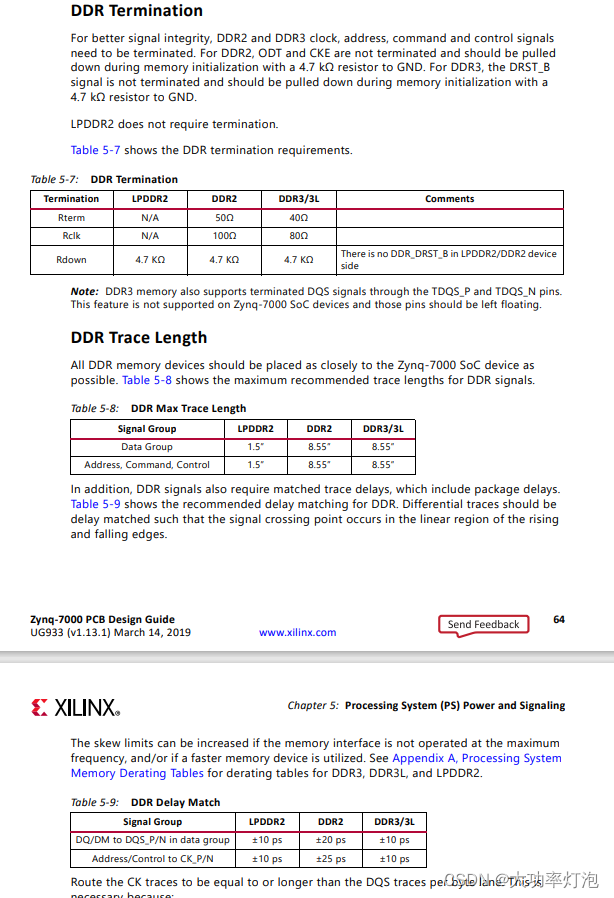

等长延时容差、终端阻抗:

继续补充,

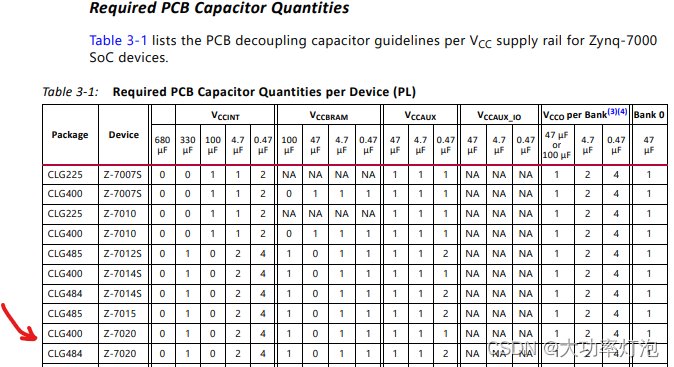

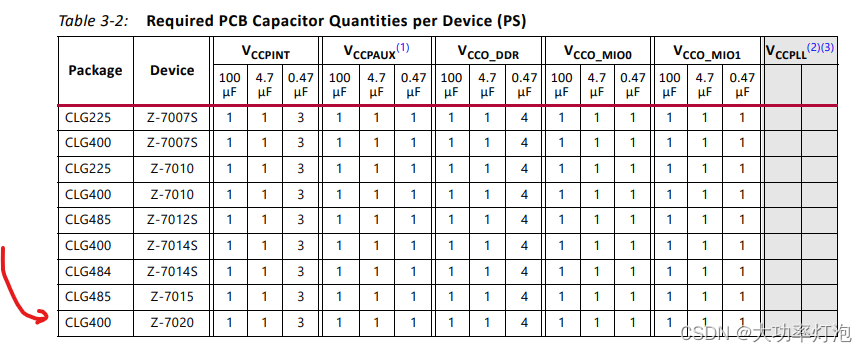

11. zynq7020去偶电容规范–ug933

需要100uF的大电容,惊了

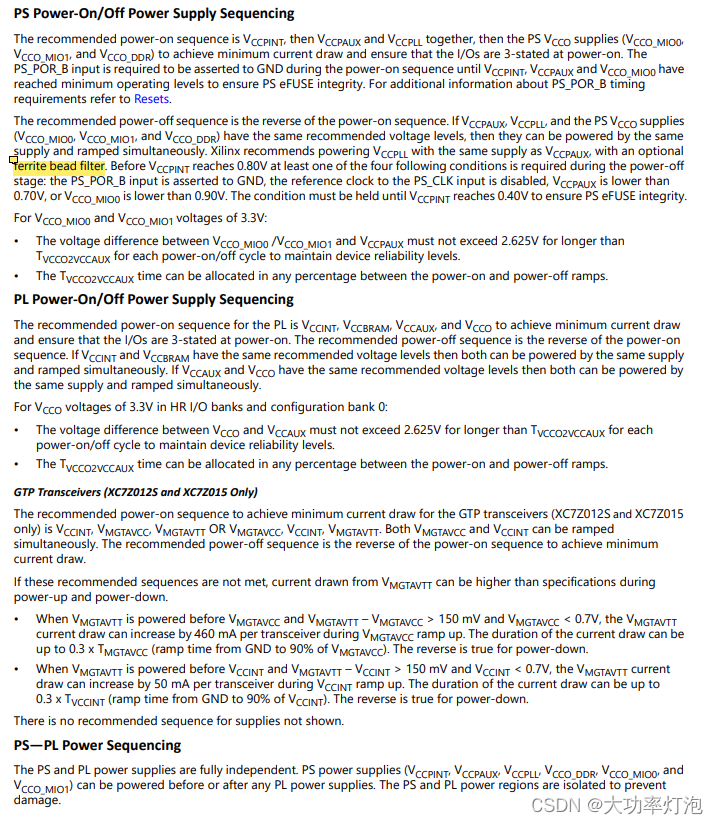

12.PS、PL电源上电顺序:

参考ds187,

注意最后,ps和pl之间的上电顺序是完全独立的!

13.FPGA 是否支持25Mhz时钟?–暂且认为支持

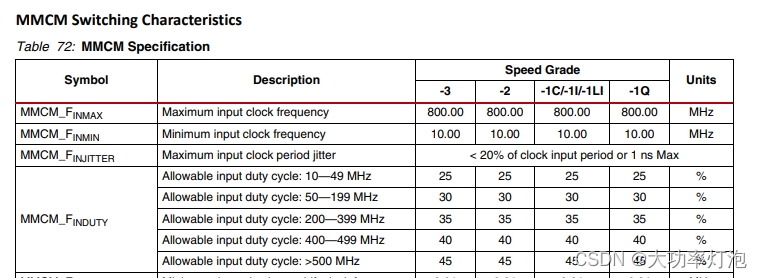

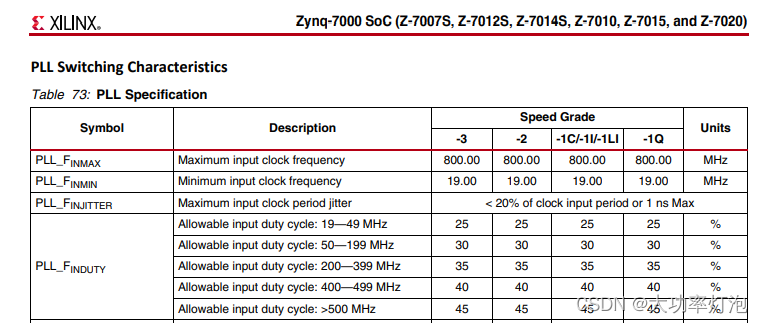

一般FPGA的板载晶振时钟为50Mhz,但是我想替换为稳定度更高的TCXO,电子市场搜了一圈发现50Mhz的温补晶振很少,25Mhz的很贵但也尚有。那么zynq7020支不支持25Mhz的时钟呢?从IO角度,按理说,50Mhz支持,25M更易支持,但除了普通IO速率情况,更应该关注FPGA内部的PLL、MMEM是否支持。

查看ds187,MMCM最低支持10.00Mhz,PLL最低支持19.00Mhz。

按理说,可能还有更多的限制条件我没查到,导致器件不支持25Mhz,但目前姑且认为支持吧(20220216)。等后面做出来后,实际测试再来说明。

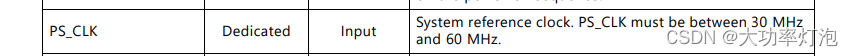

补充一点,ug865 P14 中规定了PS_CLK范围为30M-60Mhz:

14.FPGA 时钟引脚选择

不能随便乱选,应该选择 MRCC 或者 SRCC后缀的引脚,可以参看:https://zhuanlan.zhihu.com/p/139452374

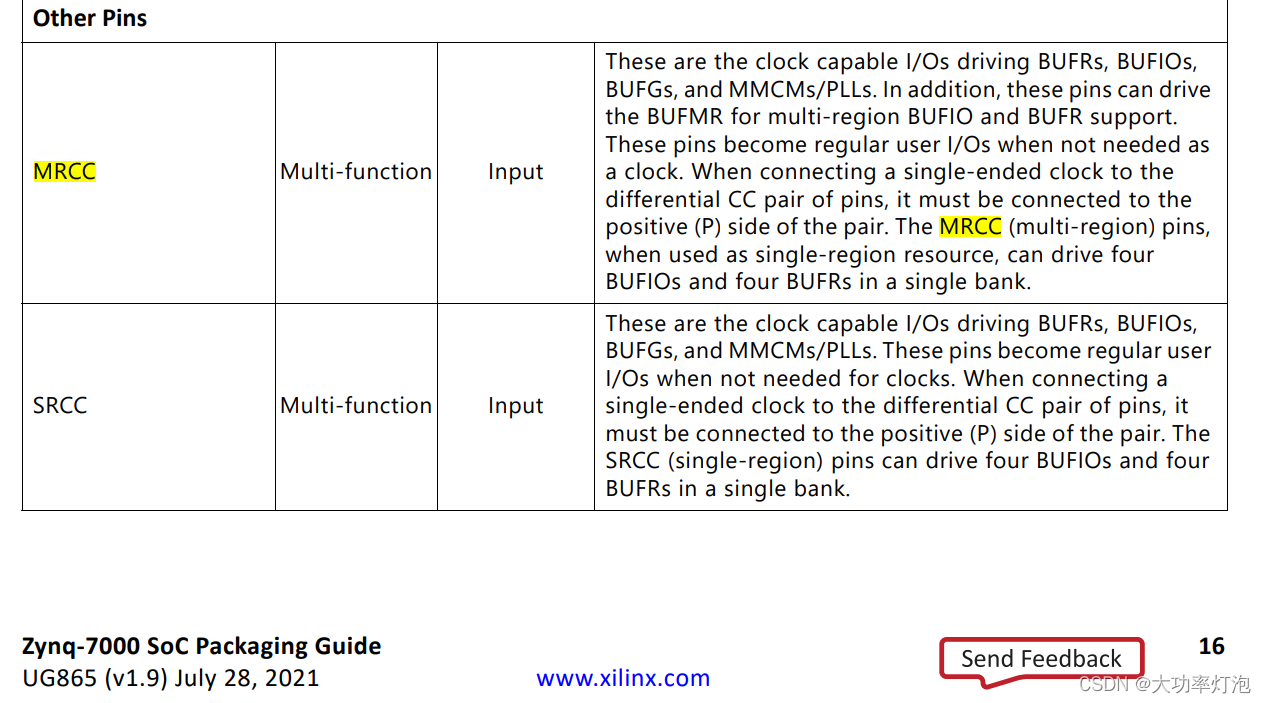

另外手册ug865:

MRCC可以不经过全局时钟到达邻域bank,SRCC只能通过全局时钟,另外单端时钟接入时必须接到差分对的P脚。

········································

········································

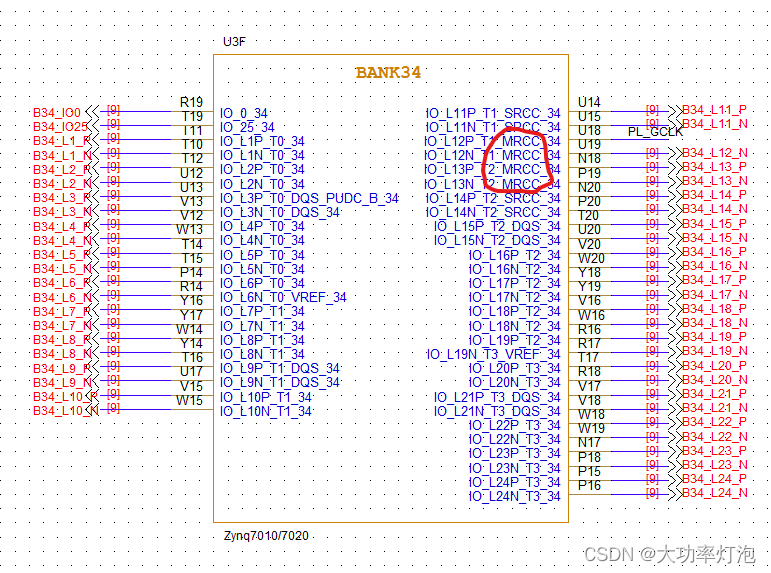

对于zynq7020 Bank34是同时与B35和B13相邻的,B34的MRCC其实最优选择有限,单端的话也就B34_L12_P 和B35_L13_P两个引脚可选。

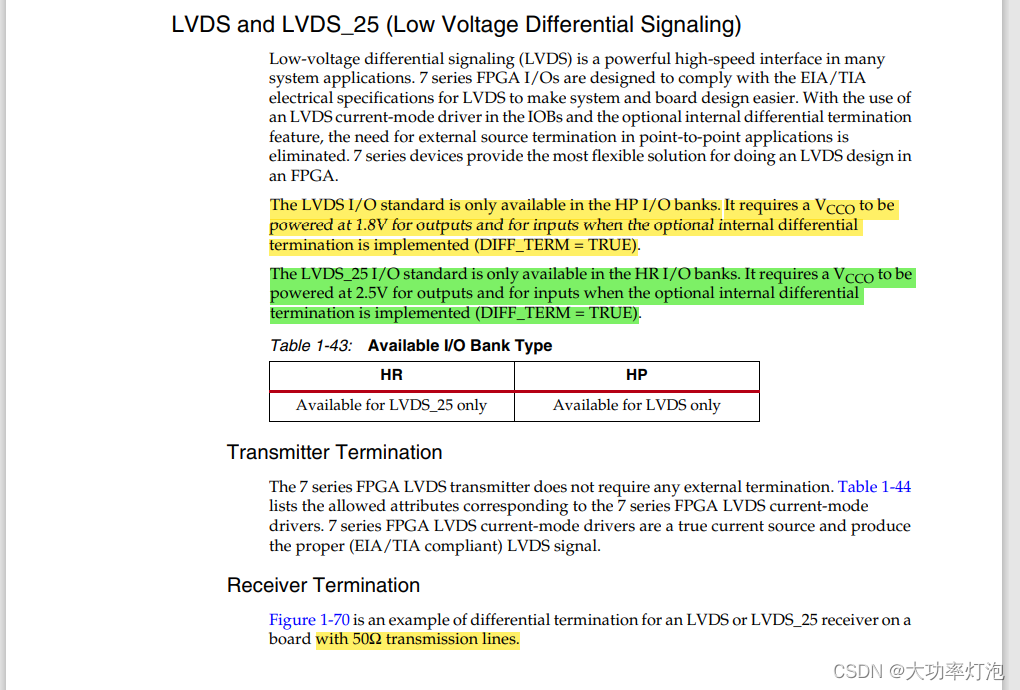

15.LVDS接口使用时注意事项

xilinx 7系列的FPGA的LVDS接口用法和普通IO区别较大,如果后期会使用到该接口,应提交做好硬件上电路的规划,否则后期无法使用该功能!

7系列的FPGA引脚分为HR bank和HP bank两种,HP bank专注于高性能的通信接口, HR bank则是我们通常意义上的IO bank,支持BANK电压 1.8V 2.5V 3.3V等多个电平。各个bank对应的是哪一种可以参考Pkg-Pinout 的手册,如xc7z020就只支持HR bank。HR bank若想使用其LVDS功能,则只能接2.5V的bank电压, 来使用其所谓的LVDS25,不可以接3.3V!

ug865 -zynq-7000-pkg-pinout

ug471-7Series_SelectIO

LVDS要求接收端有一个100欧的终端电阻,FPGA内部一般自带!

所以建议,如果你的时钟接的3.3V电平标准,接入B34 ,那么可以用B35接2.5V的bank来使用LVDS!

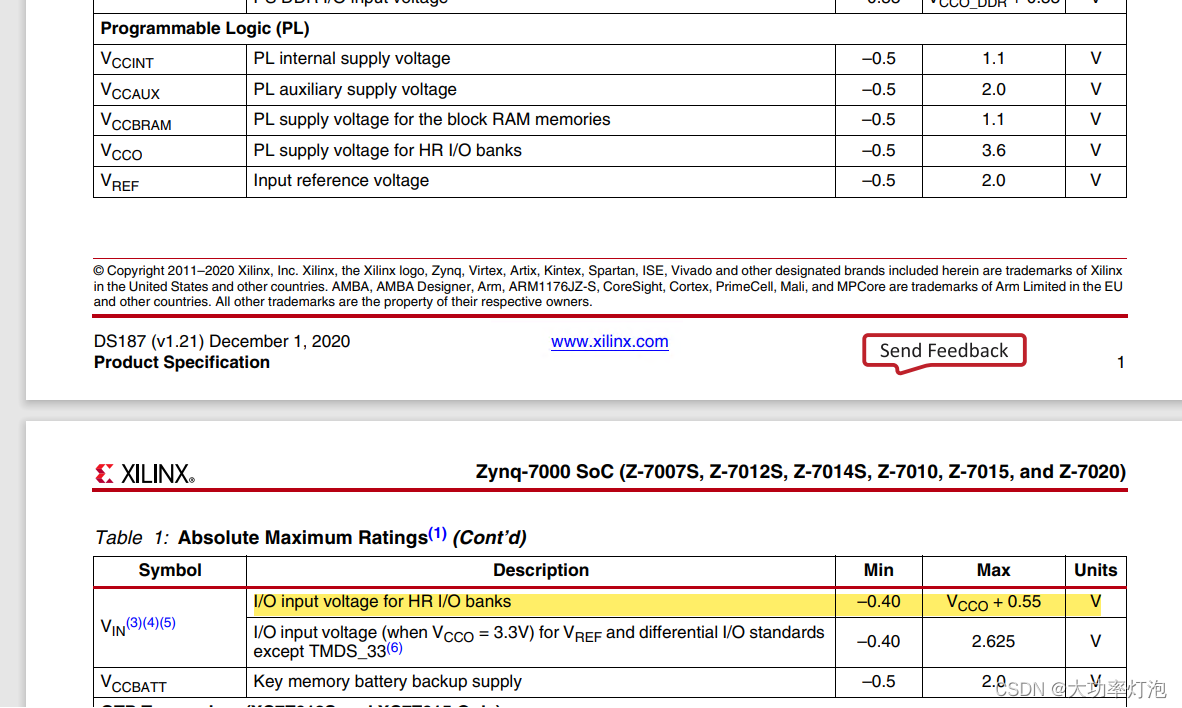

另外,FPGA普通IO的2.5V bank是否支持3.3V输入? 下图告诉我们不要超过0.55V! 强使用时,潜在的影响轻则影响寿命,重则所谓 闩锁效应 烧毁,谨慎考虑!

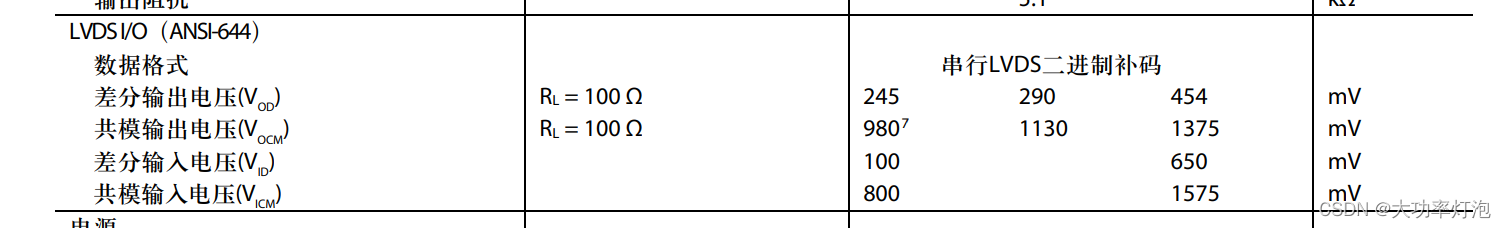

另外LVDS25和LVDS18完全不兼容吗?不一定,需要看具体的器件接收发送共模差模范围!

例如AD7960 ADC使用的是LVDS 1.8V的标准,如下

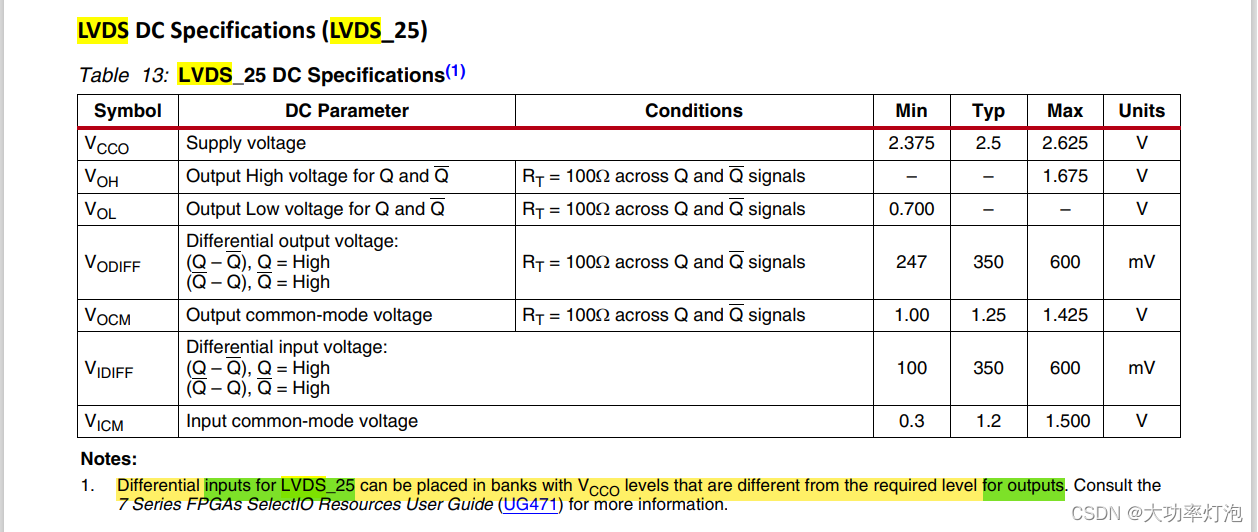

而xc7z202的LVDS 2.5V标准为,

可以发现,无论是共模还是差模,接收端的允许范围都囊括了发送端的变化范围,理论上是可以使用的!