文章目录

- 一、概述

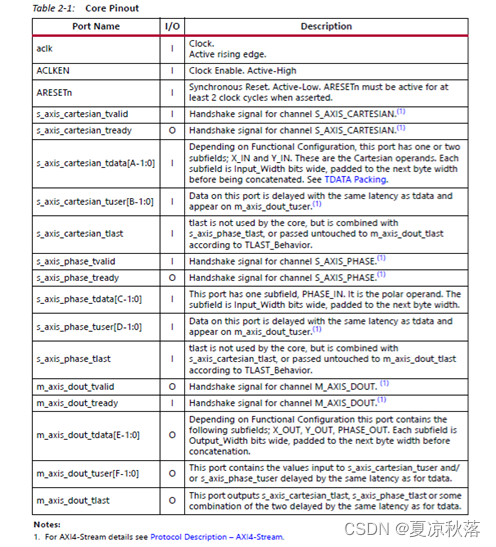

- 二、端口说明

- 三、ip核的生成

- 四、示例

- 五、参考资料

一、概述

cordic核主要用来求三角方程, 主要功能为:

rotate 旋转 ——复数旋转

translate 变换 ——复数转极坐标

sin/cos

arctan

sinh/cosh

arc tanh

square root 平方根

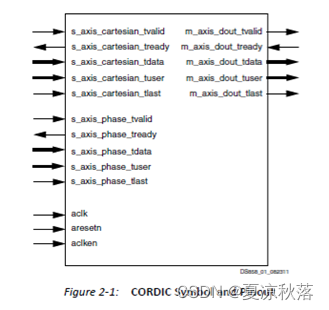

二、端口说明

备注:s_axis_代表核作为丛机,m_axis代表核作为主机,数据宽度一般为8的整数倍

三、ip核的生成

(1)在ip catalog里面选择cordic

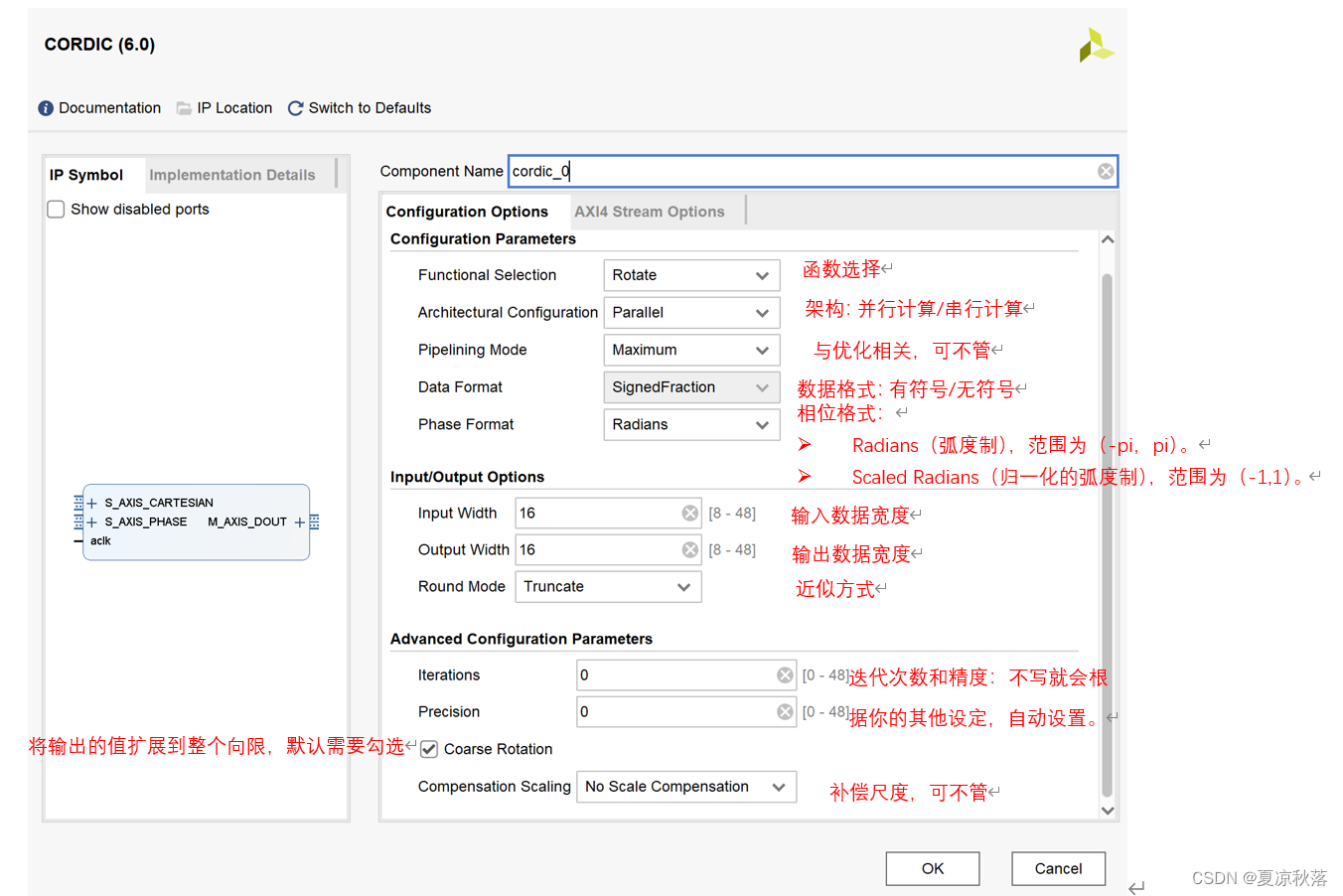

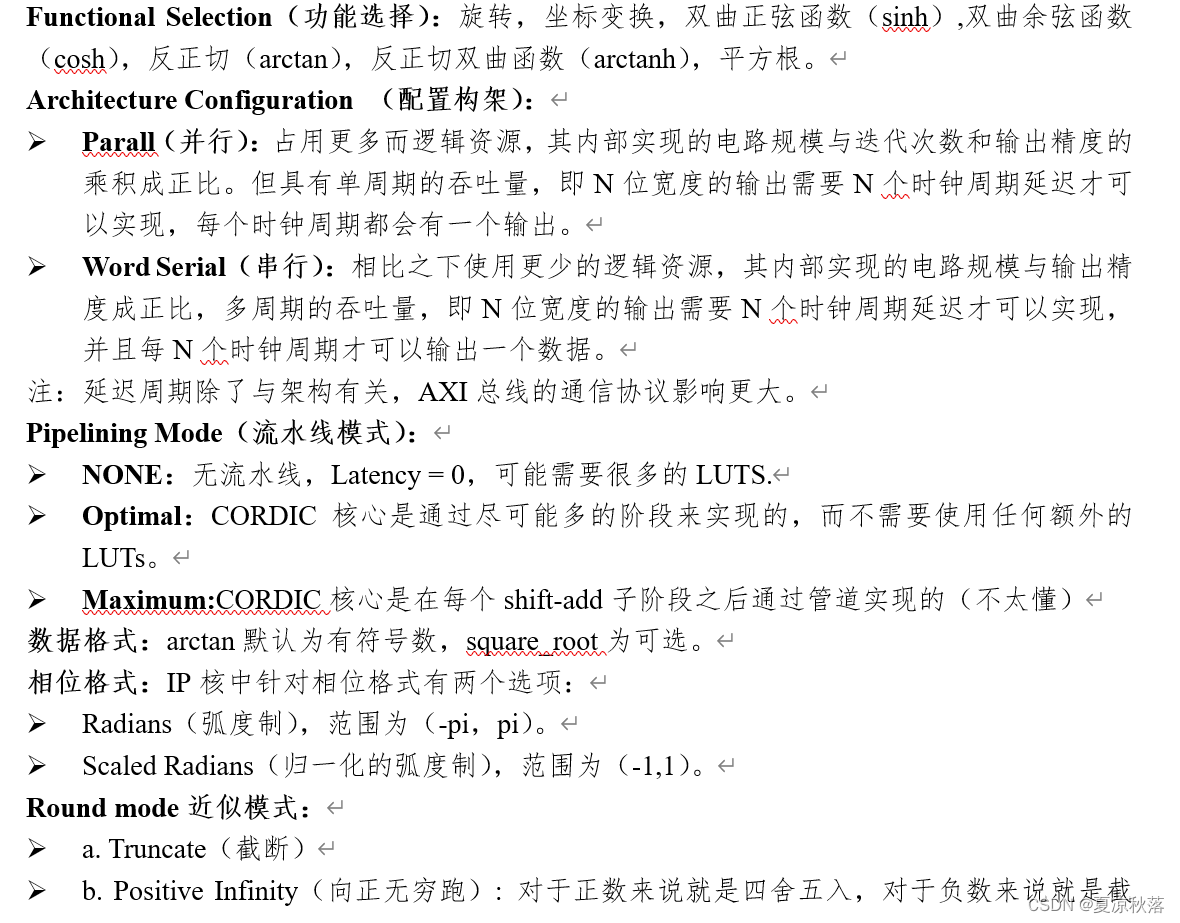

(2)配置configuration

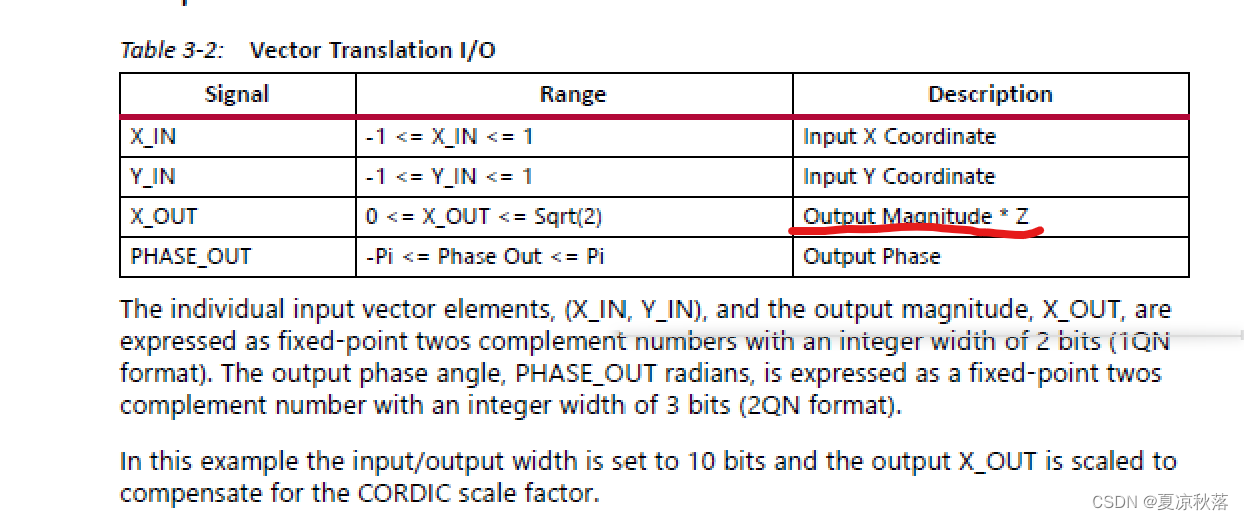

compensation Scaling:补偿因子,当选择不补偿时他的输出是乘了倍数Z的,如下所示:

因此,为了让结果为z,则需要选择补偿项

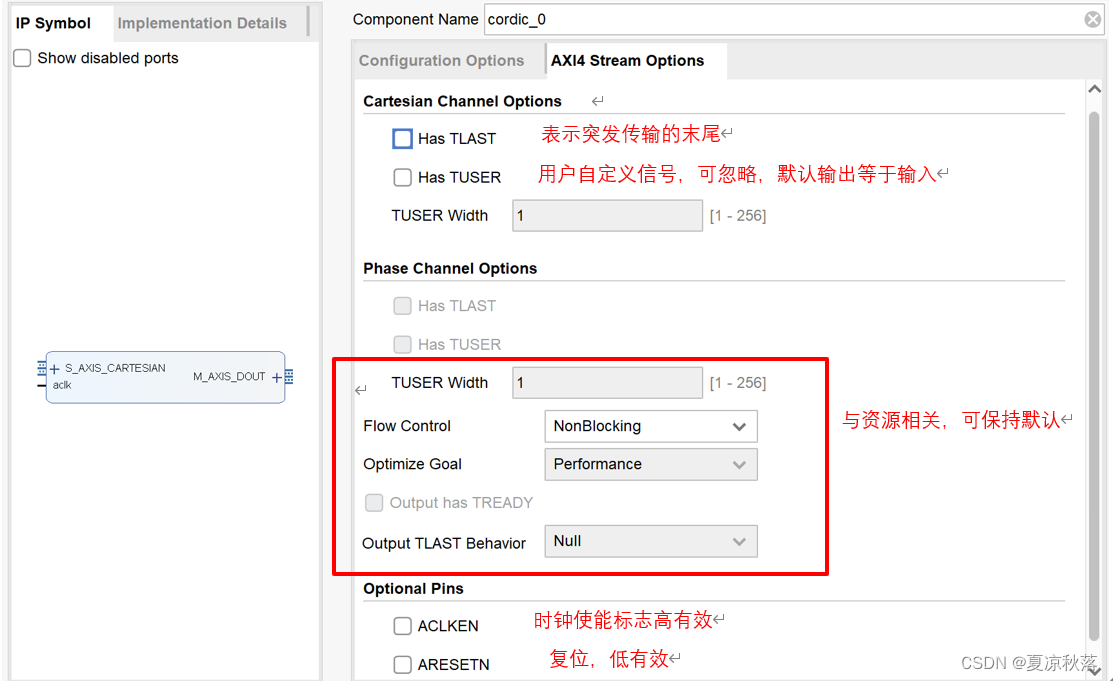

(3)配置Axis Stream Option

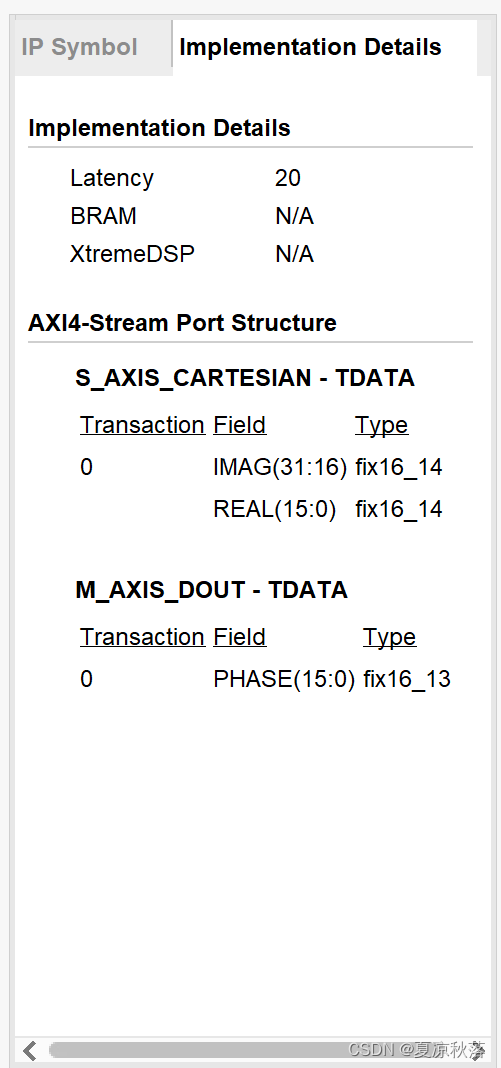

与核相关的具体细节如下所示:

四、示例

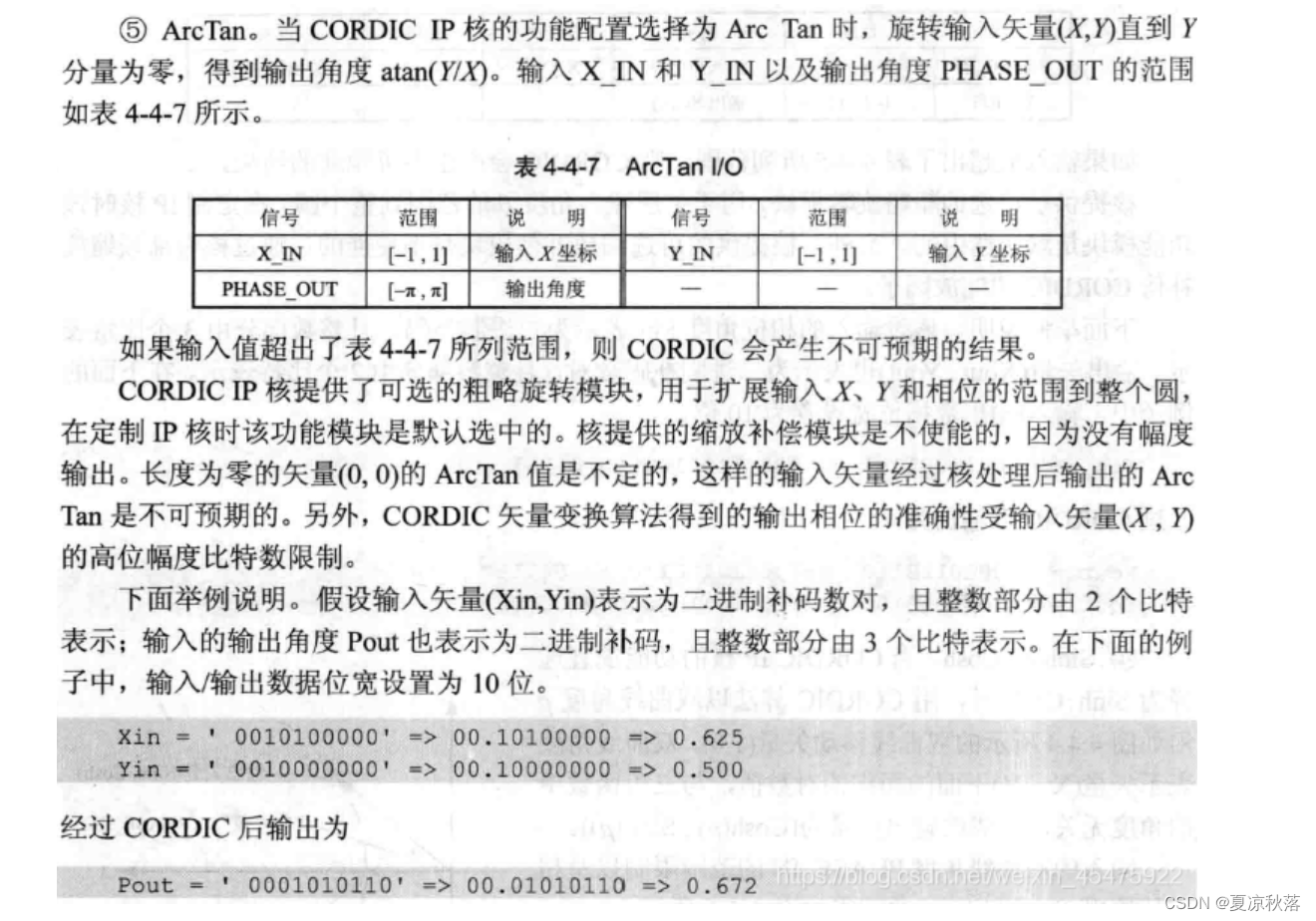

以arctan函数为例进行仿真说明:

输入: 复数据实部虚部,输入格式:IMAG(31:16),REAL(15:0);范围:− 1 ≤ x o r y ≤ 1

输出: 相位,输出格式:PHASE(15:0);范围:− π ≤ x ≤ π

tb文件:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/06/04 10:14:40

// Design Name:

// Module Name: cordic_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module cordic_tb();reg aclk;

reg aresetn;

reg s_axis_cartesian_tvalid;

reg [31:0] s_axis_cartesian_tdata;

wire m_axis_dout_tvalid;

wire [15:0] m_axis_dout_tdata;wire [15:0]X_in;//real

wire [15:0]Y_in;//imagassign Y_in = s_axis_cartesian_tdata[31:16];

assign X_in = s_axis_cartesian_tdata[15: 0];cordic_0 cordic_0_inst0(.aclk(aclk), // input wire aclk.aresetn(aresetn), // input wire aresetn.s_axis_cartesian_tvalid(s_axis_cartesian_tvalid), // input wire s_axis_cartesian_tvalid.s_axis_cartesian_tdata(s_axis_cartesian_tdata), // input wire [31 : 0] s_axis_cartesian_tdata.m_axis_dout_tvalid(m_axis_dout_tvalid), // output wire m_axis_dout_tvalid.m_axis_dout_tdata(m_axis_dout_tdata) // output wire [15 : 0] m_axis_dout_tdata

);/*********************************时钟信号*********************************/initial aclk = 0;always #5 aclk = ~aclk;initial beginaresetn =0;s_axis_cartesian_tvalid=0;s_axis_cartesian_tdata=32'd0;#20;aresetn =1;s_axis_cartesian_tvalid=1;// 前两位为整数部分【第1位符号位,第2位为数字】,后两位为小数部分,,输入必须归一化到-1到1// s_axis_cartesian_tdata=32'b0010000000000000_0010100000000000; //高位为虚部,低位为实部s_axis_cartesian_tdata=32'b0010000000_000000_0010100000_000000;

endendmodule

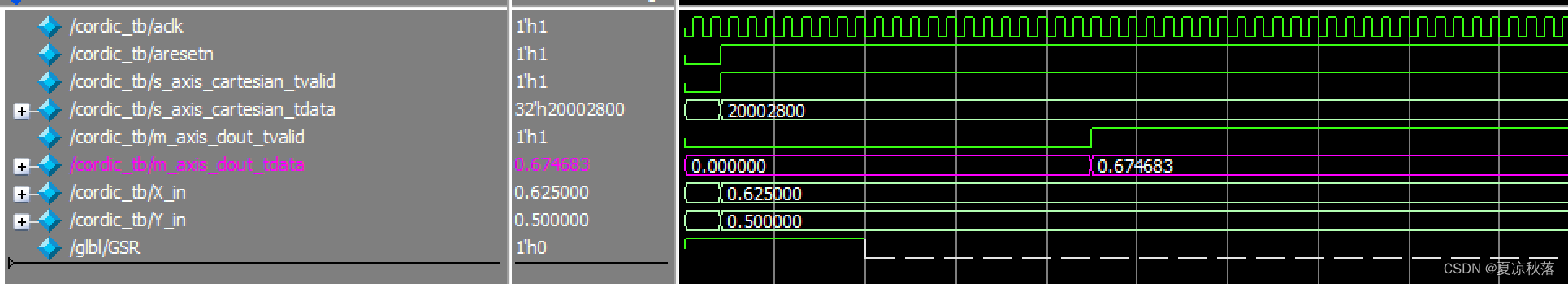

仿真结果;

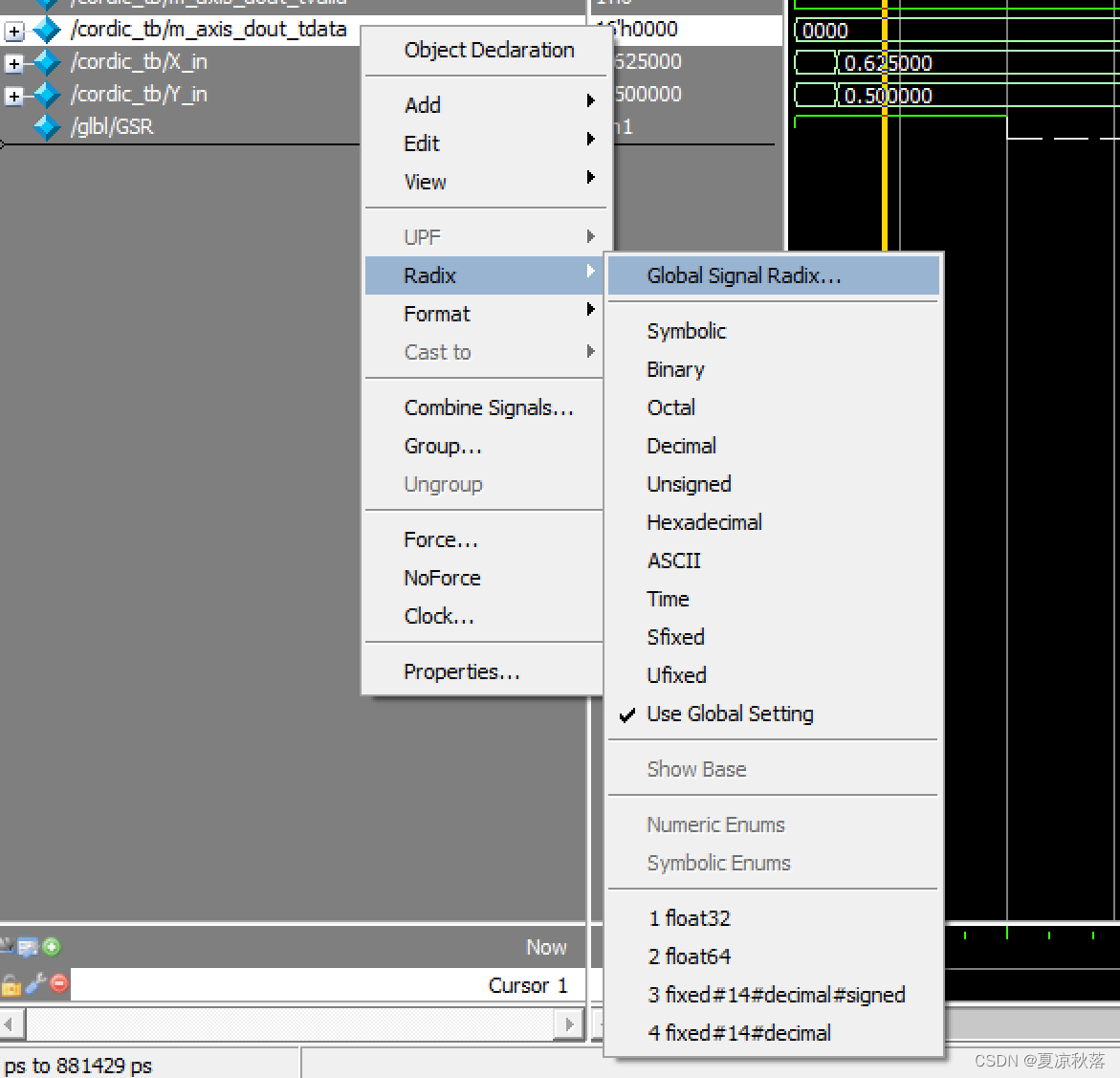

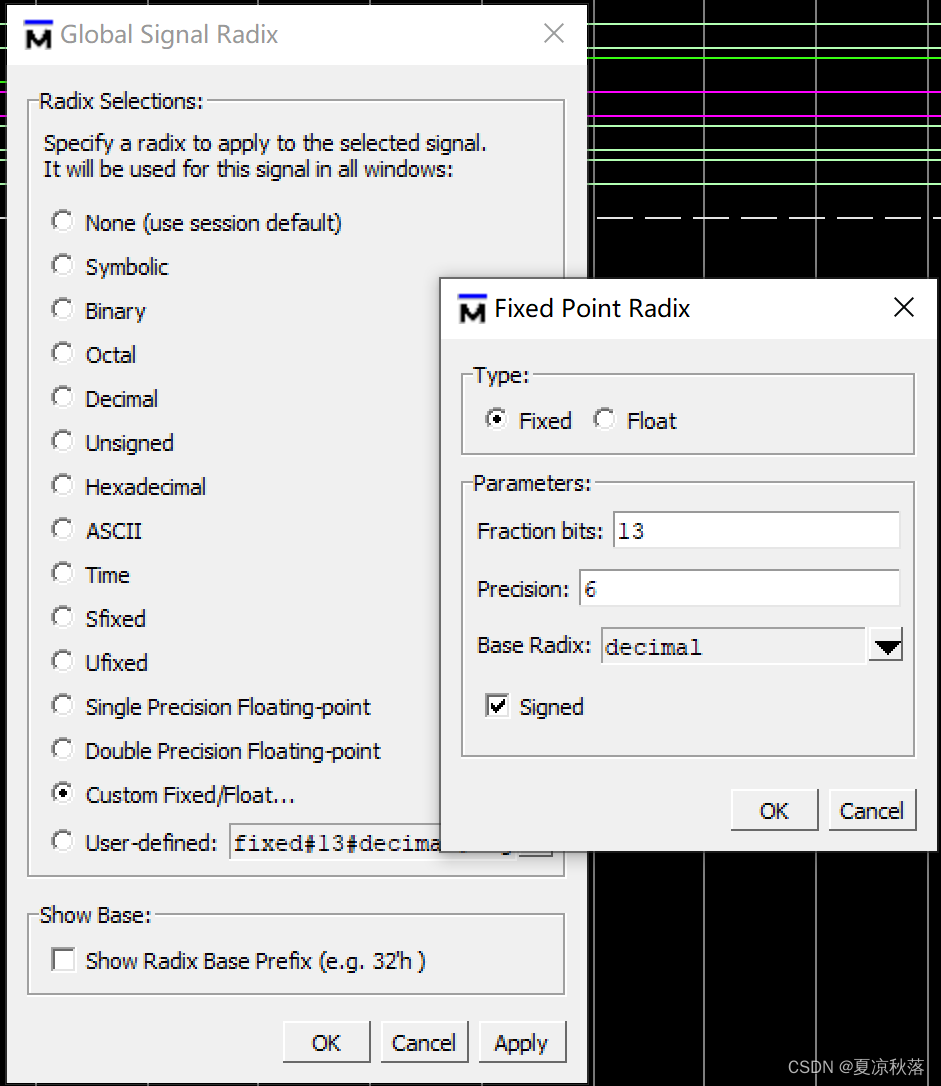

其中modelsim显示小数的方法如下:

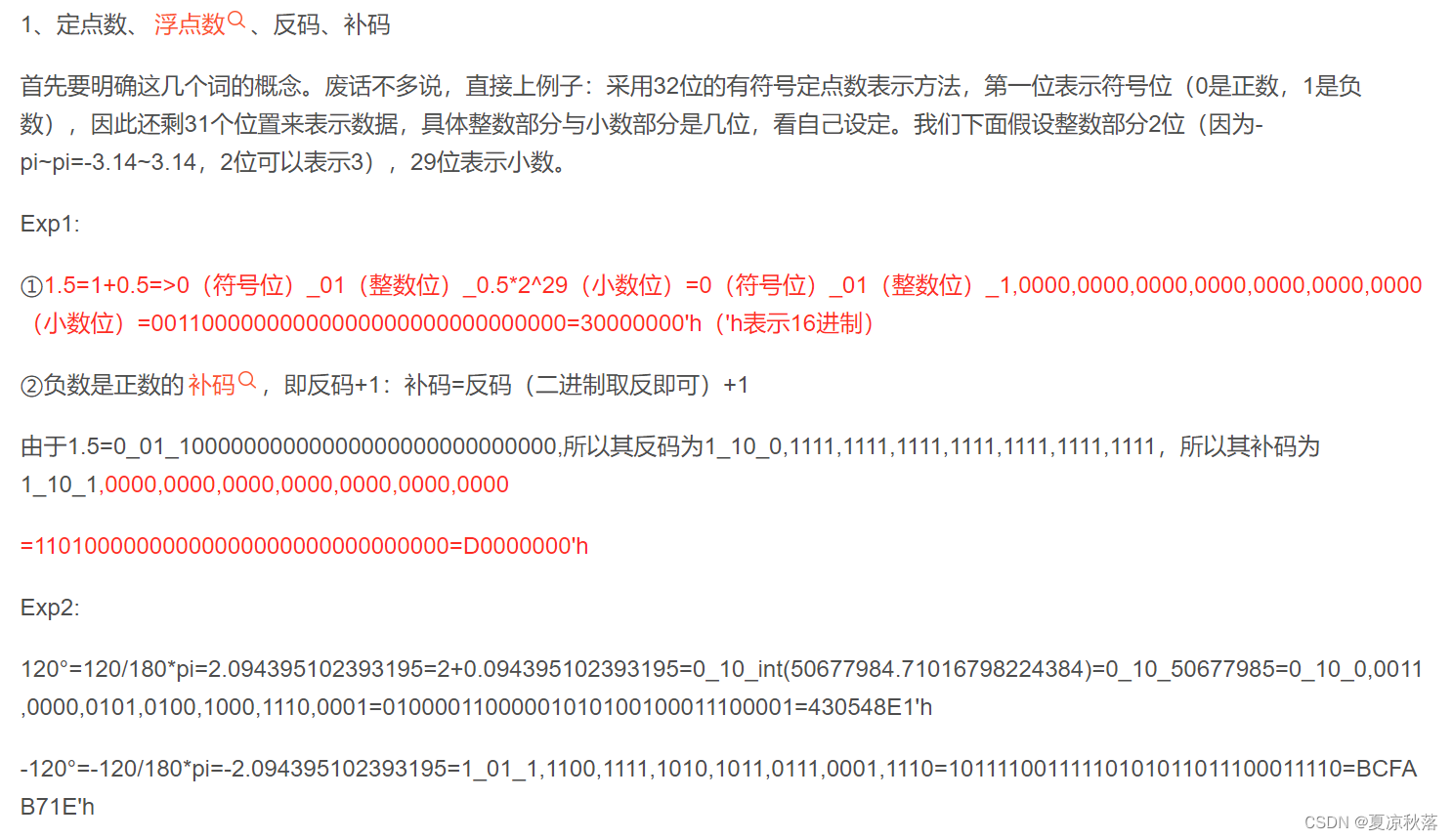

对于本例而言,输入数据的整数为2bit,输出数据的整数为3bit,均为有符号数。

总结: cordic ip核使用 时候通常情况下输入为【-1,1】,超过此范围会出错,因此,常用办法为,对原来数据的最高位进行扩一位符号位,再送入cordic ip核,或者代码中必定能要保证输入数据的范围限定在-1~1之间。若是不能肯定上级模块向CORDIC中输入数据的范围,能够先仿真,肯定数据的最大值和最小值是否超出了该范围。若是超过能够用相似“{q[15],q[15:1],i[15],i[15:1]}”这样的移位除法,缩小输入数据范围。因为是带符号数二进制补码,移位时注意高位补符号位。

五、参考资料

- VIVADO cordic IP核

- XILINX CORDIC IP核使用记录

- CORDIC(6.0) IP核 与 DDS Compiler(6.0) IP核 使用示例

- FPGA----IP核cordic使用

- VIVADO cordic IP核

- Cordic v6.0 IP CORE使用说明

- modelsim调试把信号显示为小数格式

- VIVADO cordic IP核(遇到的一些问题)

- FPGA数字信号处理(十四)Vivado Cordic IP核计算arctan(使用技巧)