目录

概述

1 双重 ADC 模式介绍

1.1 双重 ADC模式

1.2 双重 ADC 模式的类型

2 双重 ADC 模式寄存器的配置

3 模式功能实现

3.1 注入同步模式

3.2 支持独立注入的常规同步模式

3.2.1 中断的方式

3.2.2 DMA 读取常规数据

3.3 支持独立注入的交替模式

3.3.1 中断触发

3.3.2 DMA 传输常规数据

3.3.3 传输数据案例

3.3 交替触发模式

3.3.1 禁止注入不连续模式(两个 ADC 的 JDISCEN 均为 0)

3.3.2 使能注入不连续模式

3.4 混合型常规/注入同步模式

3.5 常规同步 + 交替触发组合模式

3.6 注入同步 + 交替组合模式

4 双重 ADC 模式下的 DMA 请求

4.1 DAMDF=0b10

4.2 DAMDF=0b10

4.3 DAMDF=0b11

4.4 溢出检测

4.5 选择多重 ADC 模式时的 DMA 单次模式/DMA 循环模式

4.6 停止双重 ADC 模式下的转换

4.7 双重 ADC 交替模式下的 DFSDM 模式

4.8 双重 ADC 同步模式下的 DFSDM 模式

概述

本文主要介绍STM32H750外设ADC之双重 ADC 模式,该模式下可以实现两个ADC模块同时进行数据转换,文中介绍了实现双重ADC转换的实现方法,原理,和寄存器的配置方式等。

1 双重 ADC 模式介绍

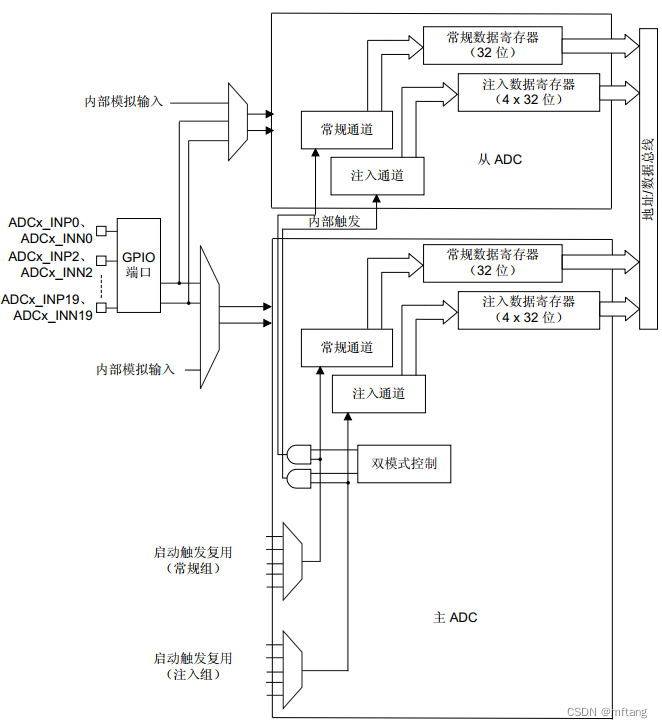

1.1 双重 ADC模式

如果器件配有两个或多个 ADC,可使用双重 ADC 模式:

1.2 双重 ADC 模式的类型

ADC1 与 ADC2 可在双重模式下共同使用( ADC1 为主器件)

在双重 ADC 模式下,通过 ADCx 主器件到 ADC 从器件的交替触发或同时触发来启动转换,具体取决于 ADCx_CCR 寄存器中的 DUAL[4:0] 位所选的模式。

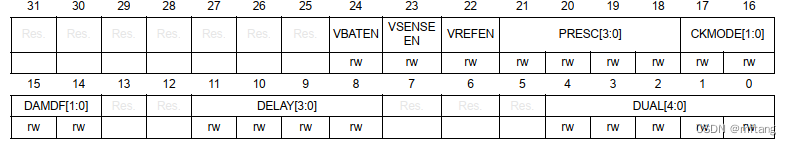

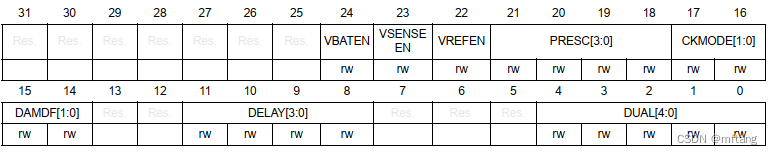

ADC x 通用控制寄存器 (ADCx_CCR)( x=12 或 3)

ADC x common control register

偏移地址: 0x08(该偏移地址与主 ADC 基址 + 0x300 相关)

复位值: 0x0000 0000ADC1 和 ADC2 由相同的接口控制,而 ADC3 单独控制

位 4:0 DUAL[4:0]: 双重 ADC 模式选择 (Dual ADC mode selection)

通过软件写入这些位可选择操作模式。

所有 ADC 均独立:

00000:独立模式

00001 到 01001:双重模式,主 ADC 与从 ADC 一起工作

00001:常规同步 + 注入同步组合模式

00010:常规同步 + 交替触发组合模式

00011:交错 + 注入同步组合模式

00100:保留

00101:仅注入同步模式

00110:仅常规同步模式

00111:仅交错模式

01001:仅交替触发模式

其它所有组合均需保留且不允许编程

可实现以下四种模式:

注入同步模式

常规同步模式

交替模式

交替触发模式

也可按以下方式组合使用这些模式:

注入同步模式 + 常规同步模式

常规同步模式 + 交替触发模式

注入同步模式 + 交替模式

2 双重 ADC 模式寄存器的配置

在双重 ADC 模式下( ADCx_CCR 寄存器中的 DUAL[4:0] 位不等于零时), ADCx_CFGR寄存器的 CONT、 AUTDLY、 DISCEN、 DISCNUM[2:0]、 JDISCEN、 JQM、 JAUTO 位会在主 ADC 与从 ADC 之间共享:从 ADC 中的位始终与主 ADC 的对应位相等。

要在双重模式下开始转换,用户必须仅对主 ADC 的 EXTEN、 EXTSEL、 JEXTEN、 JEXTSEL位进行编程,以配置软件或硬件触发以及常规或注入触发。(从 ADC 的 EXTEN[1:0] 和JEXTEN[1:0] 位为无关位)。

在常规同步或交替模式下:用户将主 ADC 的 ADSTART 位或 ADSTP 位置 1 后,从 ADC 的相

应位也会自动置 1。 但从 ADC 的 ADSTART 位或 ADSTP 位不需要与主 ADC 位同时清零。

在注入同步或交替触发模式下:用户将主 ADC 的 JADSTART 位或 JADSTP 位置 1 后,从ADC 的相应位也会自动置 1。 但从 ADC 的 JADSTART 位或 JADSTP 位不需要与主 ADC位同时清零。

在双重模式下,可通过读取 ADC 通用数据寄存器 (ADCx_CDR) 的方式同时读取主 ADC 和

从 ADC 的已转换数据。此外,还可以通过读取双重模式状态寄存器 (ADCx_CSR) 的方式同

时读取主 ADC 和从 ADC 的状态位。

3 模式功能实现

3.1 注入同步模式

通过将 DUAL[4:0] 位编程为 00101 来选择此模式。此模式可转换注入通道组。外部触发源来自主 ADC 的注入组多路复用器(通过 ADCx_JSQR寄存器中的 JEXTSEL[4:0] 位选择)。

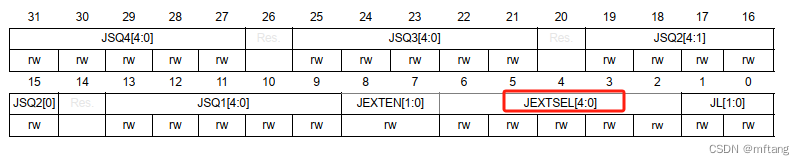

ADC x 注入序列寄存器 (ADCx_JSQR)( x=1 到 3)

ADC x injected sequence register

偏移地址: 0x4C

复位值: 0x0000 0000位 6:2 JEXTSEL[4:0]:注入组的外部触发选择 (External Trigger Selection for injected group)

这些位可选择用于触发注入组转换的外部事件。

00000:事件 0

00001:事件 1

00010:事件 2

00011:事件 3

00100:事件 4

00101:事件 5

00110:事件 6

00111:事件 7

...

11111:事件 31:

注: 不要在两个 ADC 上转换同一通道(转换同一通道时,不允许两个 ADC 采样时间重叠)。在同步模式下,转换的序列长度必须相同,并且在序列中,主器件和从器件的第 N 次转换必须配置为采用相同的采样时间。

常规转换可在一个或所有 ADC 上执行。这种情况下,它们彼此之间都是独立的,而且会在出现注入事件时中断。它们会在注入转换组结束时恢复转换。

当主 ADC 上出现注入转换序列结束 (JEOS) 事件时,已转换数据会存储到主 ADCx_JDRy寄存器中,并会产生 JEOS 中断(若使能)。

1)当从 ADC 上出现注入转换序列结束 (JEOS) 事件时,已转换数据会存储到从 ADCx_JDRy寄存器中,并会产生 JEOS 中断(若使能)。

2)如果主注入序列的持续时间与从注入序列的持续时间相等(如下图 所示),软件可以只使能两个 JEOS 中断中的一个(例如:主 JEOS)并读取两者的已转换数据(从主ADCx_JDRy 和从 ADCx_JDRy 寄存器中读取)。

如果 JDISCEN=1,注入序列的每个同步转换都需要在出现一个注入触发事件后才能进行。该模式可与 AUTDLY 模式结合使用:

1)转换的同步注入序列结束后,仅当主 ADC 和从 ADC 的 JEOS 位均已清零时,才会接受新的注入触发事件(延时阶段)。如果在进行的注入序列中以及关联的延时阶段出现新的注入触发事件,则会被忽略。

2)主 ADC 的常规转换序列结束后,仅当已读取主数据寄存器 (ADCx_DR) 时,才会接受主ADC 的新常规触发事件。如果在进行的常规序列中以及关联的延时阶段出现关于主ADC 的新常规触发事件,则会被忽略。

在从 ADC 上发生的常规序列也是如此。

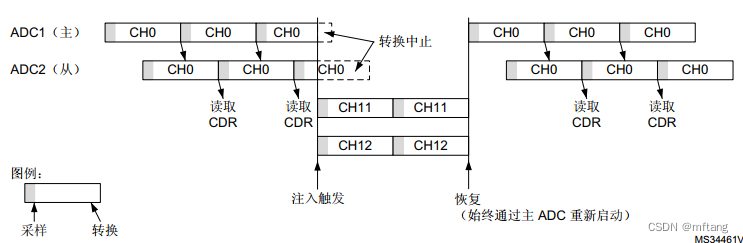

3.2 支持独立注入的常规同步模式

通过将 DUAL[4:0] 位编程为 00110 来选择此模式。此模式可用于常规通道组。外部触发源来自主 ADC 的常规组多路复用器(通过 ADCx_CFGR寄存器中的 EXTSEL[4:0] 位选择)。同时触发可用于从 ADC。在该模式下,支持独立注入转换。注入请求(主 ADC 或从 ADC 上)将中止当前的同步转换,并在注入转换结束后重新开始该同步转换。

注: 不要在两个 ADC 上转换同一通道(转换同一通道时,不允许两个 ADC 采样时间重叠)。在常规同步模式下,转换的序列长度必须相同,并且在序列中,主器件和从器件的第 N 次转换必须配置为采用相同的采样时间。

3.2.1 中断的方式

当软件可读取数据时,会通过中断的方式获得通知:

1) 每次主 ADC 上出现转换结束事件时 (EOC),会产生主 EOC 中断(若使能 EOCIE),软件可读取主 ADC 的 ADCx_DR。

2)每次从 ADC 上出现转换结束事件时 (EOC),会产生从 EOC 中断(若使能 EOCIE),软件可读取从 ADC 的 ADCx_DR。

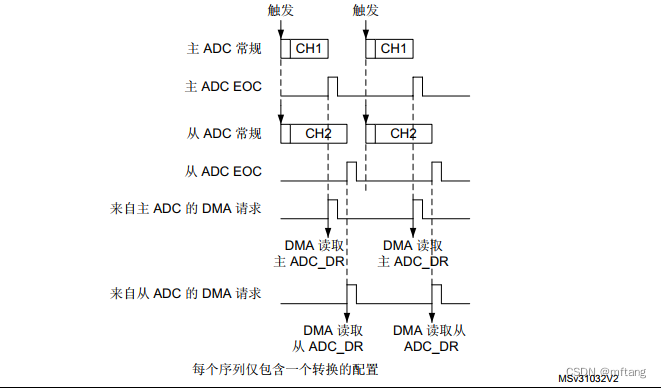

3)如果主常规序列的持续时间与从常规序列的持续时间相等(如图 178 所示),软件可以只使能两个 EOC 中断中的一个(例如:主 EOC)并从通用数据寄存器 (ADCx_CDR)中读取两者的已转换数据。

3.2.2 DMA 读取常规数据

此外,还可以使用 DMA 读取常规数据,具体通过以下两种方法来实现:

1)使用两条 DMA 通道(一条用于主 ADC,另一条用于从 ADC)。在这种情况下,必须使

DAMDF[1:0] 位保持清零。

– 将 DMA 主 ADC 通道配置为读取主 ADC 的 ADCx_DR。每次主 ADC 上出现 EOC事件时,都会生成 DMA 请求。

– 将 DMA 从 ADC 通道配置为读取从 ADC 的 ADCx_DR。每次从 ADC 上出现 EOC事件时,都会生成 DMA 请求。

2)配置双重 ADC 模式数据格式 DAMDF[1:0] 位,留下一条 DMA 通道用于其他用途:

– 配置 DAMDF[1:0]=0b10 或 0b11(具体取决于分辨率)。

– 使用一条 DMA 通道(主 ADC 的一条通道)。将 DMA 主 ADC 通道配置为读取通用 ADC 寄存器 (ADCx_CDR)。

– 每次同时出现主 EOC 事件和从 EOC 事件时,都会生成单次 DMA 请求。此时,从ADC 转换的数据会出现在 ADCx_CDR 32 位寄存器的高位半字中,主 ADC 转换的数据会出现在 ADCx_CCR 寄存器的低位半字中。

– DMA 读取 ADCx_CCR 寄存器时,两个 ECO 标志都会清零。

注: DAMDF[1:0]=0b10 或 0b11 时,用户必须将主序列和从序列中的转换次数编程为相同值。否则,多余的转换将不会生成 DMA 请求。

如果 DISCEN=1,常规序列的每“n”个同步转换都需要在出现一次常规触发事件后才能进行(“n”由 DISCNUM 定义)。该模式可与 AUTDLY 模式结合使用:

1)序列的同步转换结束后,仅当通用数据寄存器 ADCx_CDR(或主 ADC 的常规数据寄存器)已被读取时,才会开始序列中的下一个转换(延时阶段)。

2)转换的同步常规序列结束后,仅当通用数据寄存器 (ADCx_CDR) 已被读取时,才会接受新的常规触发事件(延时阶段)。如果在进行的常规序列中以及关联的延时阶段出现新的常规触发事件,则会被忽略。可以使用 DMA 在常规同步与 AUTDLY 组合模式下处理数据,前提是使用多重 DMA 模式:DAMDF 位必须设为 0b10 或 0b11。

ADC x 通用控制寄存器 (ADCx_CCR)( x=12 或 3)

ADC x common control register

偏移地址: 0x08(该偏移地址与主 ADC 基址 + 0x300 相关)

复位值: 0x0000 0000

ADC1 和 ADC2 由相同的接口控制,而 ADC3 单独控制。

位 15:14 DAMDF[1:0]: 双重 ADC 模式数据格式 (Dual ADC Mode Data Format)

此位域由软件置 1 和清零。它指定通用该数据寄存器 ADCx_CDR 中的数据格式。

00:双重 ADC 模式,无数据封装(未使用 ADCx_CDR 和 ADCx_CDR2 寄存器)。

01:保留

10:数据格式化模式,用于 32 位到 10 位分辨率

11:数据格式化模式,用于 8 位分辨率

如果常规同步模式与 AUTDLY 模式相结合使用,用户必须确保:

1)主序列中的转换次数必须与从序列中的转换次数相等。

2)对于序列的每个同步转换,从 ADC 的转换长度要小于主 ADC 的转换长度。请注意,序列长度取决于要转换的通道数目以及每条通道的采样时间和分辨率。

注: 仅当只编程了常规通道时,才可以将常规同步模式与 AUTDLY 模式结合使用:禁止在该组合模式下对注入通道进行编程。

3.3 支持独立注入的交替模式

3.3.1 中断触发

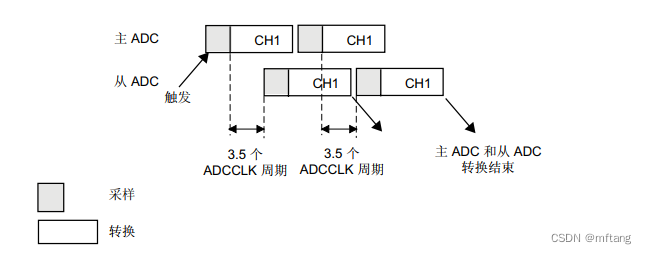

通过将 DUAL[4:0] 位编程为 00111 来选择此模式。此模式只能用于常规组(通常为一个通道)。外部触发源来自主 ADC 的常规通道多路复用器。

出现外部触发之后:

1)主 ADC 立即启动。

2)从 ADC 在主 ADC 采样阶段完成后的多个 ADC 时钟周期延时后启动。

交替模式下 2 个转换之间的最小延迟通过 ADCx_CCR 寄存器中的 DELAY 位进行配置。该延时会在主转换的采样阶段结束后开始计时。这样一来,如果某个 ADC 的互补 ADC 仍在对其输入进行采样,则该 ADC 无法启动转换(在给定时间内,只有一个 ADC 能够对输入信号采样)。

1)可能的最小延时为 1,用以确保主 ADC 采样阶段模拟开关断开与从 ADC 采样阶段模拟开关闭合之间至少有一个周期时间。

2)最大延时与所选分辨率对应的周期数相等。但用户必须正确计算该延时,以确保在某个ADC 仍在对其输入进行采样时不会有其他 ADC 开始转换。

如果主 ADC 和从 ADC 上的 CONT 位均置 1,则这两个 ADC 所选常规通道会连续进行转换。每次从 ADC 上出现转换结束事件时 (EOC),都会在软件能够读取数据时以中断方式通知软件,会产生从 EOC 中断和主 EOC 中断(若使能 EOCIE),软件可读取从/ 主 ADC 的ADCx_DR。

3.3.2 DMA 传输常规数据

在这种情况下,不能在每个 ADC 上使用单次 DMA请求,务必使用 MDMA 模式,方法如下:

1)配置 DAMDF[1:0]=0b10 或 0b11(具体取决于分辨率)。

2)使用一条 DMA 通道(主 ADC 的一条通道)。将 DMA 主 ADC 通道配置为读取通用 ADC寄存器 (ADCx_CDR)。

3)每次同时出现主 EOC 事件和从 EOC 事件时,都会生成单次 DMA 请求。此时,从 ADC转换的数据会出现在 ADCx_CDR 32 位寄存器的高位半字中,主 ADC 转换的数据会出现在 ADCx_CCR 寄存器的低位半字中。

3.3.3 传输数据案例

1)连续转换模式下 1 通道的交替模式:双重 ADC 模式

2) 单次转换模式下 1 通道的交替模式:双重 ADC 模式

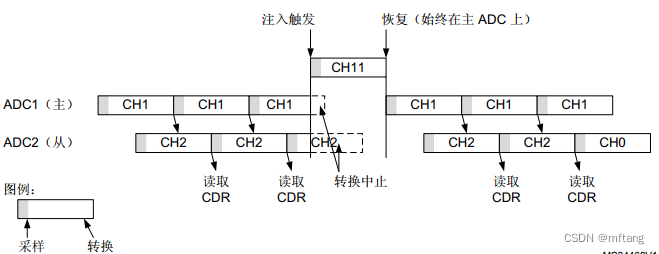

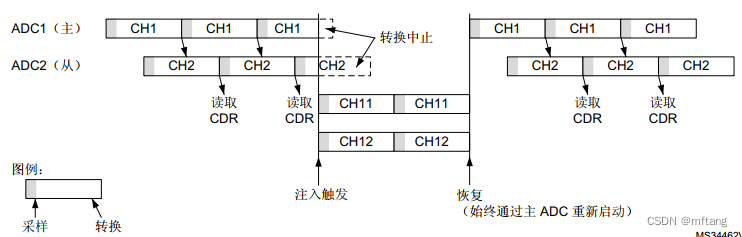

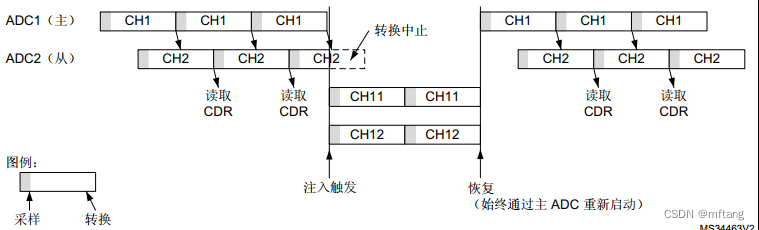

如果 DISCEN=1,常规序列的每“n”(“n”由 DISCNUM 定义)个同步转换需要在出现一个常规触发事件后才能进行。在该模式下,支持注入转换。注入完成后(在主 ADC 或从 ADC 上),主常规转换和从常规转换都会中止,序列会从主 ADC 重启(请参见下文中的图 )。

3.3 交替触发模式

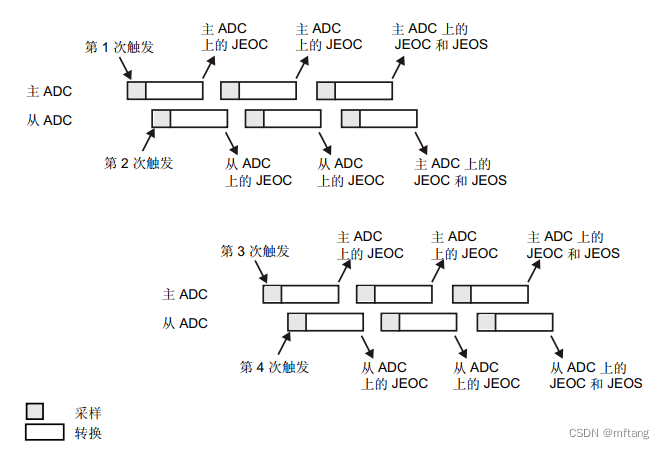

通过将 DUAL[4:0] 位编程为 01001 来选择此模式。此模式只能用于注入组。外部触发源来自主 ADC 的注入组多路复用器。仅当选择了硬件触发时,才能使用此模式: JEXTEN 不得为 0x0。

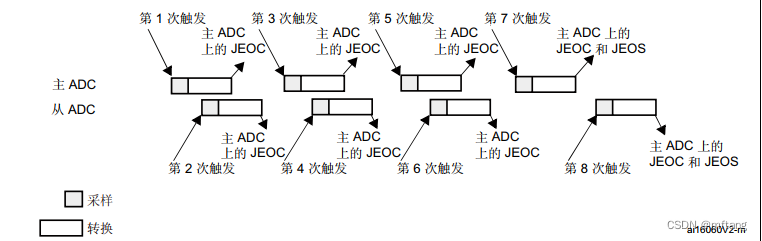

3.3.1 禁止注入不连续模式(两个 ADC 的 JDISCEN 均为 0)

1. 发生第一次触发时,将转换组中主 ADC 的所有注入通道。

2. 发生第二次触发时,将转换组中从 ADC 的所有注入通道。

3. 以此类推。

当组中主 ADC 的所有通道都转换完成后,会生成一个 JEOC 中断(如果已使能)。当组中从 ADC 的所有通道都转换完成后,会生成一个 JEOC 中断(如果已使能)。每次注入转换后也会生成 JEOC 中断(如果已使能)。如果在组中的所有注入通道都完成转换后出现另一个外部触发,则可通过转换组中主 ADC的注入通道来重新启动交替触发过程。

3.3.2 使能注入不连续模式

使能注入不连续模式(两个 ADC 的 JDISCEN 均为 1)如果使能主 ADC 和从 ADC 的注入不连续模式:

发生第一次触发时,将转换主 ADC 的第一条注入通道。

发生第二次触发时,将转换从 ADC 的第一条注入通道。

以此类推。

当组中主 ADC 的所有通道都转换完成后,会生成一个 JEOC 中断(如果已使能)。

当组中从 ADC 的所有通道都转换完成后,会生成一个 JEOC 中断(如果已使能)。

每次注入转换后也会生成 JEOC 中断(如果已使能)。

如果注入组中的所有通道都完成转换后出现另一个外部触发,则会重新启动交替触发过程。

3.4 混合型常规/注入同步模式

通过将 DUAL[4:0] 位编程为 00001 来选择此模式。

可以中断常规组的同步转换,然后开始注入组的同步转换。

注: 转换的序列长度必须相同,并且在给定序列中,主模式和从模式的第 N 次转换必须配置为采

用相同的采样时间,或必须确保触发之间的间隔长于 2 个序列的长转换时间。如果不遵循上述条件,当序列较长的 ADC 完成上一次转换时,序列较短的 ADC 可能重新开始转换。

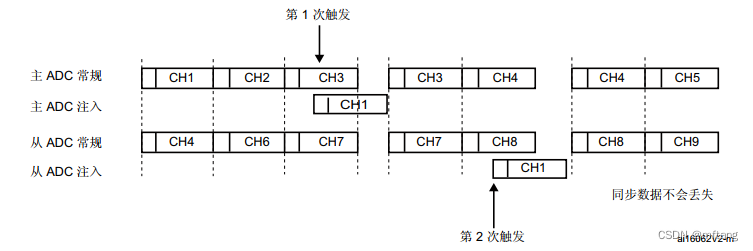

3.5 常规同步 + 交替触发组合模式

通过将 DUAL[4:0] 位编程为 00010 来选择此模式。

可以中断常规组的同步转换,然后开始注入组的交替触发转换。 图 184 说明了交替触发模式中断同步常规转换的行为。注入事件后立即开始注入交替转换。当常规转换处于运行状态时,为确保在注入转换后实现同步,所有的(主/从) ADC 常规转换均将停止,并会在注入转换结束时得以恢复运行。

注: 转换的序列长度必须相同,并且在给定序列中,主模式和从模式的第 N 次转换必须配置为采用相同的采样时间,或必须确保触发之间的间隔长于 2 个序列的长转换时间。如果不遵循上述条件,当序列较长的 ADC 完成上一次转换时,序列较短的 ADC 可能重新开始转换。

如果在已导致常规转换中断的注入转换期间出现交替触发,则会得到处理。 图显示了这种情况下的操作(请注意,由于与第 6 次触发相关联的交替转换未完成,因此会忽略第 6 次触发)。

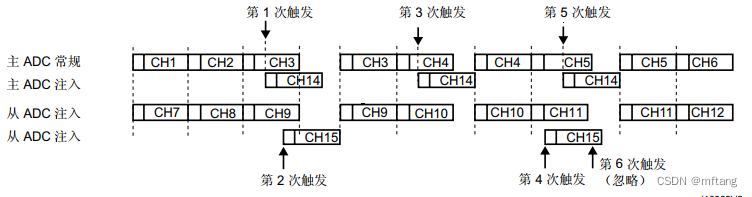

3.6 注入同步 + 交替组合模式

通过将 DUAL[4:0] 位编程为 00011 来选择此模式。可以通过同步注入事件中断交替转换。在这种情况下,交替转换会立即中断,同步注入转换会开始。注入序列结束时,会恢复交替转换。交替常规转换恢复后,执行的第一个常规转换始终是主 ADC 的常规转换。

注意: 在该模式下,必须使用通用数据寄存器以单次读访问的形式读取常规数据。但是,主从数据的一致性无法得到保证。

1)单条交替通道 CH0,注入序列 CH11 和 CH12

2) 两条交替通道( CH1、 CH2),注入序列 CH11 和 CH12 - 情况 1:先中断主 ADC

3) 两条交替通道( CH1、 CH2),注入序列 CH11 和 CH12 - 情况 2:先中断从 ADC

4 双重 ADC 模式下的 DMA 请求

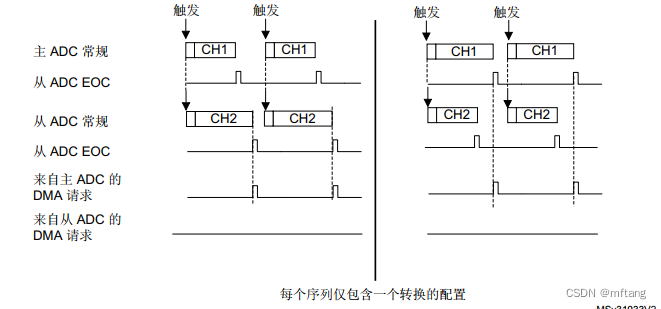

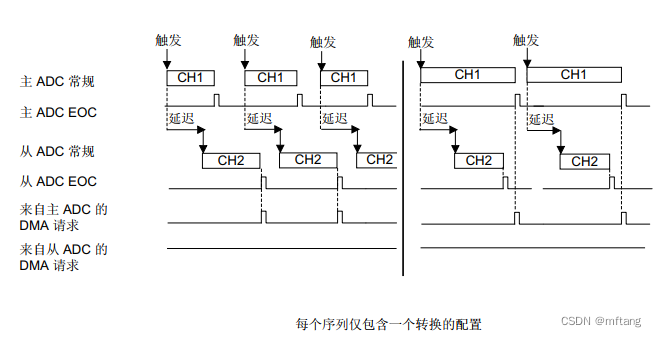

在所有双重 ADC 模式下,可以使用两条 DMA 通道(一条用于主 ADC,一条用于从 ADC)来传输数据,与在单模式下一样(请参见下图 :常规同步模式下的 DMA 请求( DAMDF=0b00 时) )。

在同步常规模式和交替模式下,还可以保留一条 DMA 通道而使用单条 DMA 通道传输两者

的数据。为此,必须配置 ADCx_CCR 寄存器中的 DAMDF 位:

4.1 DAMDF=0b10

DAMDF=0b10, 32 位格式:出现主 EOC 事件或从 EOC 事件时,会交替生成单次 DMA请求。此时,数据项会交替出现在 ADCx_CDR2 32 位寄存器中。当分辨率高于 16 位时,该模式用于交替模式和常规同步模式。

示例:

双重交替模式:每当有新的 32 位数据可用时,就会生成一个 DMA 请求:

第一个 DMA 请求: ADCx_CDR2[31:0] = MST_ADCx_DR[31:0]

第二个 DMA 请求: ADCx_CDR2[31:0] = SLV_ADCx_DR[31:0]

4.2 DAMDF=0b10

DAMDF=0b10, 16 位格式:每当同时出现主 EOC 事件和从 EOC 事件时,都会生成单次 DMA 请求。此时有两个数据项可用, 32 位寄存器 ADCx_CDR 包含的两个半字代表两个经过 ADC 转换的数据项。从 ADC 数据占用高位半字,主 ADC 数据占用低位半字。

当分辨率介于 10 位和 16 位之间时,该模式用于交替模式和常规同步模式。如果主转换

器或从转换器中的值大于 16 位,则会被截断为 16 个最低有效位。

示例:

双重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求:

第一个 DMA 请求: ADCx_CDR[31:0] = SLV_ADCx_DR[15:0] |MST_ADCx_DR[15:0]

第二个 DMA 请求: ADCx_CDR[31:0] = SLV_ADCx_DR[15:0] |MST_ADCx_DR[15:0]

1)常规同步模式下的 DMA 请求( DAMDF=0b10 时

2) 交替模式下的 DMA 请求( DAMDF=0b10 时)

4.3 DAMDF=0b11

DAMDF=0b11:该模式与 DAMDF=0b10 时相似。唯一的区别是:在这种模式下,每发送一个 DMA 请求(两个数据项可用),就会以半字的形式传输表示两个 ADC 转换数据项的两个字节。

当结果为 8 位时,该模式用于交替模式和常规同步模式。当有 4 个新的 8 位值可用时,会发出新的 DMA 请求。

示例:

双重交替模式:每当有 4 个数据项可用时,就会生成一个 DMA 请求( t0、 t1... 对应于连续的采样点)

第一个 DMA 请求:

ADCx_CDR[7:0] = MST_ADCx_DR[7:0]t0

ADCx_CDR[15:8] = SLV_ADCx_DR[7:0]t0

ADCx_CDR[23:16] = MST_ADCx_DR[7:0]t1

ADCx_CDR[31:24] = SLV_ADCx_DR[7:0]t1

第二个 DMA 请求:

ADCx_CDR[7:0] = MST_ADCx_DR[7:0]t2

ADCx_CDR[15:8] = SLV_ADCx_DR[7:0]t2

ADCx_CDR[23:16] = MST_ADCx_DR[7:0]t3

ADCx_CDR[31:24] = SLV_ADCx_DR[7:0]t3

4.4 溢出检测

在双重 ADC 模式下( DUAL[4:0] 不等于 b00000 时),如果在其中一个 ADC 上检测到溢出,将不再发出 DMA 请求,以确保传输到 RAM 的所有数据均有效(无论 DAMDF 采用何种配置,都具有此特性)。对于与某个 ADC 对应的 EOC 位,有时可能会因为此 ADC 的数据寄存器包含有效数据而保持置 1。

4.5 选择多重 ADC 模式时的 DMA 单次模式/DMA 循环模式

如果选择 DAMDF 模式( 0b10 或0b11),还必须将主 ADC 的 ADCx_CCR 寄存器中的DMNGT[1:0] 位配置为 0b10,以在 DMA 单次模式和 DMA 循环模式之间进行选择,请参见使用 DMA 管理转换一节。

4.6 停止双重 ADC 模式下的转换

用户必须将主 ADC 的控制位 ADSTP/JADSTP 置 1,以停止双重 ADC 模式下两个 ADC 的转换。从 ADC 的另一控制位 ADSTP 在双重 ADC 模式下不起作用。

两个 ADC 均有效停止后,主 ADC 和从 ADC 的 ADSTART/JADSTART 均会通过硬件清零。

4.7 双重 ADC 交替模式下的 DFSDM 模式

在双重 ADC 交替模式下, ADC 转换结果可直接传送到具有 Σ∆ 调制器的数字滤波器(DFSDM)。此模式通过将主 ADC 的 ADCx_CFGR 寄存器中的 DMNGT[1:0] 位设为 0b10 来使能。ADC 将常规数据寄存器的 16 个最低有效位交替地从主转换器和从转换器传送至 DFSDM 的一条通道。

数据必须为 16 位有符号格式:

ADCx_DR[31:16] = 0x0000

ADCx_DR[15] = 符号

ADCx_DR[14:0] = 数据

如果任何转换器中存在超出 16 位有符号格式的值,则会被截断。

4.8 双重 ADC 同步模式下的 DFSDM 模式

在双重 ADC 同步模式下使用 DFSDM 无需双重模式,因为转换数据将由每个单独的通道处理。具有相同触发源的单一模式会导致使用 DFSDM 接口进行同步转换。