注释:了解pcie的硬件接口,lanes,link,串行,并行,包结构

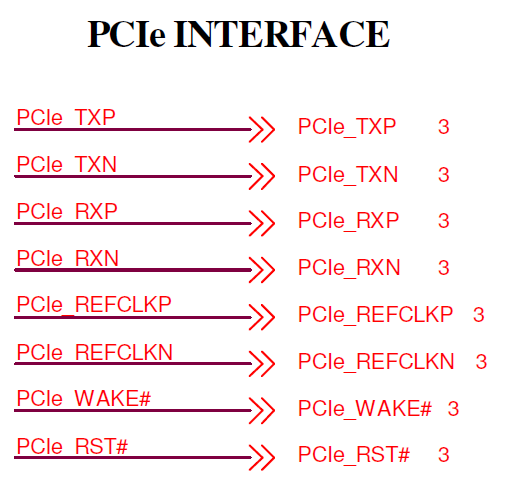

1、PCIe硬件接口引脚

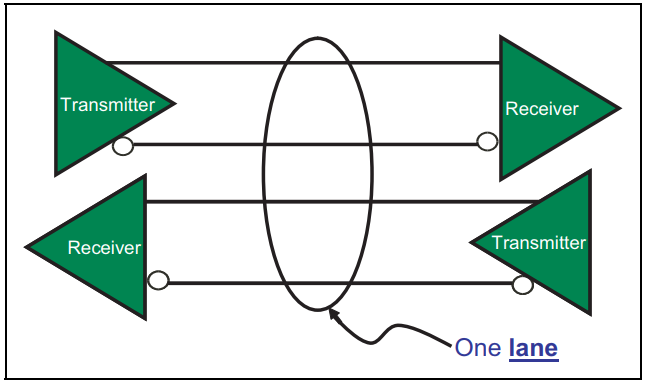

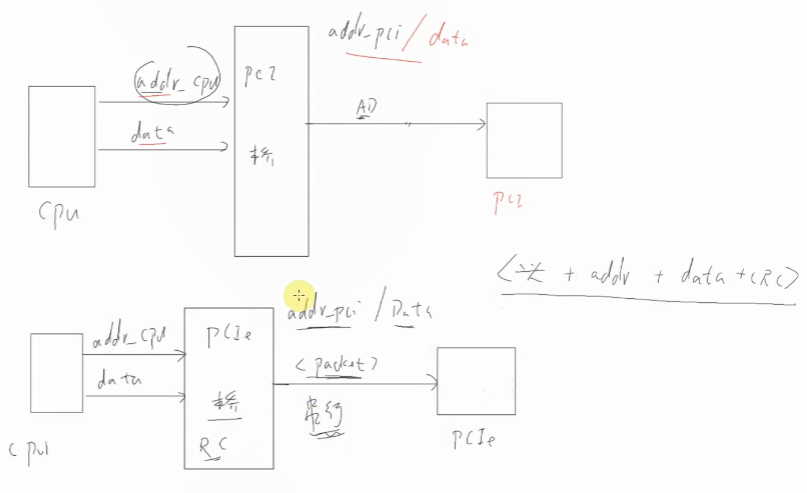

通过差分信号TX+ TX-和RX+ RX-信号发生接收数据。这4条信号称为一个lane。每个方向两条线来传输。在1个lane里面有发送和接收两个方向。两个PCIE设备之间称为1个link。下图是pcie硬件结构引脚电路示意图。回顾之前的pci接口引脚电路图,发现具有的引脚明显比较多,有AD0-AD31等。随着时钟频率的增加,并行引脚会引入很多问题,因此引入串行引脚的设计方式。

PCIE接口的引脚是并行的。PCIe的是串行的。每个方向的数据使用2条差分信号来传输,发送接收两个方向就需要4条线,这被称为1个lane。

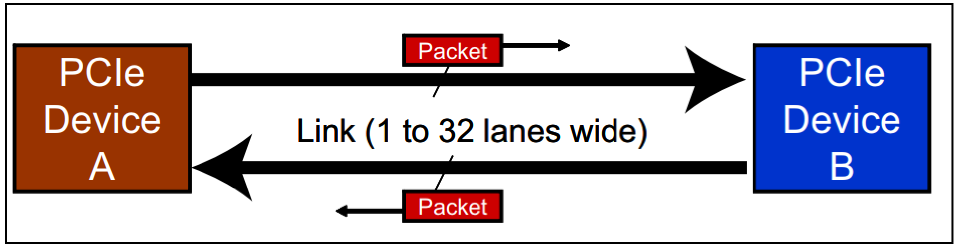

一般PCIe设备的接口,可以有多个lane。

- 两个PCIe设备之间一个link。

- 一个link中有1对或者多对发送接收引脚,其中每对引脚称为一个lane

- 一个lane:有发送、接收两个方向,每个方向用2条查分信号线,所以1个lane有4条线

- 一个link最多可以有32lane。

PCI和PCIe进行传输的时候对比,由于PCI上可以通过AD总线发送地址和,而在PCIE上需要使用串行将多个信息组成包的形式发送出去。对于CPU一侧编程来说,不需要关心是PCI或者pcie,电信号的发送都是有RC来处理。

2、从软件角度理解硬件接口

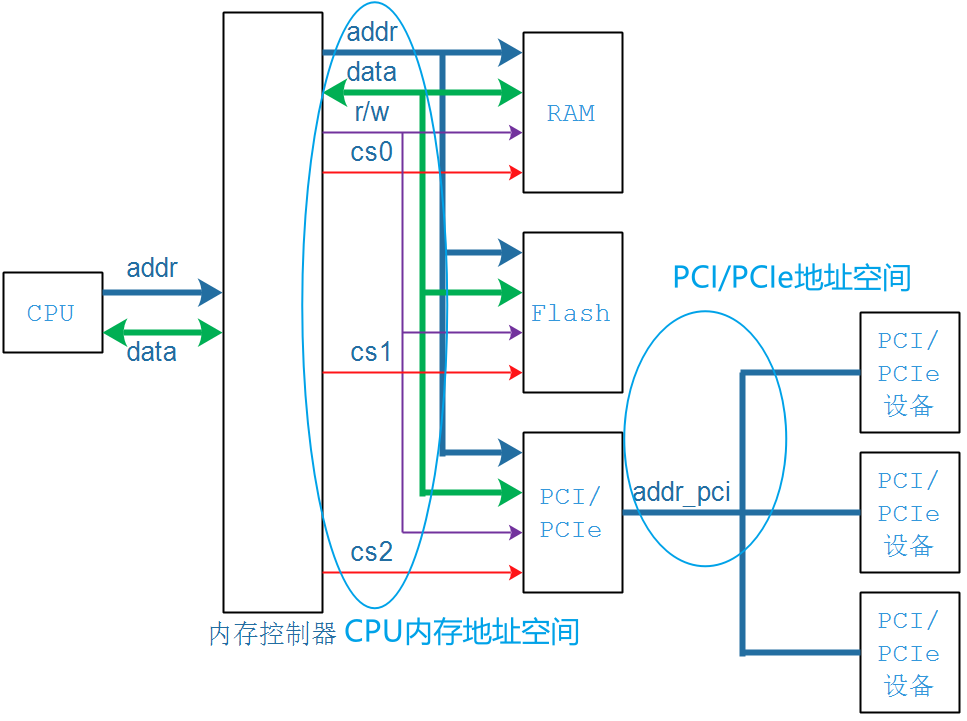

2.1 PCI/PCIe地址空间转换

CPU发出的地址会经过桥转换成PCIe空间的地址。在PCI中地址和数据通过并行发送给设备,现在pcie中通过串行信号线发送。此时信号线上包括地址和数据。如何区分呢?相当于组报文的形式规则。

2.2 PCIe上如何传输地址、数据

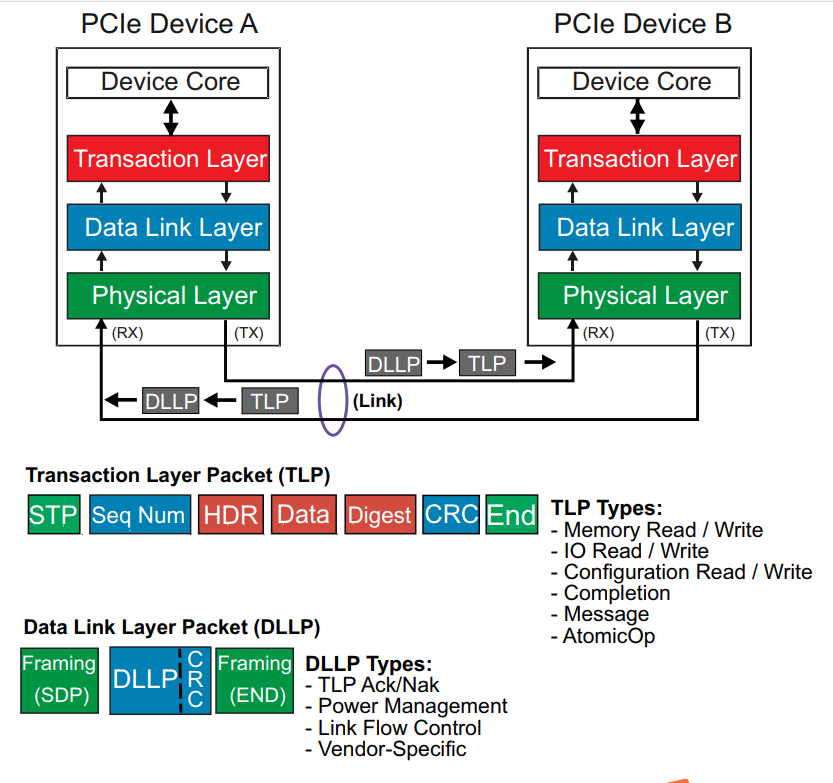

既然PCIE是串行的,那只能在包里传输地址和数据了。

- 需要定义包的格式:类型(Mem R/W) + 地址 + 数据

- 包怎么传递给对方、怎么确保不出错?有重传机制、有检验码

- 包怎么通过差分线传送出去?

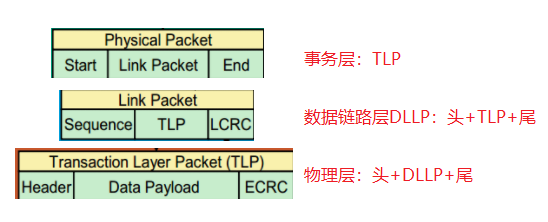

PCIe总线的层次结构和数据包:

- 事务层Trasaction layer:传输的是TLP(transaction layer packet)。一般只有头部+原始数据+CRC组成。头部又包括读类型,读地址等等。

- 数据链路层:传输的是DLLP(data link layer packet)。一般是在TLP上加头(序列号)加尾(CRC校验)得到。

- 物理层(physical layer):传输的是物理包。一般是在DLLP上加头加尾得到。

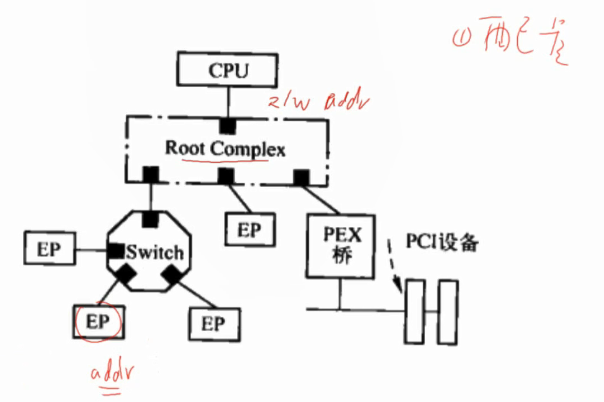

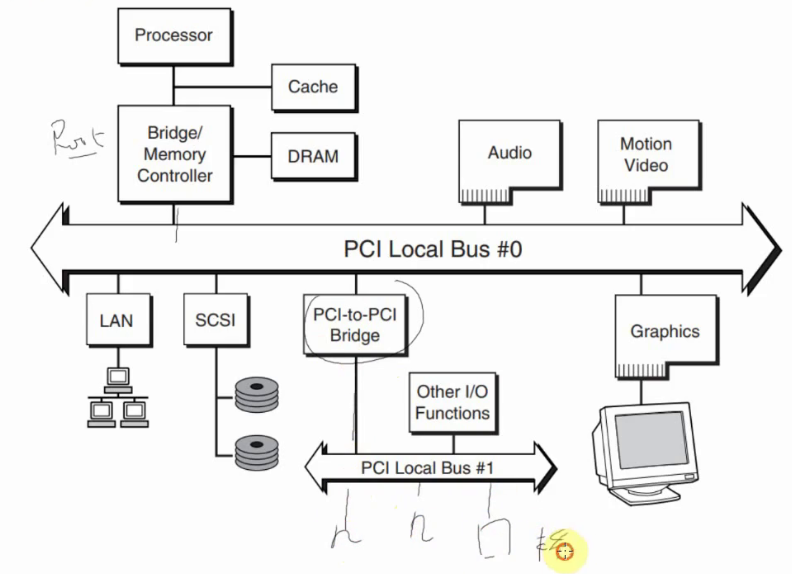

3、PCIe系统硬件框图

先对比了之前学习的PCI设备, PCI上桥可以挂多个设备,但是在PCIe中,只能挂1个pcie设备。

在PCIe系统里,是点对点传输的:

- 一条PCIe总线只能接一个PCIe设备(相当于Root Complex内部有多个P2P的桥-他们也有自己的BDF,也可以理解为一个设备)

- 要接多个PCIe设备,必须使用Switch进行扩展

- PCIe设备的配置流程和PCI设备的基本相似:先去配置每个设备的地址访问,也就是向他的寄存器中写明需要占用多大的空间,后面CPU发出的地址设备就能判断是否属于自己的地址,然后做出反馈。