本教程演示如何在DE1-SOC开发板上创建一个基于Nios V 的SOPC系统,并在系统上运行Nios V软件工程。

一、Nios V简介

Nios V处理器是基于RISC-V规范的软知识产权(IP)处理器。

Nios V处理器系统相当于一个微控制器(或“芯片级计算机”),其中包括处理器以及单芯片上的外设和内存组合。Nios®V处理器系统由一个Nios V处理器内核、一组片内外设、片内存储器和片外存储器的接口组成,所有这些都集成在Intel FPGA芯片上进行实现。与微控制器类似,所有的Nios V处理器系统都使用一致的指令集和编程模型。

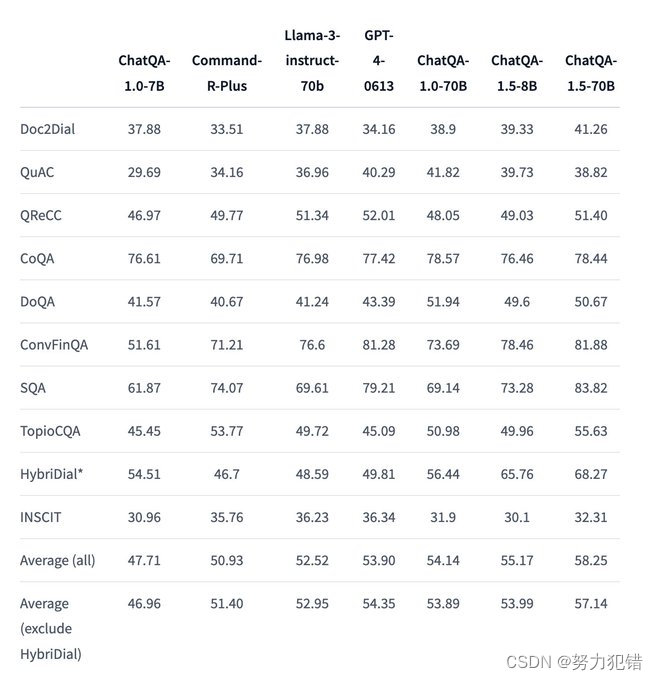

目前Intel推出了三款Nios® V处理器(图片来自Intel 官网):

(点击图可放大)

从截图可以看到这里面功能最强的是Nios V/g IP,用户可根据实际需求选择对应的软核。不过对于Cyclone V器件目前只支持Nios V/m软核。Agilex V等器件则支持以上三种软核。

Nios V/m处理器性能:

Nios®V/m处理器是Intel基于RISC-V指令集开发的微控制器核心。

Nios®V/m处理器支持两种不同的配置:

-

流水线

-

应用RV32IZicsr指令集。

-

支持五阶段流水线数据通路。

2. 非流水线

-

应用RV32IZicsr指令集。

-

支持非流水线数据通路。

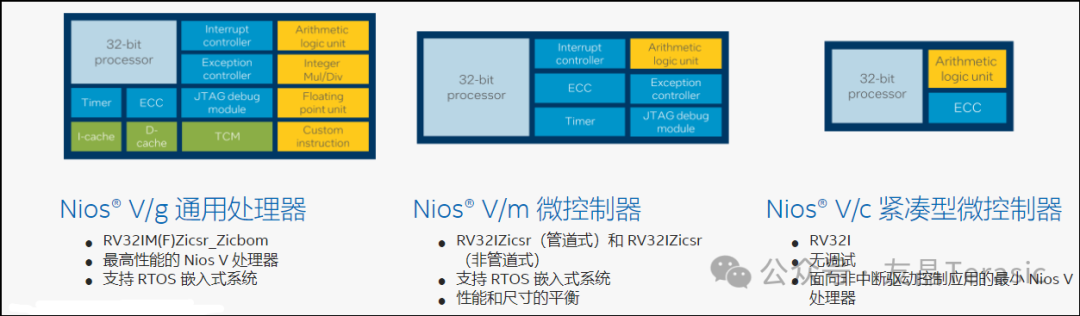

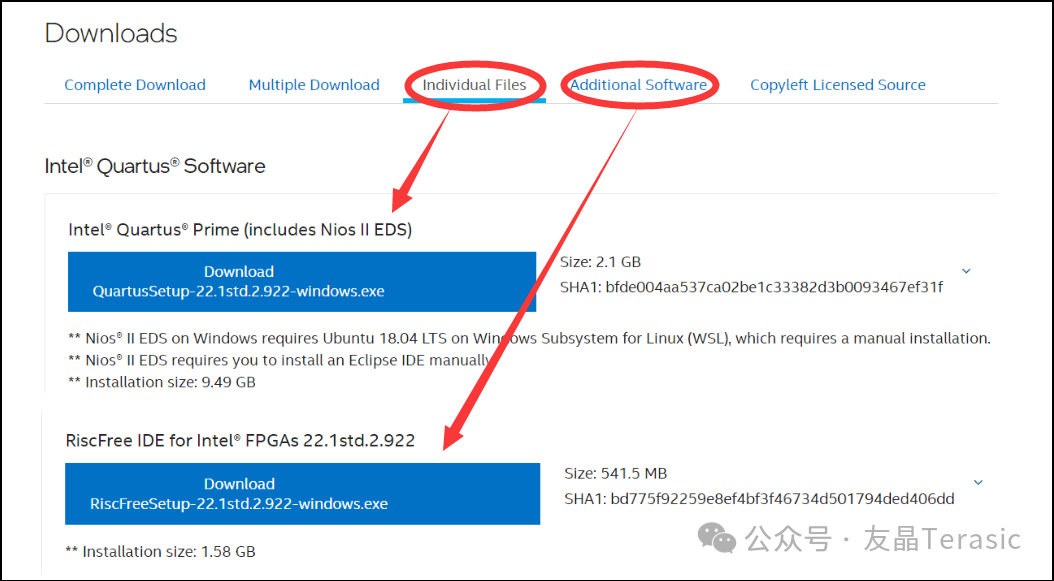

二、SOPC开发流程

在Quartus Prime完成嵌入式系统的硬件部分,在RiscFree IDE中完成NiosV软件部分。基于Nios V 的SOPC 的开发流程其实和以前Nios II 的流程是一样的,以下是Nios II 的开发流程:

本文具体会使用Quartus软件中的Platform Designer系统集成工具创建一个基于Nios V的FPGA硬件系统工程(一个简单的LED控制电路),将编译产生的sof编程文件下载到FPGA 中,然后使用Ashling RiscFree IDE创建Nios v软件工程——my_first_niosv(给LED提供控制信号),最后将软件编译产生的.elf可执行文件下载到DE1-SOC开发板。

在这个设计当中,除了可以直接在FPGA开发板上观察LED的现象,还可以在Nios V terminal上查看打印信息(这是因为Nios V软件程序要打印的信息通过JTAG UART传输到PC上,并在Nios V terminal进行了显示。)

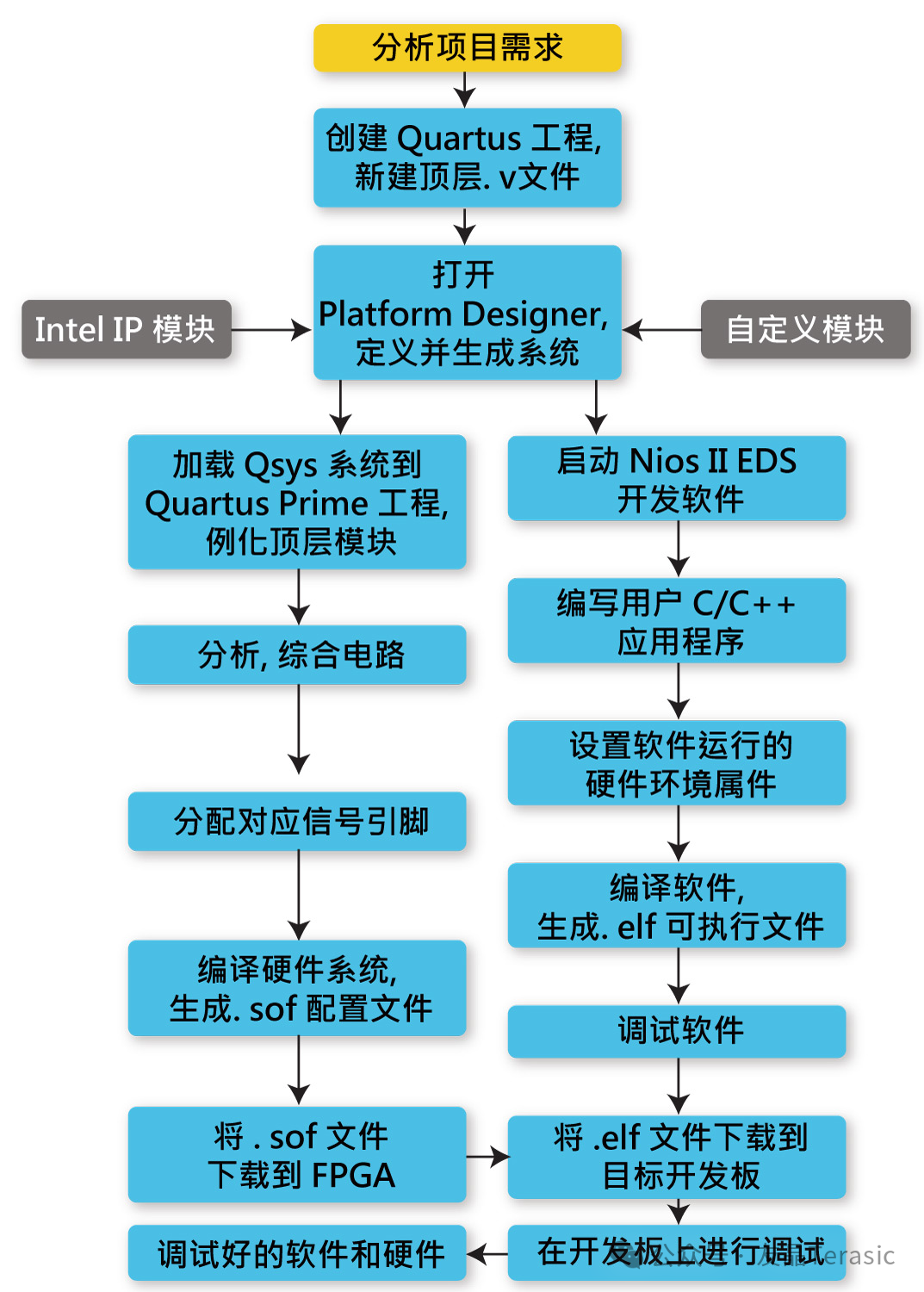

三、开发工具下载

目前Quartus Prime Standard版从 22.1及以上版本都支持Nios V了,而且这些版本也支持Cyclone V器件。Quartus Prime Pro版从22.2及以上版本都支持Nios V ,但Pro版不支持Cyclone V器件。

本文以22.1.2版本为例进行操作演示。

1. Quartus Prime v22.1.2 Standard Edition 和对应的Ashling RiscFree IDE下载链接:https://www.intel.com/content/www/us/en/software-kit/785052/intel-quartus-prime-standard-edition-design-software-version-22-1-2-for-windows.html

备注1:点击Individual Files找到QuartusSetup-22.1std.2.922-windows.exe文件并下载

备注2:点击Additional Software找到RiscFreeSetup-22.1std.2.922-windows.exe文件并下载

2. Quartus以及Nios® V/m Embedded Processor的license,在Intel [Self Service Licensing Center]可免费申请,申请步骤可参考链接(点击跳转),使用期限是90天。

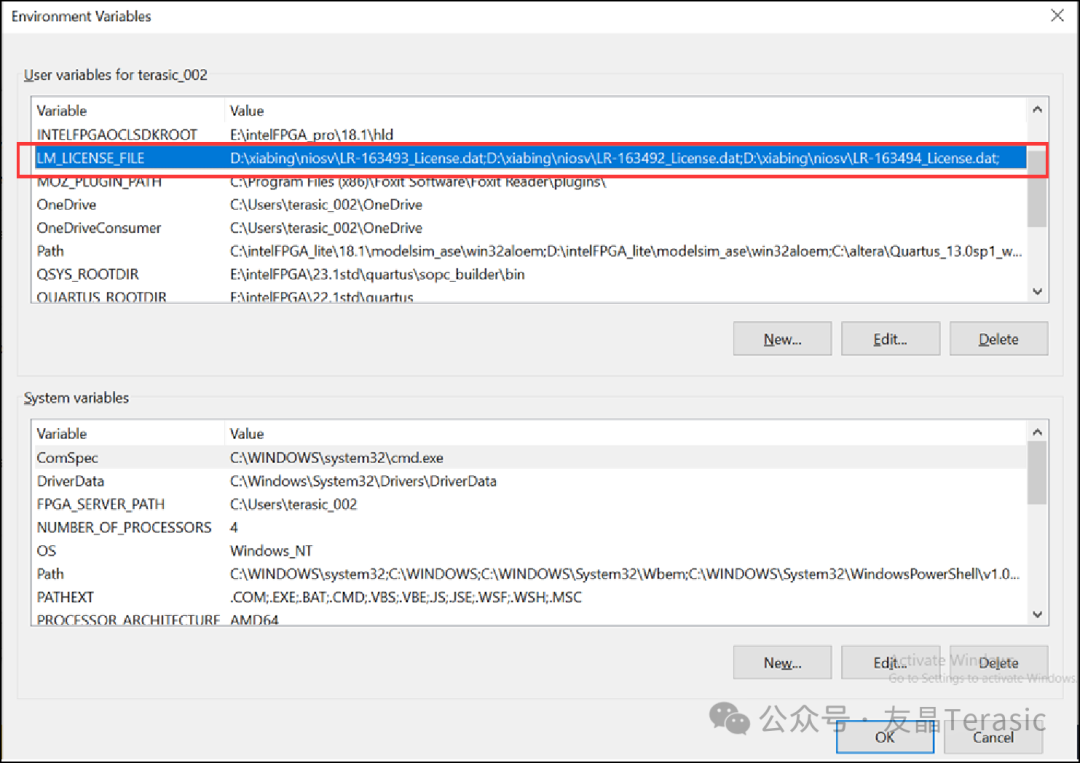

3. 设置license环境变量。将Intel发送过来的license文件保存到本地盘,然后将其具体路径添加到计算机的环境变量窗口。

同时,也在Quartus工具中点击菜单Tools——License setup设置license文件路径:

四、Quartus工程设计

系统组成

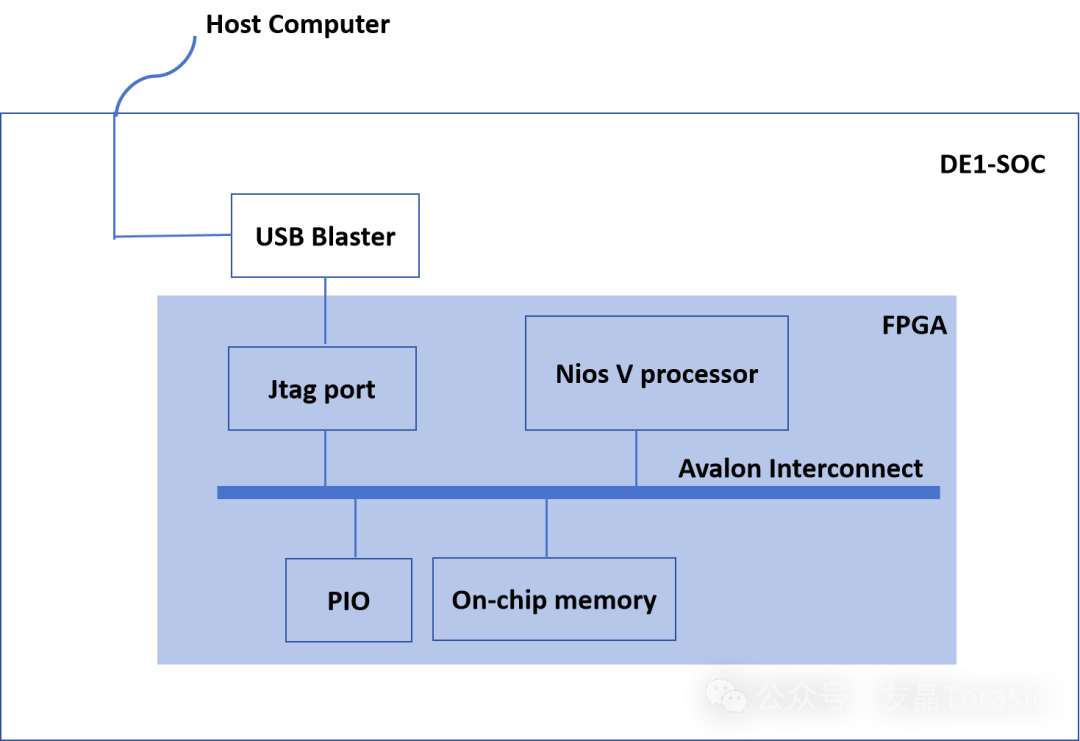

本教程要在FPGA里定制一个包含Nios V处理器、On-Chip Memory、JTAG UART和PIO的嵌入式系统。这个系统中使用的Nios V核是整个系统的核心,其他组件都会通过Avalon总线连接到这个系统核心上。

Clock Source:时钟源组件,提供时钟信号,驱动其他组件。

On-Chip Memory (RAM or ROM) Intel FPGA IP:Intel FPGA包含了可以在Platform Designer系统中当作RAM或ROM使用的片上存储器。片上存储器有以下优势:与片外存储器相比,片上存储器的访问时间更快;Platform Designer自动例化片上存储器,不需要进行任何手动连接;FPGA上电时,某些存储块可具有初始化的内容,这一特性在存储数据常量或处理器引导代码时很重要;片上存储器支持双端口访问,允许两个主设备同时访问同一内存;有RAM和ROM之分,容量大小不超过FPGA最大可用容量。

JTAG UART IP:是PC与FPGA通信电缆的控制台。PC可以将数据通过JTAG电缆传输到FPGA,也能将FPGA产生的数据回传到PC。

PIO(Parallel I/O) Intel FPGA IP :该IP是具有Avalon接口的并行输入/输出(parallel input/output)核,在Avalon存储器映射(Avalon Memory-Mapped Avalon-MM)从端口和通用I/O端口之间提供了一个存储器映射接口。I/O端口既可以连接片上用户逻辑,也可以连接到FPGA与外设连接的I/O引脚。每个PIO核可以提供最多32个I/O端口。像微处理器这样的智能主机通过读/写寄存器映射的Avalon-MM接口控制PIO端口。在主机控制下,PIO核捕获输入端口的数据,并驱动数据到输出端口。当PIO端口直接与I/O引脚相连时,主机通过写PIO核中的控制寄存器对I/O引脚进行三态控制。

或者直接参考Nios V 的handbook手册截图。(截图来自Nios® V 嵌入式处理器设计手册,点击可以跳转)

详细步骤

1. 点击Quartus菜单File——New Project Wizard——Next。

2. 在桌面创建一个my_first_niosv的文件夹,并将工程路径指向这里,且工程的名称也命名为my_first_niosv:

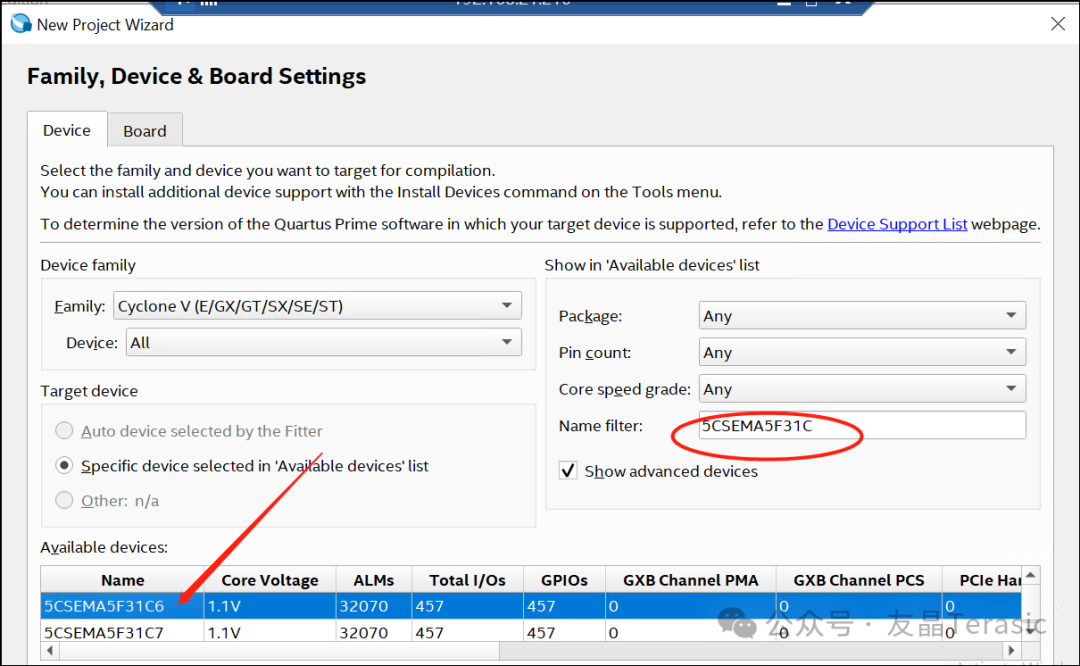

3. 连续点击3次Next得到如下界面,通过器件过滤器筛选选中DE1-SoC的Cyclone V 5CSEMA5F31C6器件。

4. 最后点击Next和Finish完成工程创建。

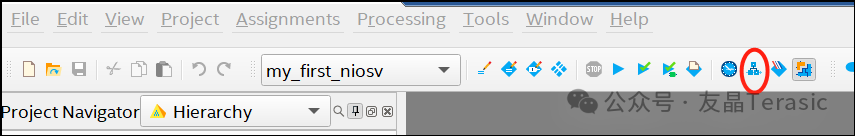

5.点击Platform Designer 图标打开qsys系统界面。

6. 在IP Catalog搜索NiosV,双击Nios V/m Processor Intel FPGA IP以添加此IP到qsys系统,暂时保持默认参数设置不变,直接点击Finish。

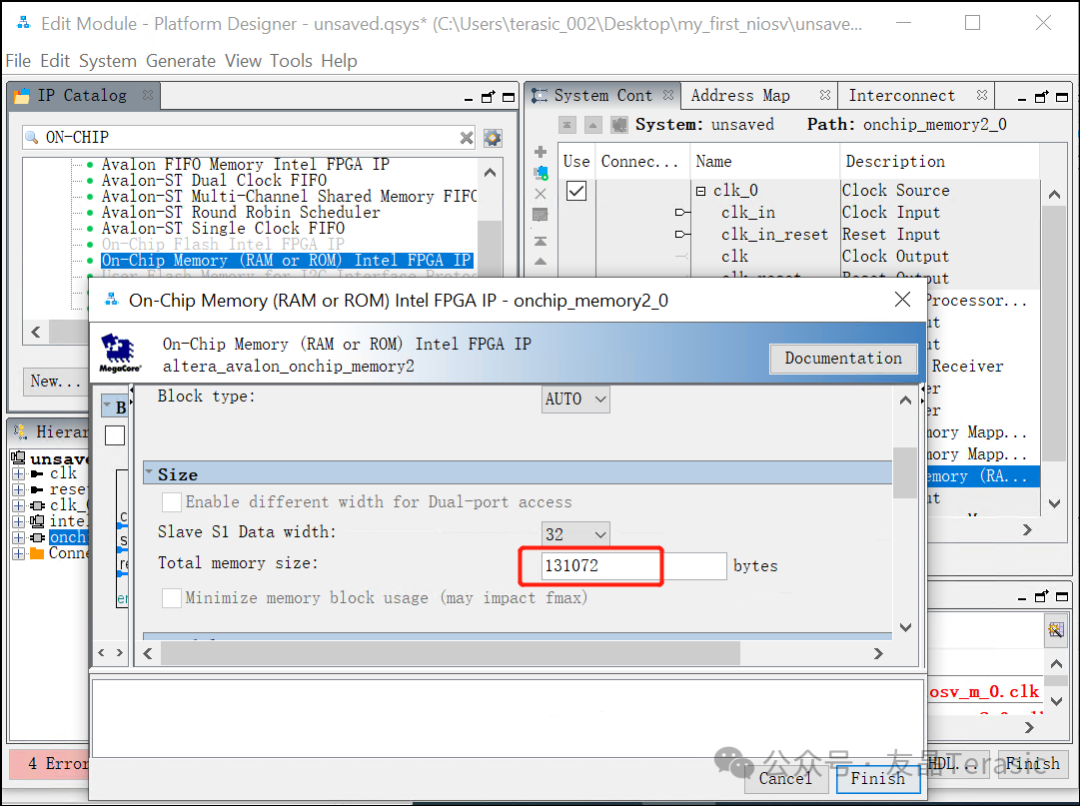

7. 用同样的方法搜索并添加On-Chip Memory (RAM or ROM) Intel FPGA IP,Total Memory Size修改为131072(对应128K),其余参数不变。

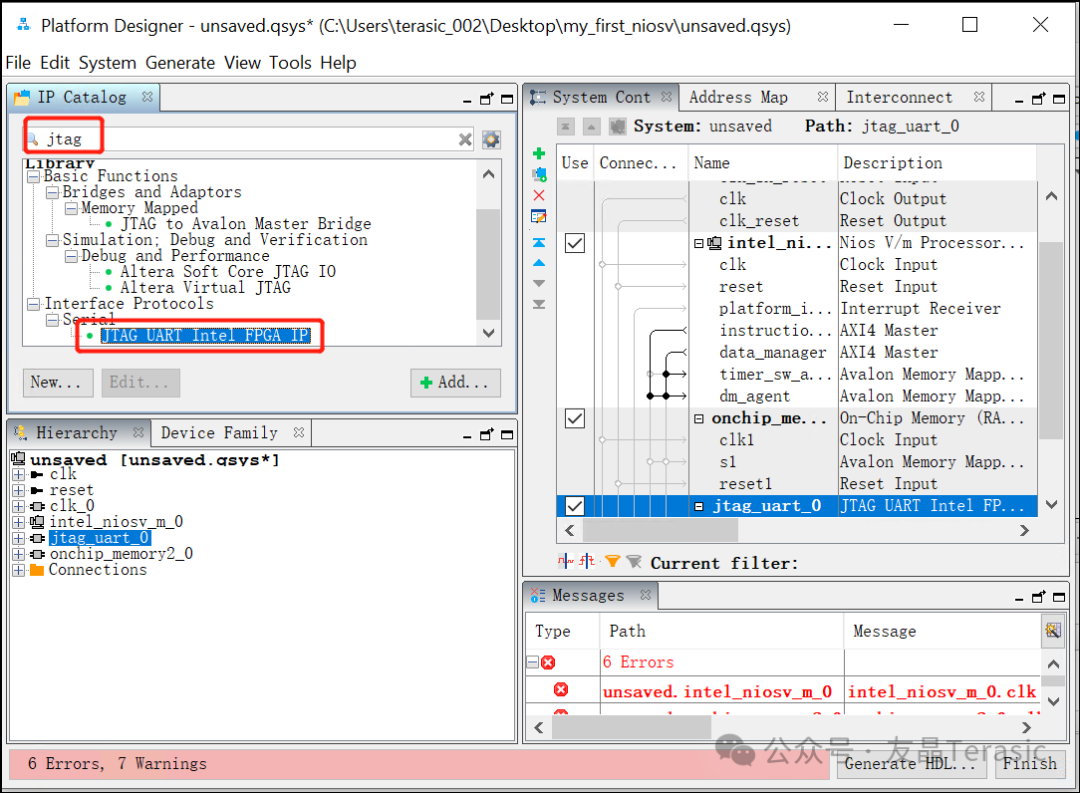

8. 继续搜索并添加JTAG UART Intel FPGA IP到系统,默认参数设置不变。

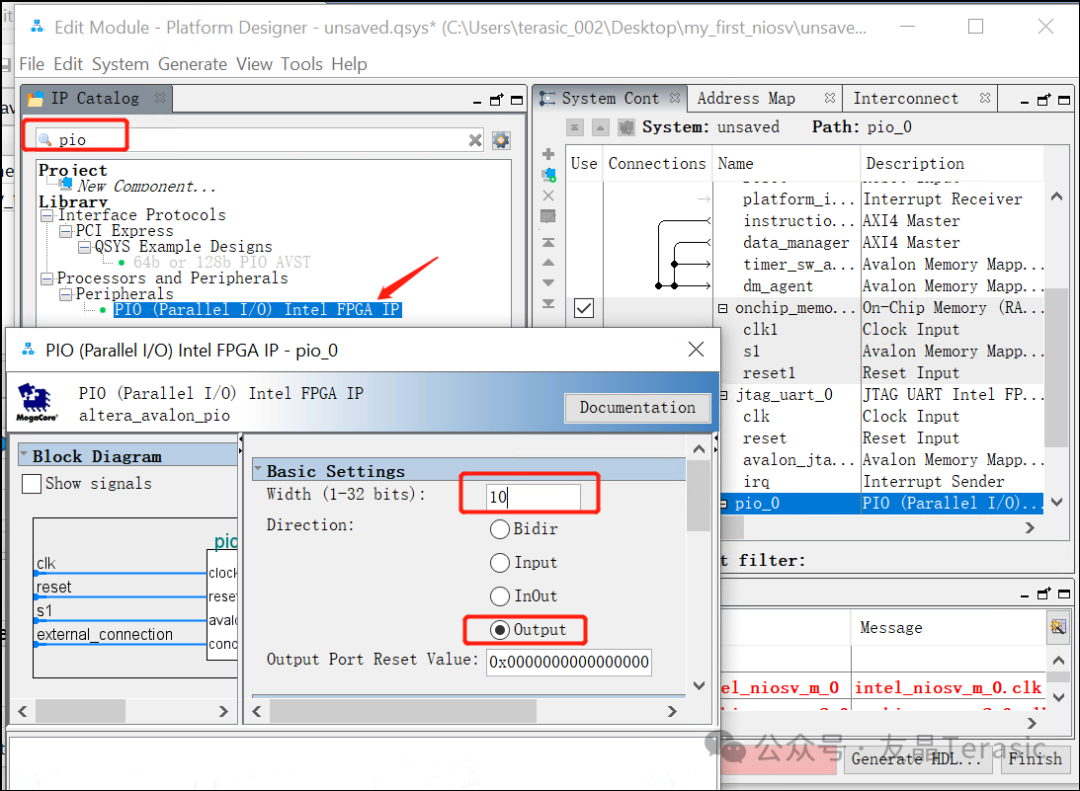

9. 最后搜索添加PIO (Parallel I/O) Intel FPGA IP,Width设置为10,Direction设置为Output。

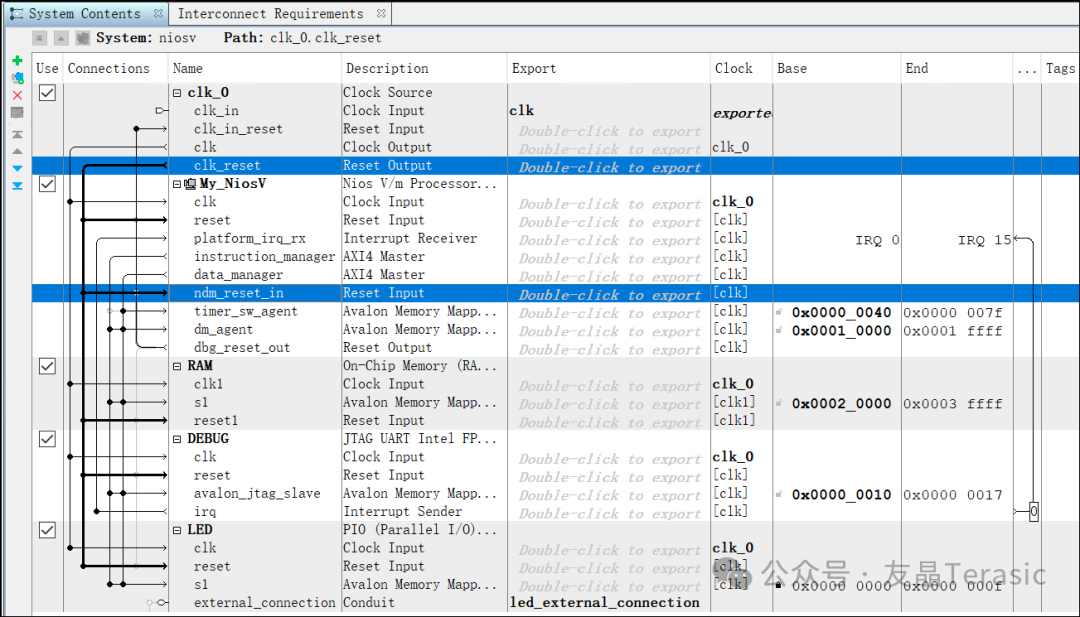

10. 按下图所示连接各IP,并按照下图重命名每个IP,最后双击箭头处将LED PIO导出。

11. 修改Nios V/m IP的参数设置,勾选Enable Reset from Debug Module,Reset Agent选择SRAM.s1。

12.点击Platform Designer的菜单System—— Assign Base Addresses给每个模块分配地址空间。

13. 这时Message栏仍然有错误提示,请将My_NiosV的ndm_reset_in信号与系统rest信号连接起来。最后点击窗口右下角的Generate HDL按钮生成qsys文件。

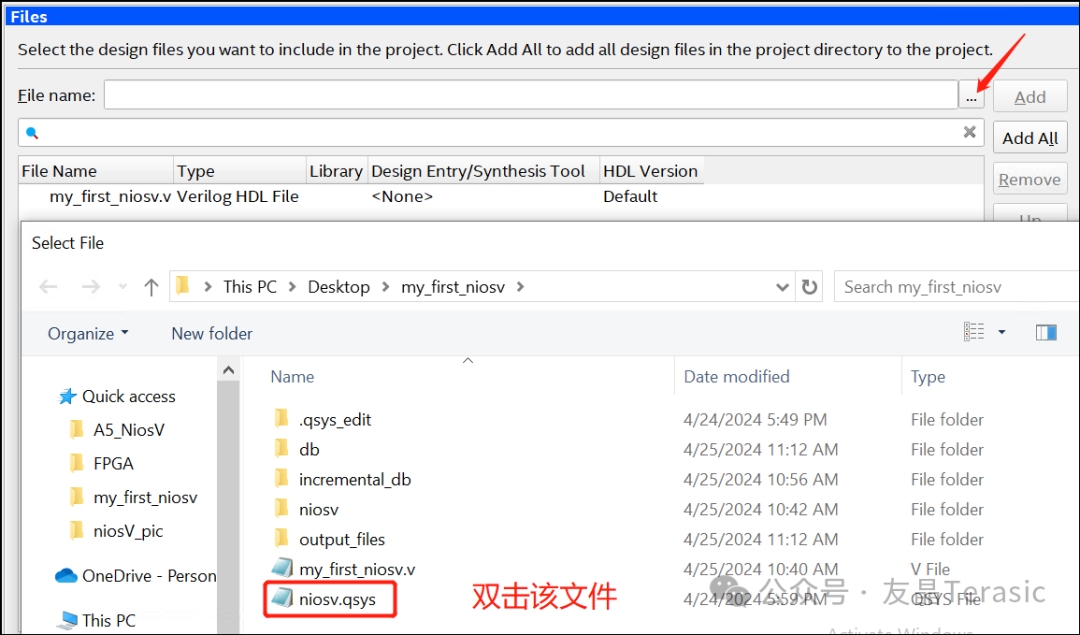

14. 点击OK。(虽然这里截图是提醒添加.qip和.sip文件到工程,但其实也可以添加my_first_niosv/niosv.qsys文件,结果是一样的。)

15. 点击菜单Project——Add/remove Files in Project...。

16. 在弹出的对话框里面点击...双击niosv.qsys文件就可以将该文件添加进工程里面去。

17. 最后得到结果如下,然后点击Apply按钮后,就可以关闭该窗口了。

18. 点击Quartus菜单File——New——Verilog HDL File——OK,创建my_first_niosv.v顶层文件。

19. 在该.v文件里面输入如下代码并保存为my_first_niosv.v。

module my_first_niosv(CLOCK_50,LEDR);input CLOCK_50;output [9:0] LEDR;niosv u0 (.clk_clk (CLOCK_50), //clk.clk.led_external_connection_export (LEDR) // led_external_connection.export);endmodule

20. 点击Analysis & Synthesis进行分析与综合。

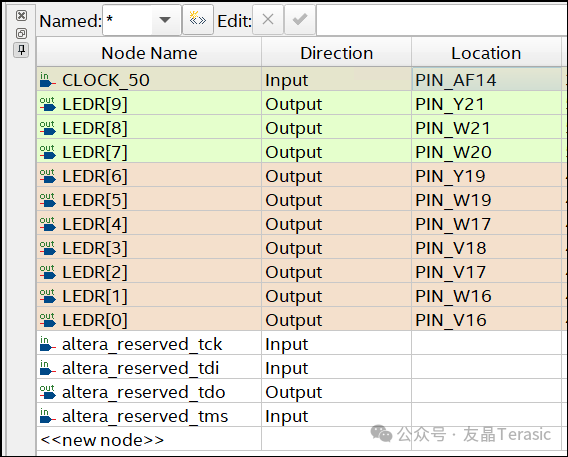

21. 分析综合完成以后,点击Quartus菜单Assignments——Pin Planner。

22. 按DE1-SoC开发板的相关引脚进行引脚分配,具体内容如如下。

23. 最后再点击Start Compilation图标编译Quartus工程,最终生成.sof文件。

五、创建Nios V 软件工程

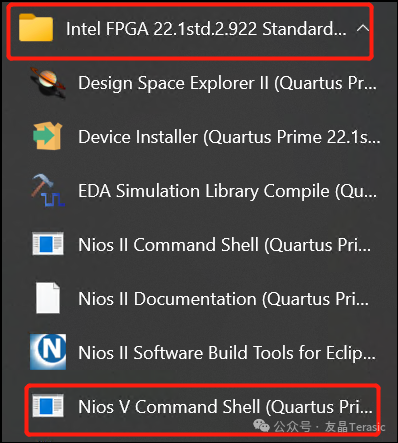

1. 点击电脑左下角的开始菜单打开Nios V Command Shell。

2. 将路径切换到my_first_niosv工程文件夹路径下,然后新建software文件。

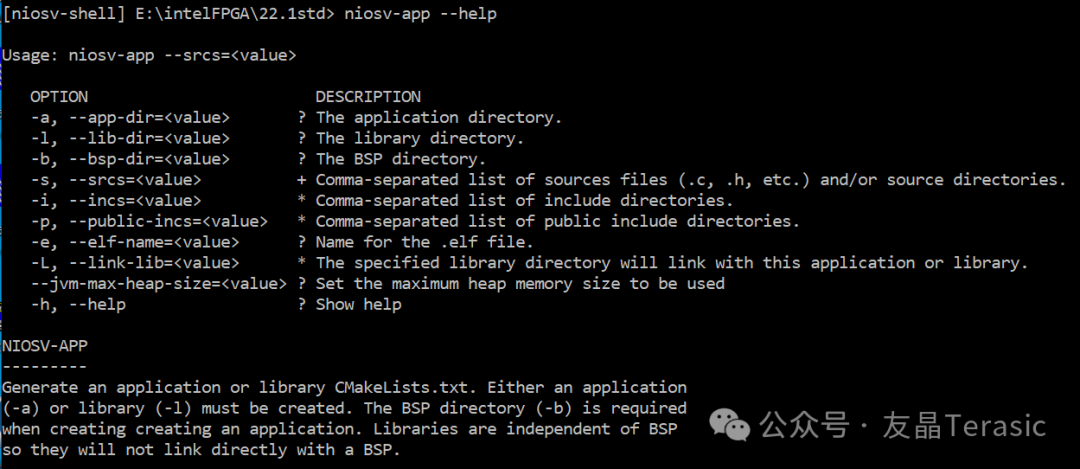

3. 先来看看niosv-app的用法(更多具体内容请自行阅读)。

3. 运行niosv-bsp -c -t=hal --sopcinfo=niosv.sopcinfo software/bsp/settings.bsp命令在software文件夹创建Nios V BSP。

4. 在software文件夹路径下再创建app文件夹,并在app文件夹下创建空白led.c文件。

5. 运行niosv-app -a=software/app -b=software/bsp -s=software/app/led.c命令在app文件夹生成CMakeLists.txt文件。(后面会在RIscFree IDE 中通过“Create a New Project” wizard创建软件工程,然后通过CMakeList.txt 来把APP project 导入进去。)

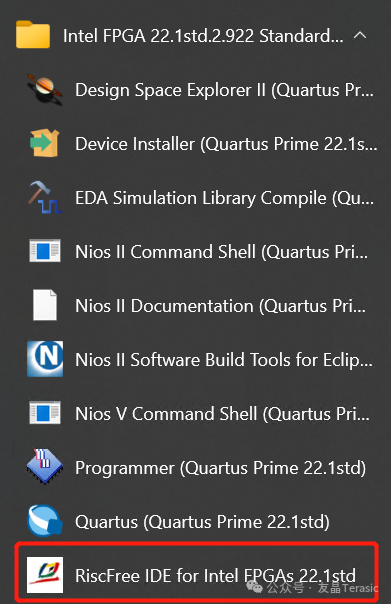

6. 在PC开始菜单栏打开Quartus v22.1.2下的RiscFree IDE。

7. workspace指向software文件夹路径。然后点击Launch启动IDE软件。

8. 点击Create a project,在New Project窗口,选择C/C++下的C Project,点击Next以打开C Project窗口。

9. 在C Project窗口,Project name命名为app,Location指向app所在文件夹,Project Type选择CMake driven下的Empty Project。

10. 接下来的Select Configurations窗口保持默认设置不变,点击Finish即可。

11. 在led.c文件里面敲入如下代码:

#include <stdio.h>#include "system.h"#include "alt_types.h"#include "altera_avalon_pio_regs.h"/* 流水灯控制数组,高电平点亮 */const alt_u32 LED_TBL[] = {0x201, //10 0000 00010x102, //01 0000 00100x84, //00 1000 01000x48, //00 0100 10000x30, //00 0011 00000x48, //00 0100 10000x84, //00 1000 01000x102, //01 0000 00100x201 //10 0000 0001};////// function: main// description: perform cyclically lighting the LED// parameter: none// return: 0////int main(){printf("Realize the function of cyclically lighting the LED\n"); //在console窗口打印信息alt_u8 i;alt_u32 delay;while(1){for(i = 0; i<9; i++){ //流水灯花样数组共有 9种状态IOWR(LED_BASE, 0, LED_TBL[i]); //流水灯花样显示delay = 0;while(delay < 500000) //延时大约1秒delay++;}}return 0;}

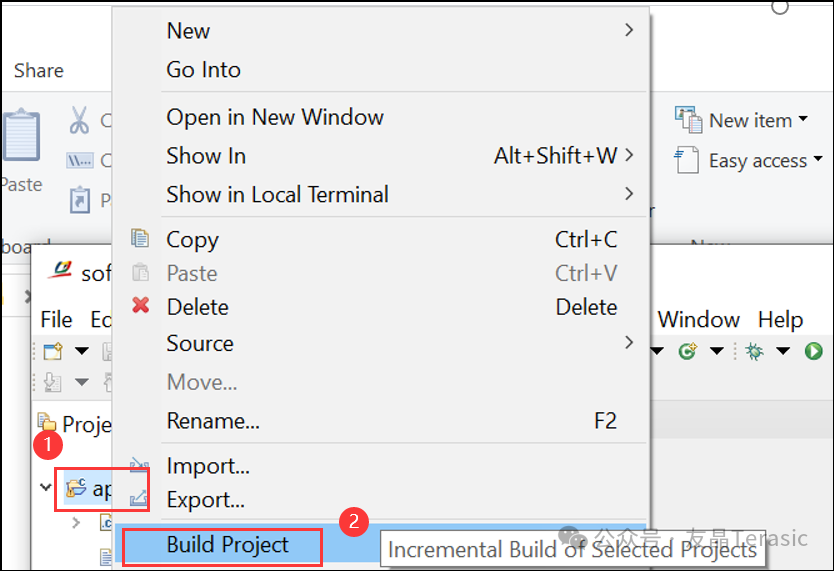

12. 左键选中app,点击Build Project编译led.c,编译完成可以看到生成app.elf文件。

六、下板测试

5.1 配置硬件

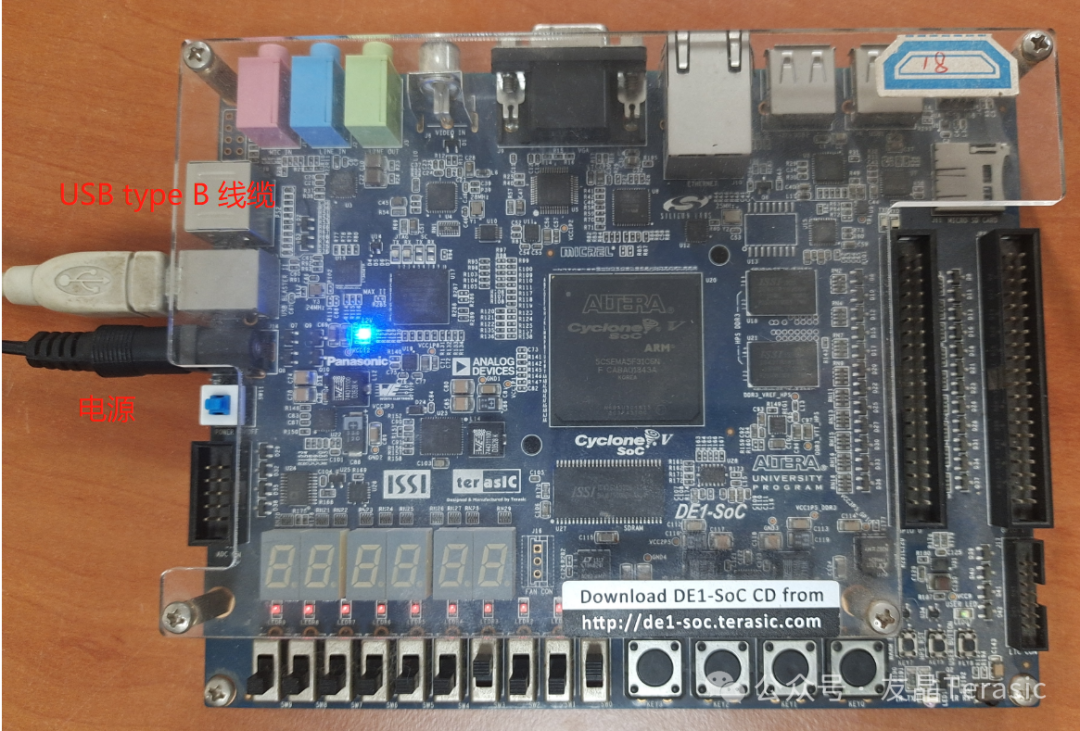

1. 将DE1-SOC开发板和电脑用板子自带的白色USB type B 线缆连接起来。给DE1-SOC插上电源并开机。

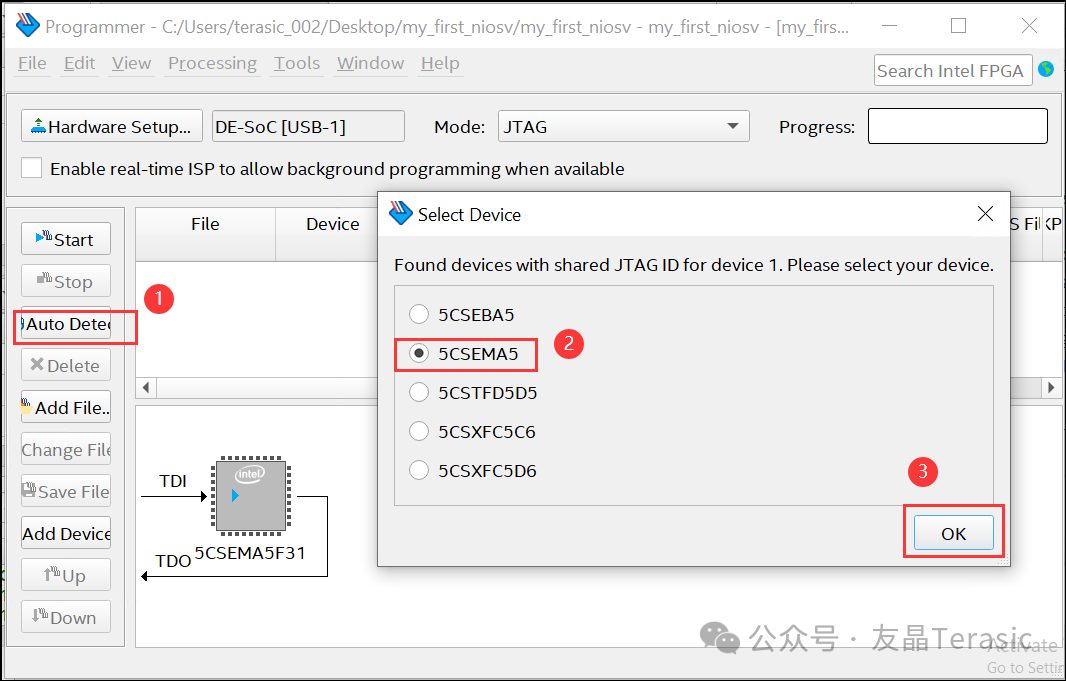

2. 打开Quartus的Programmer工具,点击Hardware Setup,选择DE-SOC[USB-1]端口。

2. 点击Auto Detect,选择DE1-SOC对应的FPGA器件5CSEMA5。

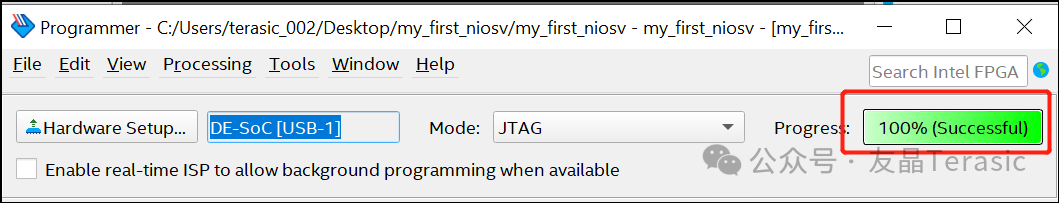

3. 这时会出现两个器件(5CSEMA5和SOCHPS),右击器件5CSEMA5,选择Change File...,然后选择C:\Users\terasic_002\Desktop\my_first_niosv\output_files路径下的my_first_niosv.sof文件,点击Start按钮开始配置FPGA。

进度条显示100%代表FPGA 配置成功。

5.2 配置软件

1. 在Nios V Command Shell里运行juart-terminal。(以前的Nios terimal tool 改为juart-termial了。)

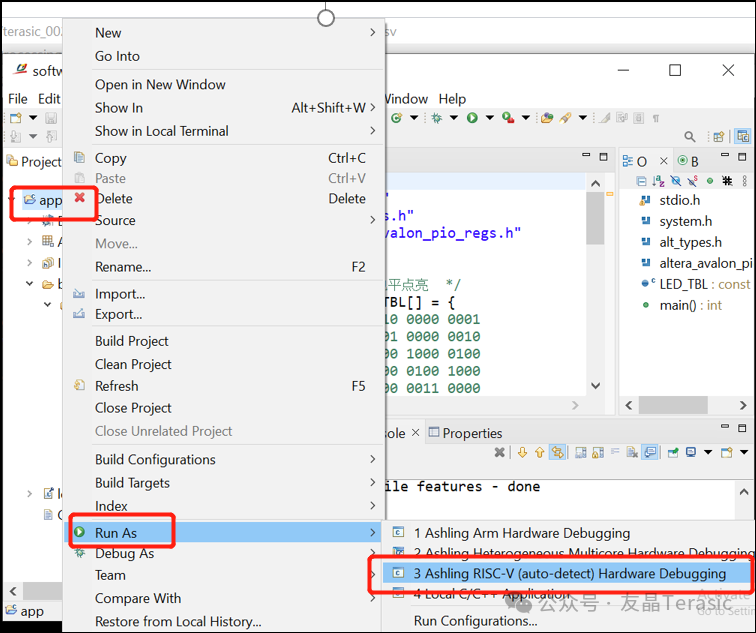

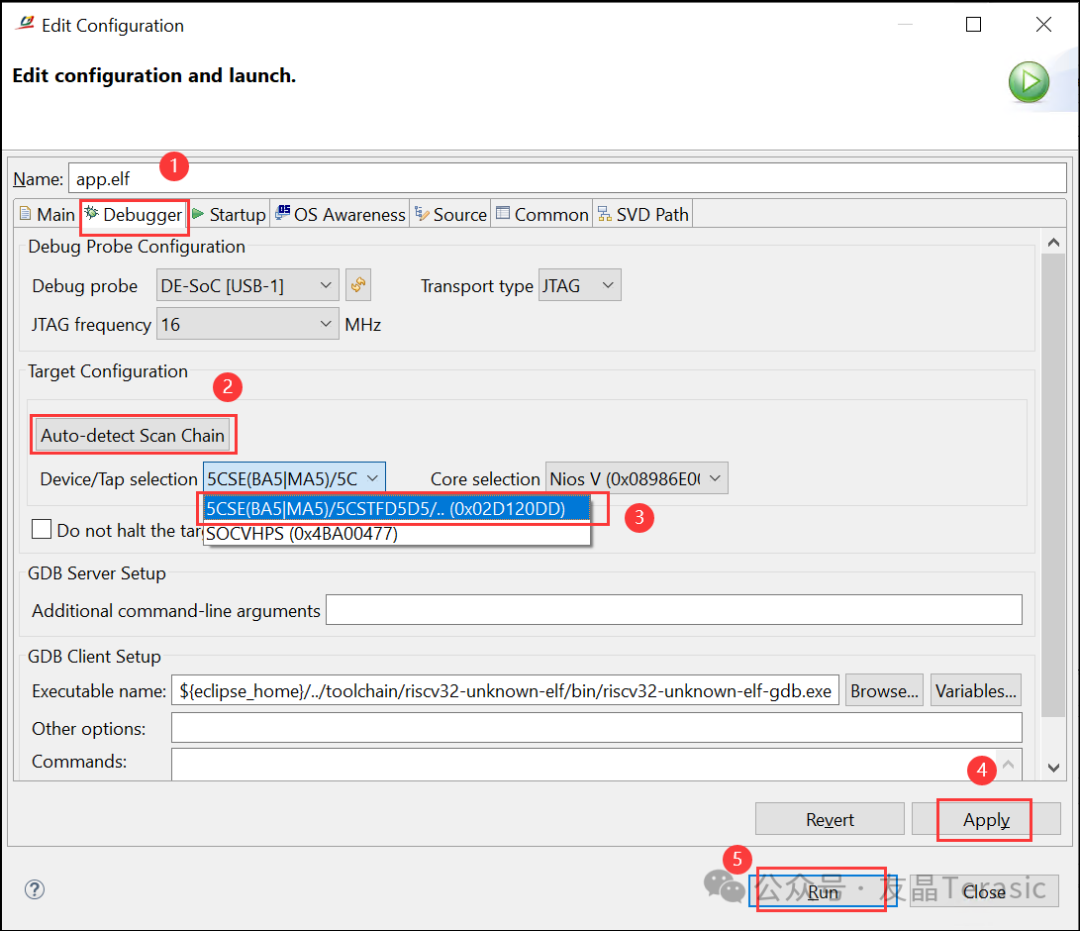

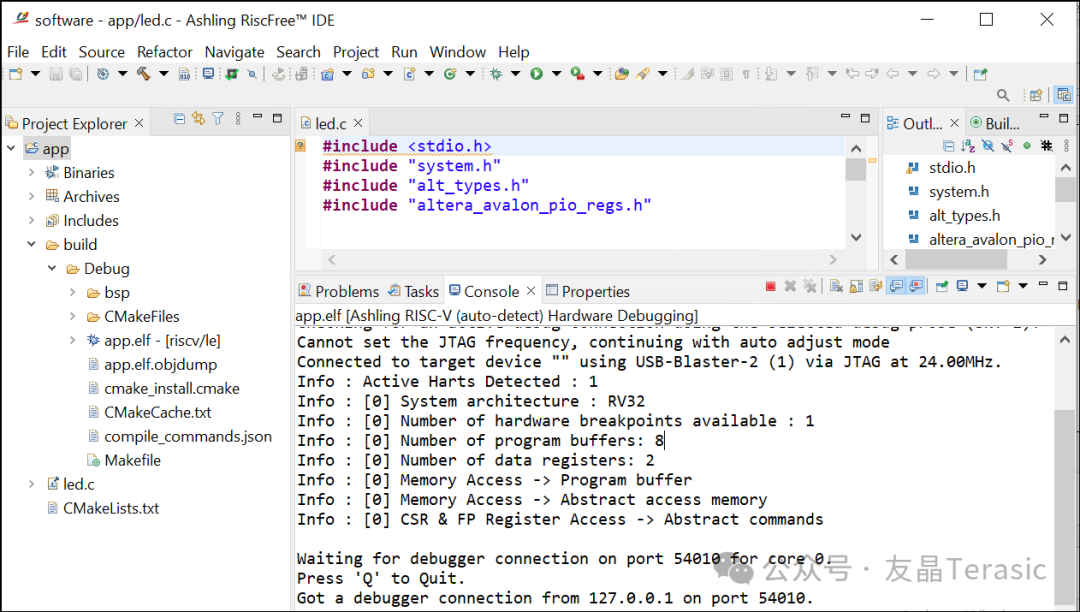

2. 在RiscFree IDE窗口左键选中app,依次选择菜单里的Run As-->3 Ashling RISC-V(auto-detect)Hardware Debugging。

3. 在C Local Application窗口选择app.elf再点OK按钮。

4. 运行完成后即可在DE1-SoC开发板上看到led.c程序的流水灯现象。

5. 同时,在Teminal会打印:Realize the function of cyclically lighting the LED