一、数据导入

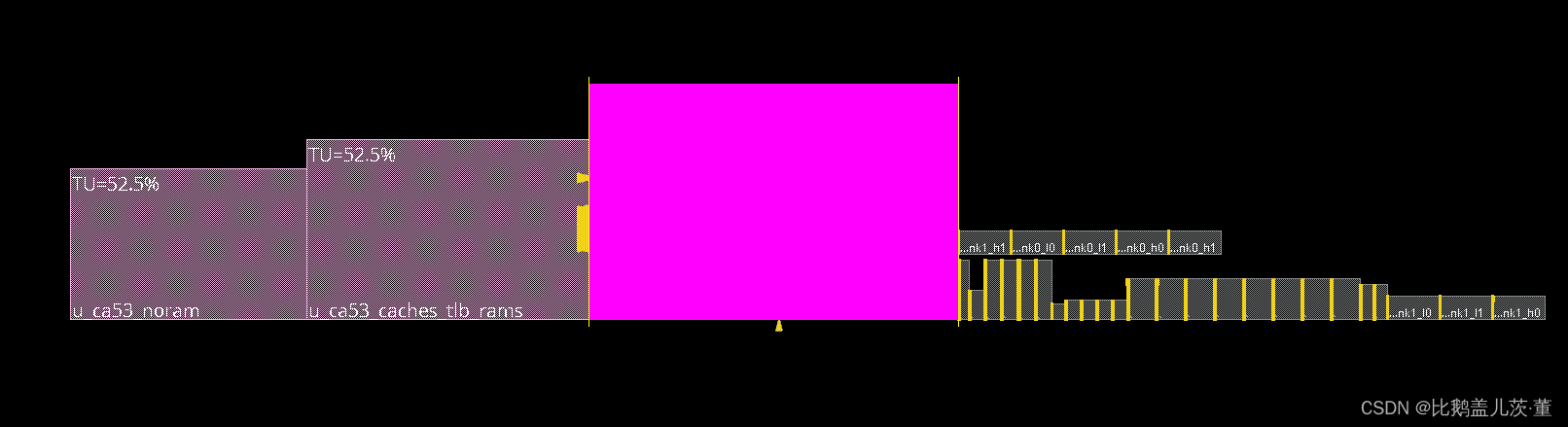

网表、lib等文件库根据flow指令读入,然后read_def 将顶层规划里切分好的ca53_cpu的def读入,即可开始第一版的floorplan。

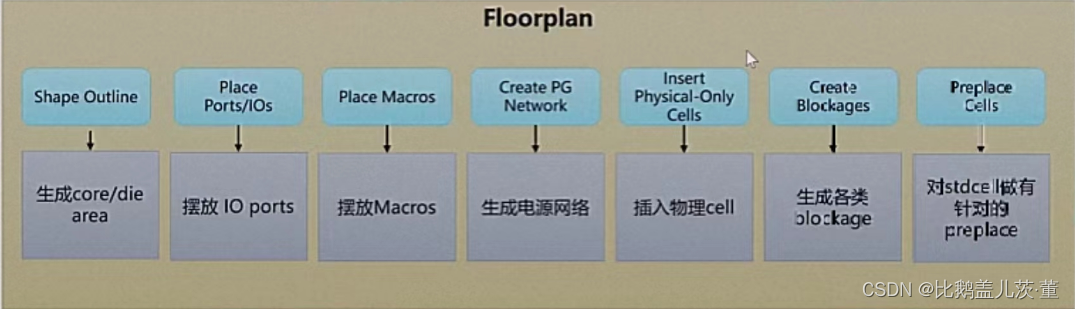

二、floorplan

1.floorplan的具体要求:

1)基本流程:

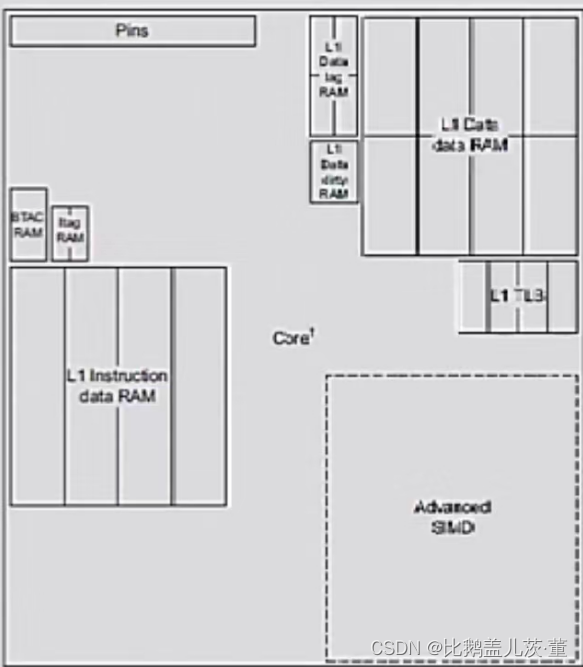

2)macro的相对位置参考

ca53_cpu参考建议如下:

std ce11区域的形状尽量接近方形;Ll icache L1 dcache应分开摆放;The Ll Data Tag应靠近L1 Data data;The L1 Data dirty应靠近L1 data;The TLBSRAM位置相对自由;Port应放在某一个边;SRAM channel应打上soft blockage

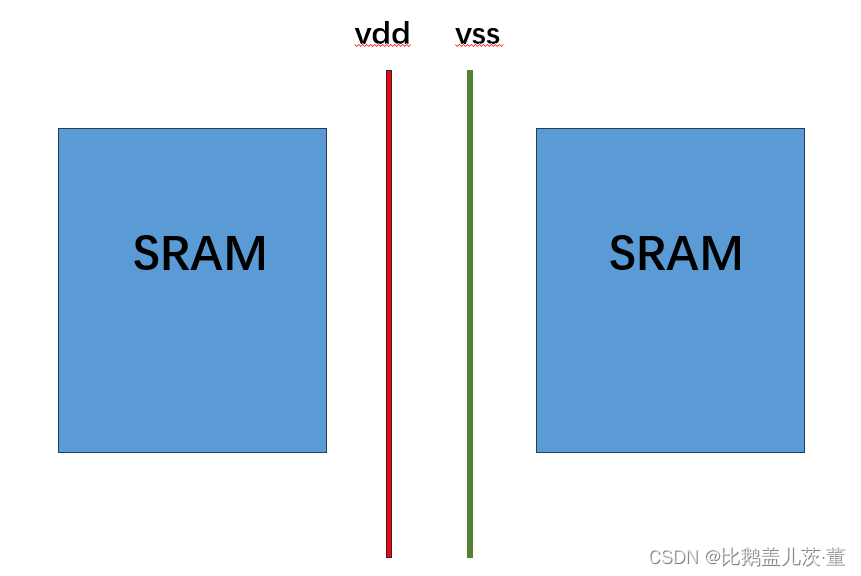

3)channel的间距

左右:除了考虑pin绕线所占据的空间外,还要考虑vdd和vss可以在channel打一组,以确保后期channel里的st cell能正常供电。

上下:比较保险的距离是2.4um以上;一般需要预留一些走线和放cell的空间;加上keepout margin/halo,推荐7um以上(经验值)。

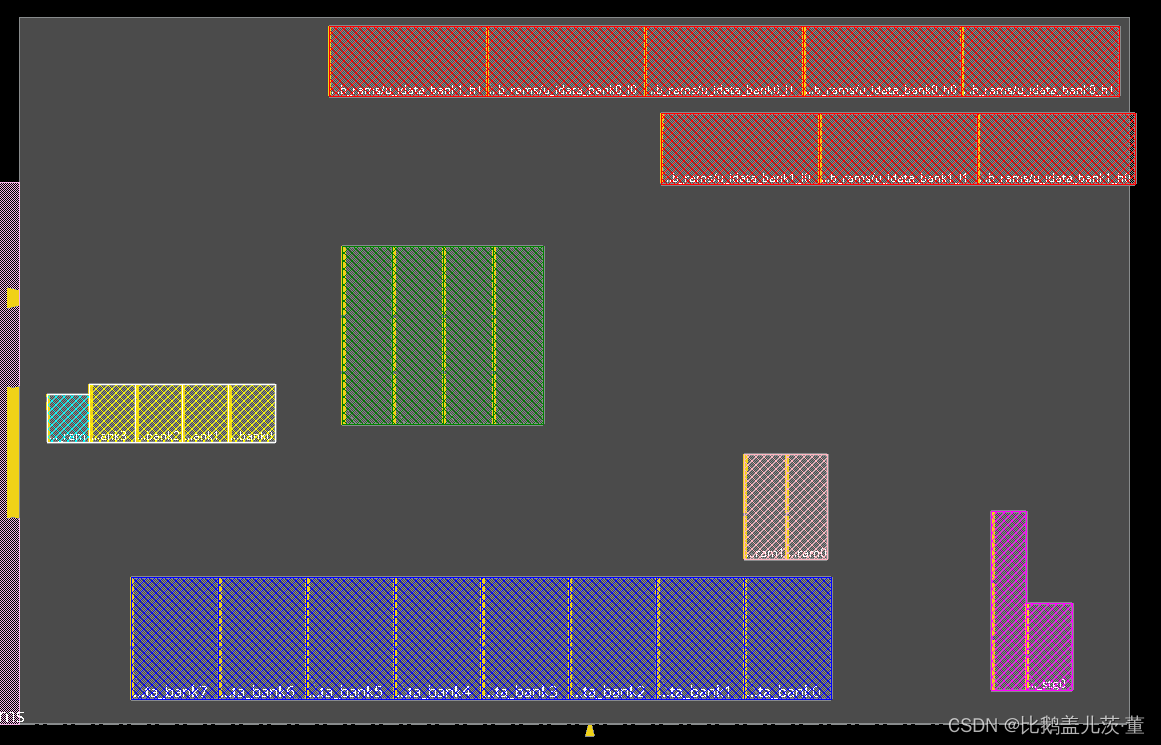

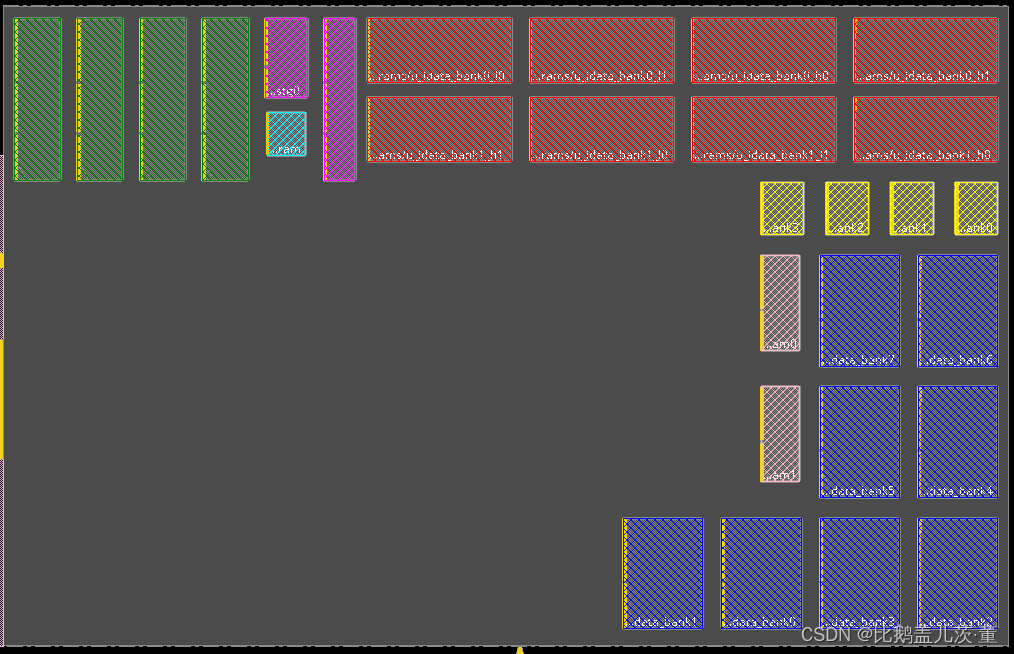

2.具体摆放方法

macro分类后,用toolbox调整位置。

第一版 floorplan

3.写出macro位置

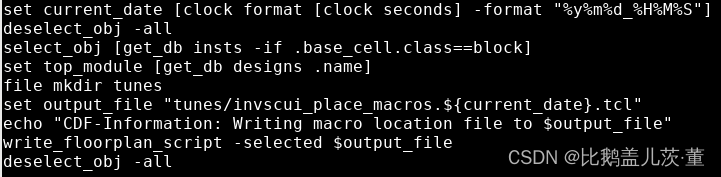

脚本:

写出至tunes目录下

注:在这里我存了一个database

![]()