dc拉高的时候就是发送128字节数据的时候 发送指令dc拉低

模式是00

sck先置低再置高

复位是与开发板上的按键一样都是低有效

25位字节指令 加 3字节的 页地址加起始结束 b0,00,10,

`timescale 1ns / 1ps

module top0(input wire clk ,input wire rst_n,// output wire cs ,output wire rst ,output wire sck ,output wire dc ,output wire mosi );

wire [7:0] data ;

wire valid;

wire busy ;

wire ena ;

wire [7:0] douta;wire [7:0] dout ;

wire vlid ;

// wire cs ;

wire [9:0] addra;reg [9:0] cunt ;

reg [9:0] cunt_b;

reg [6:0] cunt_r;

reg [7:0] cunt_t;assign rst=rst_n;

assign valid=(busy==0&&cunt==10)?1'b1:1'b0;

assign ena =1'b1;

// assign cs =1'b1;

assign dc =(cunt_b<28)?1'b0:1'b1;assign addra=cunt_b+1;

assign data=(cunt_b==25)?cunt_t:douta;

always @(posedge clk ) beginif(busy==0)cunt<=cunt+1;elsecunt<=0;

end

always @(posedge clk or negedge rst_n) beginif(!rst_n)cunt_b<=1'b0;else beginif(cunt_b==157) ///***必须多记一位cunt_b<=25;else if(cunt==1)cunt_b<=cunt_b+1;elsecunt_b<=cunt_b;end

end

//页地址更换

always @(posedge clk ) beginif(!rst_n)cunt_r<=0;else if(cunt_r==3&&cunt_b==157)///***cunt_r<=0;else if(cunt_b==157)///***cunt_r<=cunt_r+1;elsecunt_r<=cunt_r;

end

//

always @(posedge clk ) beginif(!rst_n)cunt_t<=8'hb0;else case (cunt_r)0:cunt_t<=8'hb0;1:cunt_t<=8'hb1;2:cunt_t<=8'hb2;3:cunt_t<=8'hb3;default: ;endcase

endspi_rom#(. SIZE (8)

)u_sp(/*input wire */. clk (clk ),/*input wire */. rst_n(rst_n),/*input wire [SIZE-1:0]*/. data (data ),/*input wire */. valid(valid),/*output reg */. sck (sck ),. busy (busy ),/*output reg */. mosi (mosi ));

blk_mem_gen_0 your_instance_name (.clka(clk), // input wire clka.addra(addra), // input wire [9 : 0] addra.douta(douta) // output wire [7 : 0] douta

);

spi_rx#(. SIZE (8)

)u_rx(/* input */ .clk (clk ) ,/* input */ .rst_n(rst_n) ,/* input */ .miso (mosi ) ,/* input */ .sck (sck ) ,/* input */ .cs (cs ) ,/* output reg [SIZE-1:0]*/ .data (dout ) ,/* output */ .vlid (vlid ) );

endmodule`timescale 1ns / 1psmodule spi_rom#(parameter SIZE = 8

)(input wire clk ,input wire rst_n,input wire [SIZE-1:0] data ,input wire valid,output reg sck ,output wire busy ,output reg mosi );

parameter CUNT_MAX = 100 ;

parameter BUSY = 2'b10 ;

parameter IDEL = 2'b01 ;reg fin ;

reg [1:0] state ;

reg [10:0] cunt ;

reg [10:0] cunt_b ;

reg [SIZE-1:0] data_r ;

assign busy=(state==BUSY)?1'b1:1'b0;

//状态

always @(posedge clk or negedge rst_n) beginif(!rst_n)state<=IDEL;else case (state)IDEL:beginif(valid==1)state<=BUSY;elsestate<=state;endBUSY:beginif(fin==1)state<=IDEL;elsestate<=state;enddefault: ;endcase

end

//计数器

always @(posedge clk) beginif(state==IDEL)cunt<=11'd0;else beginif(cunt==CUNT_MAX-1)cunt<=11'd0;elsecunt<=cunt+1'b1;end

end

//cunt_b

always @(posedge clk ) beginif(state==IDEL)cunt_b<=11'd0;else beginif(cunt==CUNT_MAX-1)cunt_b<=cunt_b+1;elsecunt_b<=cunt_b;end

end

//fin结束信号

always @(posedge clk ) beginif((cunt_b==SIZE-1)&&(cunt==CUNT_MAX-1))fin<=1'b1;elsefin<=1'b0;

end

//数据的缓存

always @(posedge clk ) beginif(state==IDEL&&valid==1)data_r<=data;else if(state==BUSY&&cunt==CUNT_MAX-2)data_r<=(data_r<<1);elsedata_r<=data_r;

end

//sck的产生

always @(posedge clk ) beginif(state==IDEL)sck<=1'b0;else beginif(cunt_b==SIZE) //防止sck出现末尾的毛刺sck<=1'b0;else if(cunt<50)sck<=1'b0;elsesck<=1'b1;end

end

//tx的输出

always @(posedge clk ) beginif(state==IDEL)mosi<=1'b0;else beginif(cunt==0)mosi<=data_r[SIZE-1];elsemosi<=mosi;end

end

endmodulerx方便仿真

`timescale 1ns / 1psmodule spi_rx#(parameter SIZE = 8

)(input clk ,input rst_n ,input miso ,input sck ,input cs ,output reg [SIZE-1:0] data ,output vlid );

reg [8:0] cunt_b;

reg [1:0] rx_t ;assign vlid=(cunt_b==SIZE)?1'b1:1'b0;always @(posedge clk ) beginif(!rst_n)rx_t<=2'b00;else rx_t<={rx_t[0],sck};

end

//对下降沿计数

always @(posedge clk ) beginif(!rst_n)cunt_b<=0;else if(cs==0)begin if(vlid==1)cunt_b<=0;else if(rx_t==2'b10)cunt_b<=cunt_b+1'b1;elsecunt_b<=cunt_b;endelsecunt_b<=0;

end

//data

always @(posedge clk ) beginif(cs==0&&rx_t==2'b10)data[0]<=miso;else if(cs==0&&rx_t==2'b01)data<=(data<<1);elsedata<=data;

endendmodulecoe文件

一共4个页地址8’hb0 - 8’hhb3

memory_initialization_radix=16; // 指定数据的基数,10 表示十进制

memory_initialization_vector=00,ae,20,10,00,b0,81,ff,a1,a6,a8,1f,c8,d3,00,d5,80,d9,1f,da,02,db,20,8d,14,af,

b0,00,10,00,00,00,00,00,00,00,00,00,00,46,49,49,49,31,00,00,00,00,00,7F,04,08,10,7F,00,00,00,00,00,63,14,08,14,63,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00, 00, 00;

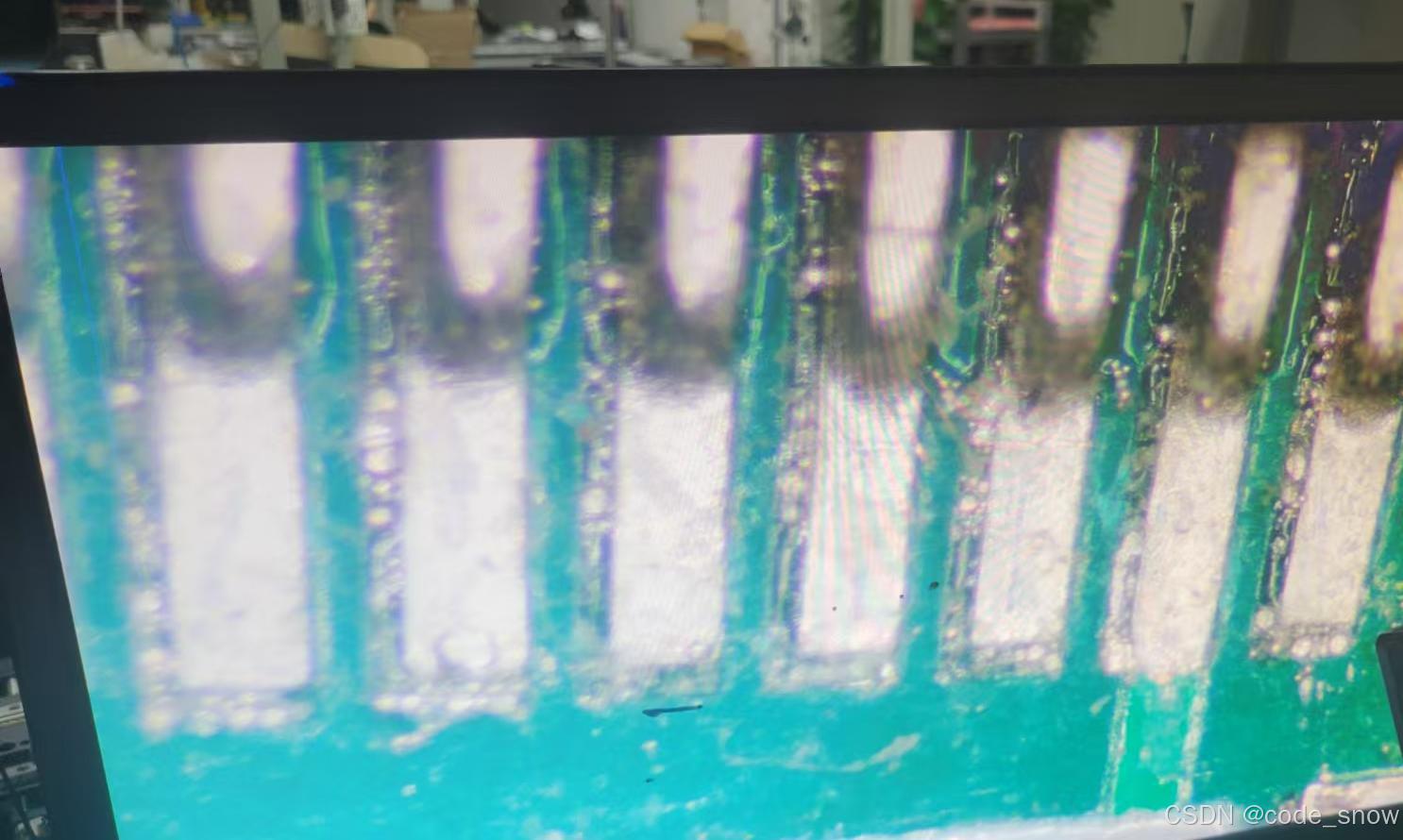

上板效果