一、关键路径

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。也就是静态时序报告中WNS(Worst Nagative Slack)对应的路径。

优化关键路径的方法:

1、在组合逻辑内插入寄存器,进行流水线处理

2、重定时,使寄存器之间的延迟趋近于平衡

3、操作符平衡。加法树、成法树。

4、消除优先级

5、逻辑复制,降低扇出。

6、关键信号后移。

关键输入应该在逻辑最后一级提供,其中关键输入为芯片、Slice、或者LUT提供的时延最大的输入,比如在if…else if…链中,将关键信号放在最低一级。

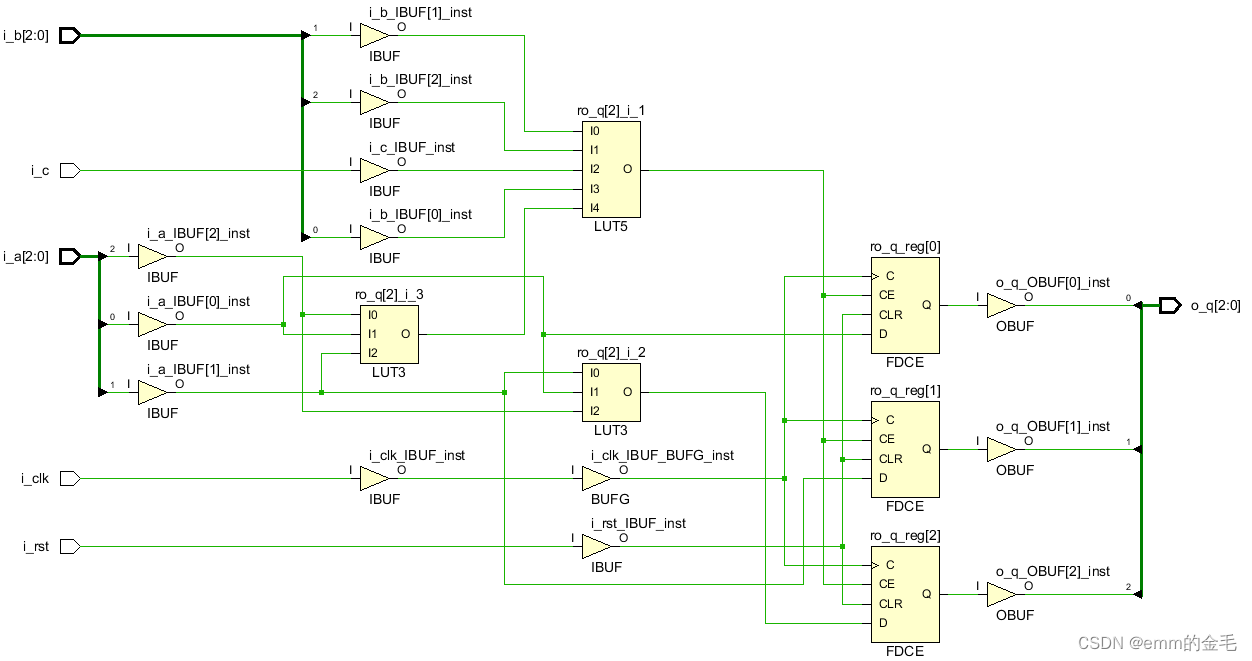

module if_test(input i_clk ,input i_rst ,input [2:0] i_a ,input [2:0] i_b ,input i_c ,output [2:0] o_q

);reg [2:0] ro_q ;assign o_q = ro_q ;always@(posedge i_clk,posedge i_rst)beginif(i_rst)ro_q <= 'd0;else if(i_a == 2)ro_q <= i_a;else if(i_b == 4 && i_c )ro_q <= i_b + i_a;elsero_q <= o_q;

上图中,ro_q[2]_i_3的LUT作为变量去控制ro_q[2]_i_1,证明了i_a == 2的优先级比i_b == 4 && i_c大,并且i_a == 2经历的路径更长。

二、静态时序分析的作用

参考:什么是STA静态时序分析,有什么作用?【FPGA/数字IC笔试面试】

静态时序分析的作用:

STA静态时序分析(Static Timing Analyse),属于验证的范畴,是从时序上对综合后的网表进行验证,检查电路是否存在建立时间、保持时间等违例。

STA与形式验证不同,STA从时序上验证,形式验证从功能上验证。

STA的工具有Synosys的Prime Time。

(1)静态时序分析是一种验证数字集成电路时序是否合格的验证方法;

(2) 静态时序分析的前提是同步逻辑设计(重要!),不能分析异步电路;

(3) 静态时序分析工具计算路径延迟的总和,并比较相对于预定义时钟的延迟;

(4) 静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能;

(5) 静态时序分析对所有的时序路径进行错误分析,不需要使用测试向量激活某个路径(与时序仿真的不同点),分析速度比时序仿真工具快几个数量级,克服了动态时序验证的缺陷,适合大规模的电路设计验证,在同步逻辑情况下,能够达到100%的时序路径覆盖;

(6) 静态时序分析的目的是找到隐藏的时序问题,根据时序分析结果优化逻辑或者约束条件,使设计达到时序闭合(Timing Closure);

(7) 静态时序分析能够识别的时序故障:建立时间(Setup)/保持时间(Hold)/恢复时间(Recovery)/移除时间(Removal)检查;最小跳变和最大跳变;时钟脉冲宽度、时钟畸变(Skew、Jitter);总线竞争;不受约束的逻辑通道;关键路径;约束冲突等;

常用时序分析的概念:

setup time:时钟有效沿到来之前,数据必须保持稳定的最短时间,对应的是数据路径的最大延时;

与寄存器的时钟有关。

hold time:保持时间:时钟有效沿到来之后,数据必须保持稳定的最短时间,对应的是数据路径的最小延时

与寄存器的时钟无关。

建立时间或者保持时间不满足导致数据采样出错,亚稳态 现象。

recovery time:时钟有效沿来临之前,异步复位已经撤销的最小时间(复位已经无效的最小时间,对应于数据的恢复);

即在时钟有效沿来临之前,复位就要撤销,数据就要开始恢复的正常状态的时间。

与寄存器的复位有关。

removal time:时钟有效沿来临之后,异步复位需要保持有效的最小时间,类似时钟的 hold。

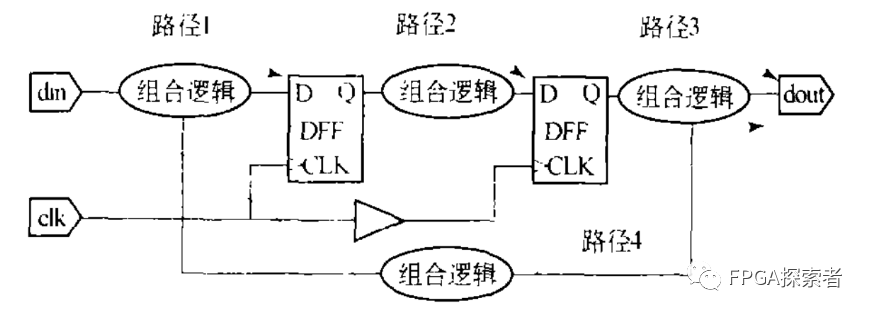

STA 的时序路径

STA 四种时序路径:

路径1:输入端口到寄存器的数据输入 D,

路径2:内部寄存器的时钟输入端到下一个寄存器的数据输入 D,

路径3:内部寄存器的时钟输入端到输出端口;

路径4:输入端口到输出端口。

每条时序路径包含 1 个起点和 1 个终点,

起点只能是设计的基本输入端口或内部寄存器的时钟输入端,

终点只能是内部寄存器的数据输入端或设计的基本输出端口。

对于路径 3,分析根据寄存器的 Tco 延迟和组合路径延迟等分析 setup 和 hold 是否满足。

对于路径 1 和 3,可以加入 input delay 和 output delay 来分析,来满足寄存器的建立/保持时间要求。

三、形式验证

参考:什么是STA静态时序分析,有什么作用?【FPGA/数字IC笔试面试】

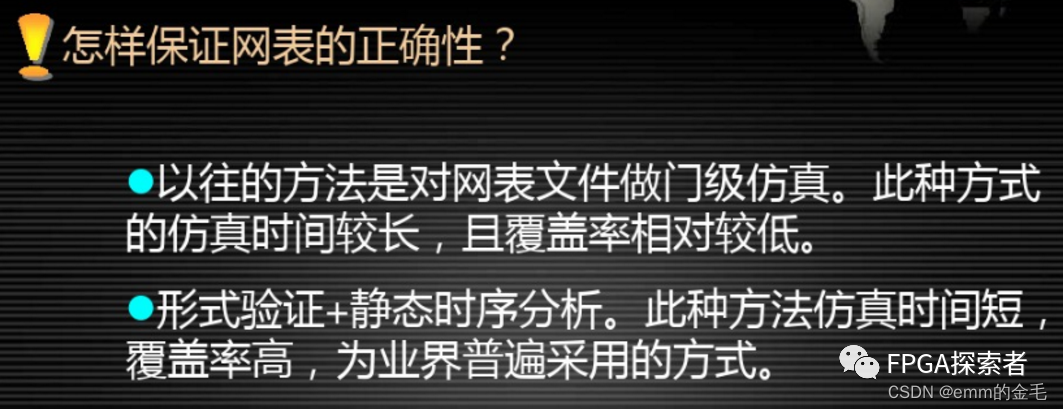

形式验证,属于验证范畴,从功能上对综合后的网表进行验证,常用的是等价性检验,以功能验证后的HDL设计为参考,对比综合后的网表功能,检验是否在功能上存在等价性,保证综合后没有改变原先HDL描述的功能。

形式验证的工具:Synopsys 的Formality

STA :时序路径覆盖率 100%,穷尽所有时序路径,验证时序;

形式验证:验证功能;