文章目录

- 一、有关时钟源

- 二、系统时钟架构

- 三、时钟树分析

- 四、修改参数步骤

- 1、设置外部晶振

- 2、选择外部时钟源。

- 3、 设置系统主频率大小

- 4、修改PLL分频倍频系数

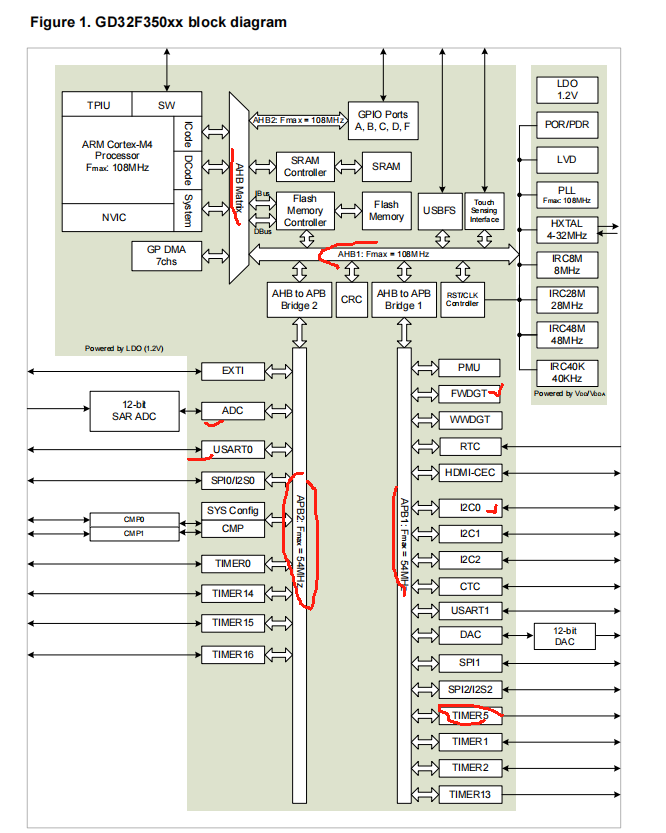

学习系统时钟架构和时钟树,验证及学习笔记如下,如有错误,欢迎指正。主要记录了总线下挂载外设,总线时钟源以及系统时钟的配置。

一、有关时钟源

1、HXTAL:高速外部时钟,4到32MHz的外部振荡器可为系统提供更为精确的主时钟。它是板子焊接的外部晶振,精度高,但功耗比内部时钟较高;

2、LXTAL:低速外部时钟,LXTAL晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。它为实时时钟电路提供一个低功耗且精确的时钟源。

3、IRC8M:高速内部8MHz时钟,内部8MHz RC振荡器时钟,简称IRC8M时钟,拥有8MHz的固定频率,设备上电后CPU默认选择的时钟源就是IRC8M时钟。它是芯片内部自带的时钟,精度较低,可以应用在对时钟要求不高的场景中;

4、IRC28M:高速内部28MHz时钟,内部28MHz RC振荡器时钟 (IRC28M) 有一个固定的频率28MHz,专门用作ADC时钟。

5、IRC48M:高速内部48MHz时钟,内部48M RC振荡器时钟(IRC48M) 有一个固定的频率48MHz,用作USB时钟或者PLL时钟源。

6、IRC32K:低速内部时钟;

7、IRC40K:低速内部时钟,IRC40K RC振荡器时钟担当一个低功耗时钟源的角色,它的时钟频率大约40 kHz,为独立看门狗定时器和实时时钟电路提供时钟。

8、内部锁相环(PLL):对输入参考频率为4到32MHz时钟进行分频操作,输出一个8-120 MHz的时钟输出。严格来说锁相环不算时钟源,它是其他时钟源头配置而来。

剩下就是HXTAL时钟监视器、时钟预分频器、时钟多路复用器和时钟门控电路等。

AHB、 APB和Cortex®-M4时钟都源自系统时钟(CK_SYS),系统时钟的时钟源可以选择IRC8M、HXTAL或PLL。

做项目时需要确认该项目所用晶振为内部晶振还是外部晶振。

二、系统时钟架构

(1)以GD32F350系列为例,Cortex-M4架构,最高时钟频率为108MHz。

通过固件库的system_gd32f10x.c以及系统时钟架构可知:

/* HXTAL is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/2 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV2;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;

AHB总线为系统时钟的1分频,即最高频率为108MHz。

APB1总线为系统时钟的2分频,即最高频率为54MHz。

APB2总线为系统时钟的1分频,即最高频率为54MHz。

(2)通过分析系统架构图可知:

- 系统时钟分频情况。

- 时钟总线(AHB、APB1、APB2)的所挂载的外设。

(以TIMER1为例,挂载的是APB1总线,USART0挂载APB2总线。)

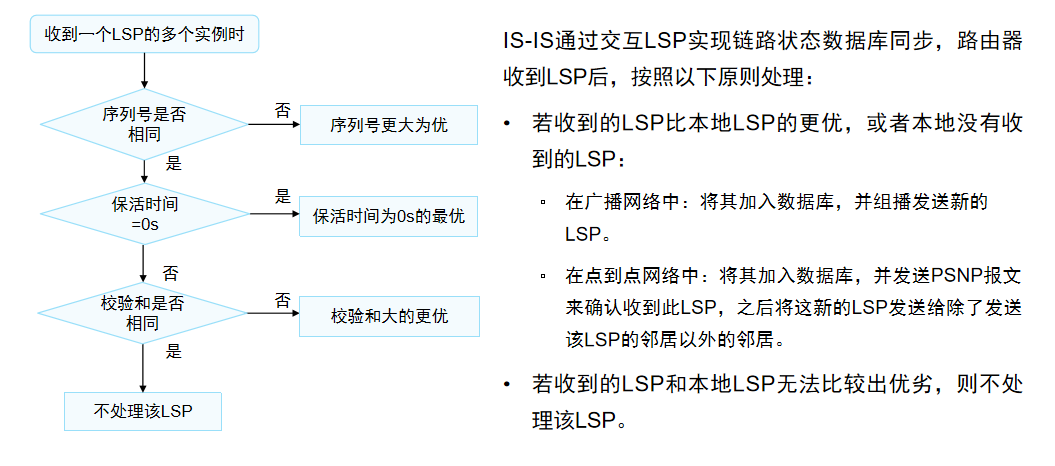

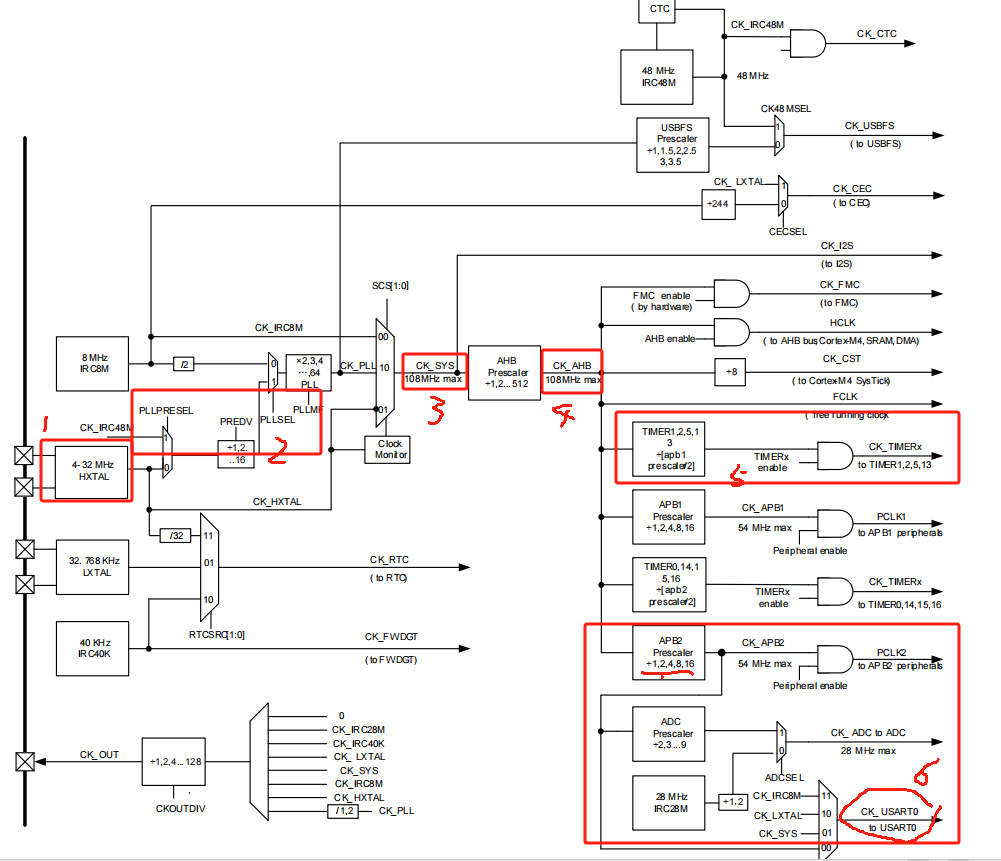

三、时钟树分析

目标是:找到TIMER5和USART0

从左往右分析:最左侧的四个方框为四种时钟源。要选择一个时钟源。

以HXTAL为例。

1、选择外部HXTAL时钟源(提供系统时钟频率)。

2、PLLPRESEL选择外部晶振作为PLL时钟源,经过PREDV分频,PLLSEL选择外部晶振作为PLL时钟源,经过PLL倍频得到CK_PLL,

3、通过SCS选择PLL时钟源作为系统时钟CK_SYS。

4、CK_SYS系统时钟通过分频得到CK_AHB,即为AHB总线的时钟频率。

5、 以TIMER1为例,TIMER1挂载APB1总线,APB1分频系数为2,则TIMER1频率为AHB÷[apb1 prescaler/2]=AHB,

6、 以USART0为例,USART0挂载APB2总线,通过APB2分频得到CK_APB2频率直接提供USART0使用。

四、修改参数步骤

1、设置外部晶振

外部晶振时钟频率,在gd32f30x.h文件中,根据实际外部晶振频率修改参数。示例选择外部晶振12M,其中HXTAL_VALUE即板子所焊接的外部晶振的宏定义。

/* define value of high speed crystal oscillator (HXTAL) in Hz */

#if !defined HXTAL_VALUE

#ifdef GD32F10X_CL

#define HXTAL_VALUE ((uint32_t)25000000) /*!< value of the external oscillator in Hz */

#else

#define HXTAL_VALUE ((uint32_t)12000000) /* !< from 4M to 16M *!< value of the external oscillator in Hz*/

#endif /* HXTAL_VALUE */

#endif /* high speed crystal oscillator value */2、选择外部时钟源。

在system_gd32f3x0.c文件,_SYS_OSC_CLK为系统时钟主频率选择宏定义,使用外部晶振选择__HXTAL。

3、 设置系统主频率大小

在system_gd32f3x0.c文件中例如:选择了72MHz作为时钟频率__SYSTEM_CLOCK_72M_PLL_HXTAL

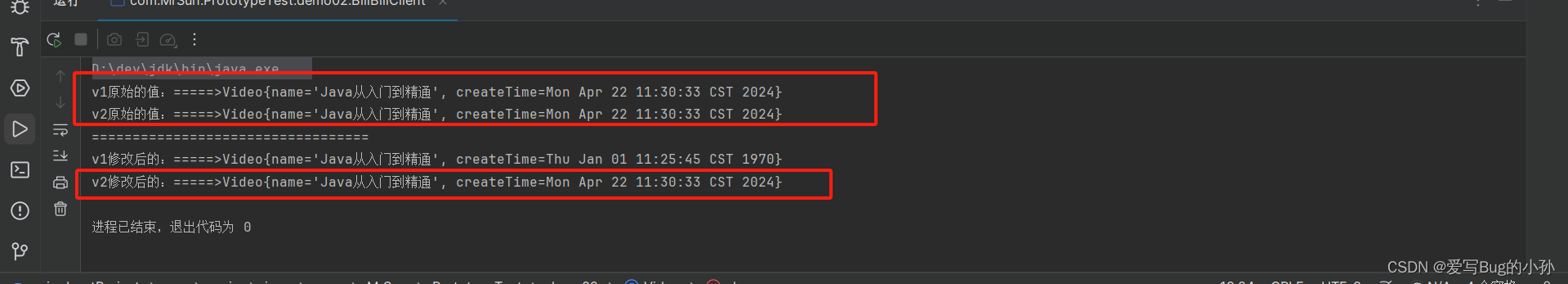

4、修改PLL分频倍频系数

在函数system_clock_72m_hxtal()内修改。

修改前:系统外部晶振HXTAL默认为8MHZ,带入公式:PLL = HXTAL * 9 = 72 MHz,PLL的倍频系数是9.

修改后:系统外部晶振HXTAL为12M,代入公式,PLL倍频系数为6

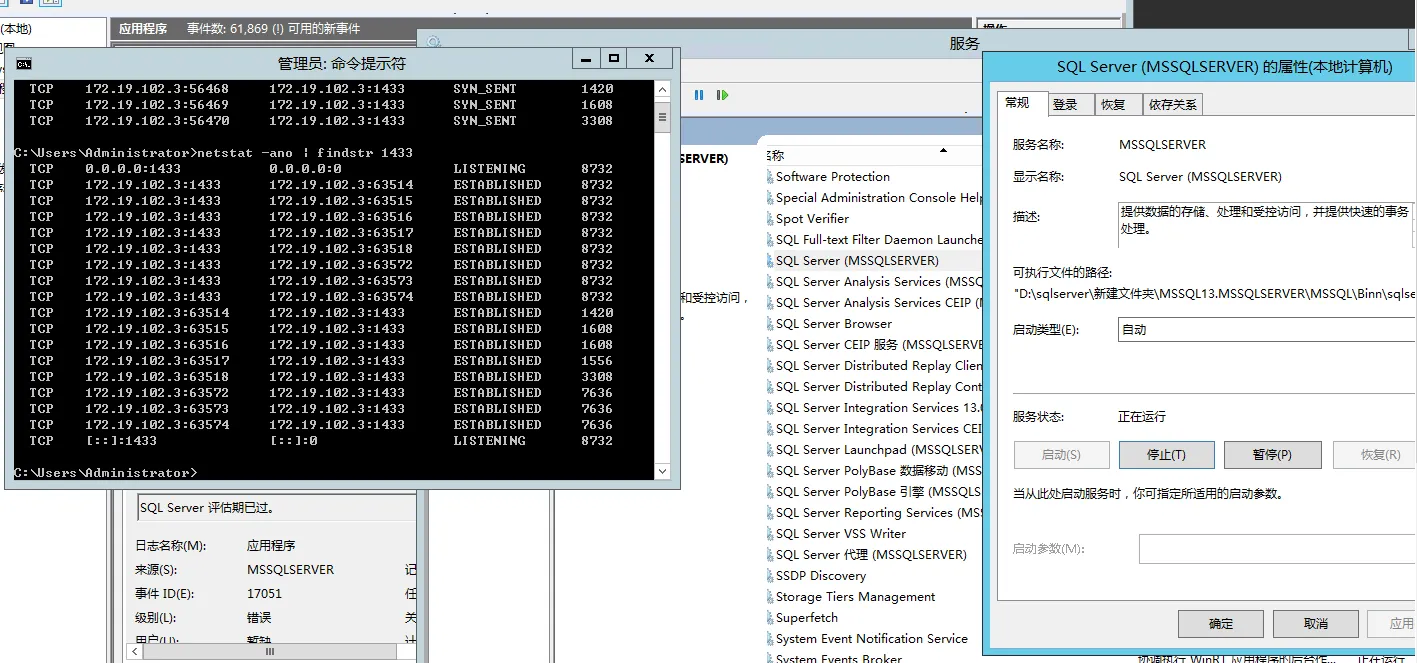

五、验证系统时钟的准确性

通过系统函数获取时钟配置,uint32_t rcu_clock_freq_get(rcu_clock_freq_enum clock)函数可用来获取时钟参数,

获取APB1时钟:uclk = rcu_clock_freq_get(CK_APB1);

获取APB2时钟:uclk = rcu_clock_freq_get(CK_APB2);

获取CK_AHB时钟:uclk = rcu_clock_freq_get(CK_AHB);

获取CK_SYS时钟:uclk = rcu_clock_freq_get(CK_SYS)。

详细的系统时钟频率配置参考链接:

GD32系列笔记四:时钟树Clock tree

GD32_时钟配置解析

【GD32】系统时钟解析

史上最详细的gd32时钟频率设置