目录

1.Cortex-M7 Core (主核心)

2.Cortex-M4 Core (从核心)

3.具体代码示例

(1)Cortex-M7 Core (主核心)

(2)Cortex-M4 Core (从核心)

(3)总结

4.额外的知识点:原子操作

(1)基本原子操作:

(2)复合原子操作:

(3)锁操作:

(4) 用途:

STM32H745BIT6上的两个ARM Cortex-M7和Cortex-M4核心共享SRAM4中的数据的方法可以是异步的,通过RTOS分时读写两个核心。使得其中一个核心将数据写入SRAM,而另一个核心从SRAM中读取数据并处理。

1.Cortex-M7 Core (主核心)

- 初始化系统,包括时钟、GPIO等。

- 设置适当的内存区域为共享RAM,并确保它对两个核心都是可见的。

- 在共享RAM中分配一块缓冲区,用于数据交换。

- 编写数据到共享RAM缓冲区。

- 使用原子操作或互斥锁确保写入操作的原子性(如果需要)。

- 通知Cortex-M4核心数据已准备好。

2.Cortex-M4 Core (从核心)

- 初始化系统,包括时钟、GPIO等。

- 设置适当的内存区域为共享RAM,并确保它对两个核心都是可见的。

- 在共享RAM中分配与Cortex-M7核心相同的缓冲区。

- 循环检查数据是否已准备好。

- 当接收到数据已准备好的通知时,从共享RAM缓冲区读取数据。

- 处理读取的数据。

- 将处理后的数据写回共享RAM缓冲区。

- 通知Cortex-M7核心数据已被处理。

3.具体代码示例

由于具体的编程语言和开发环境不同,这里仅提供伪代码作为参考:

(1)Cortex-M7 Core (主核心)

// 假设这是Cortex-M7核心的代码

#include <stdint.h>// 定义共享RAM中的缓冲区

volatile uint32_t shared_buffer[16];void init_sram()

{// 初始化SRAM,确保共享缓冲区可用

}void write_data_to_sram()

{// 将数据写入共享缓冲区for (int i = 0; i < sizeof(shared_buffer); i++) {shared_buffer[i] = i;}

}void notify_m4_data_ready()

{// 通知Cortex-M4核心数据已准备好

}int main()

{init_sram();while (1) {write_data_to_sram();notify_m4_data_ready();// 等待Cortex-M4处理完数据,可以通过某种信号量实现}return 0;

}(2)Cortex-M4 Core (从核心)

// 假设这是Cortex-M4核心的代码

#include <stdint.h>// 定义共享RAM中的缓冲区

volatile uint32_t shared_buffer[16];void init_sram()

{// 初始化SRAM,确保共享缓冲区可用

}void process_data_from_sram()

{// 从共享缓冲区读取数据并处理for (int i = 0; i < sizeof(shared_buffer); i++) {printf("Data from M7: %d\n", shared_buffer[i]);// 处理数据,例如:shared_buffer[i] *= 2;}

}void notify_m7_data_processed()

{// 通知Cortex-M7核心数据已被处理

}int main()

{init_sram();while (1) {// 检查数据是否已准备好,可以通过某种信号量实现if (data_is_ready()) {process_data_from_sram();notify_m7_data_processed();}}return 0;

}(3)总结

这只是一个简化的例子,只是提供了一种解决问题的思路。在实际应用中需要考虑更多的细节,比如错误处理、同步机制的选择(信号量、邮箱、共享变量等)、中断处理以及性能优化等。此外,更需要确保两个核心的时钟和外设访问控制正确配置,以便能够正确地访问共享SRAM。在具体实现时,还需要参考STM32H7xx的参考手册和HAL库提供的API来完成相应的配置和操作。

特别提醒,有使用外扩DPRAM经验的人,更容易理解和解决双核心ARM共享一片SRAM的技术问题,因为它们在解决共享数据的策略方面是相通的,DPRAM靠硬件逻辑控制对DPRAM的读写和刷新,而双核心的 ARM靠RTOS创建的原子性同步机制控制对SRAM的读写和刷新。

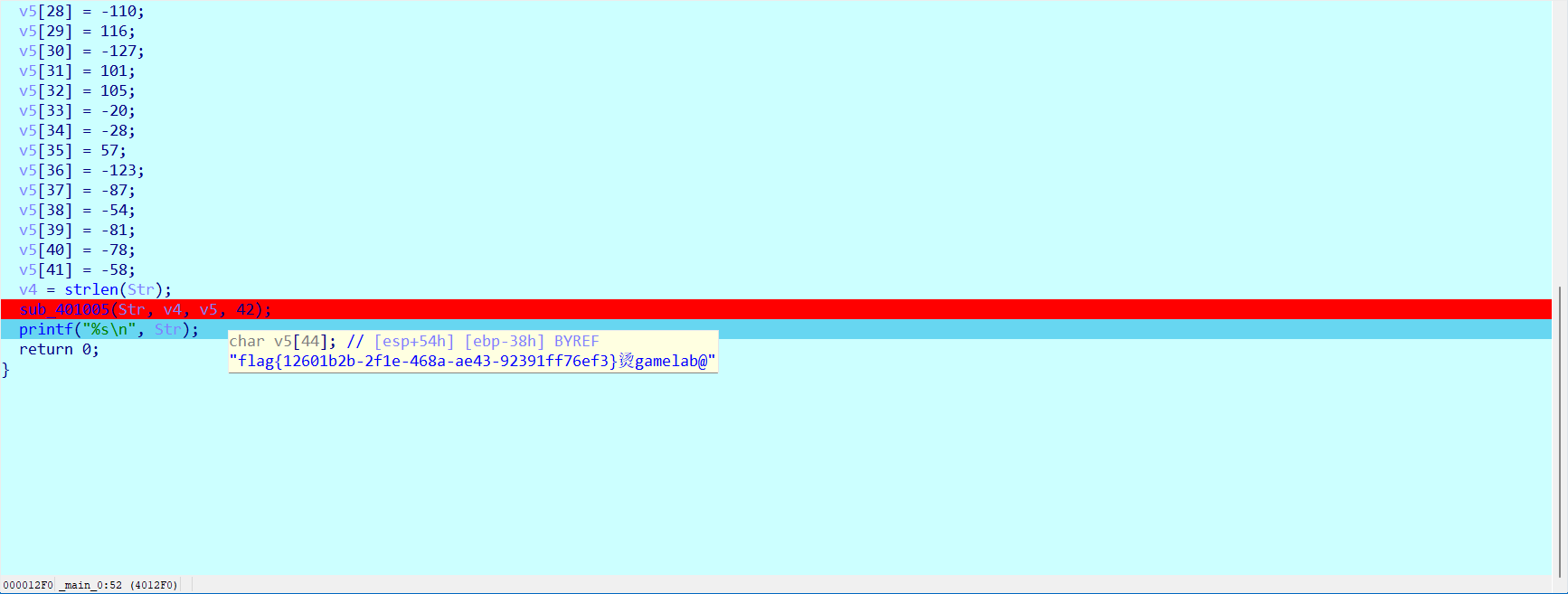

4.额外的知识点:原子操作

上面提到了原子操作,那么何为原子操作?原子操作可以分为以下几类:

(1)基本原子操作:

如加法、减法、赋值等,它们通常针对简单的数据类型(如整型)进行操作。

(2)复合原子操作:

如 compare-and-swap (CAS)、load-linked/store-conditional (LL/SC) 等,它们涉及多个步骤但被保证为原子性。

(3)锁操作:

获取锁和释放锁也是原子操作,它们用于互斥地访问共享资源。

(4) 用途:

原子操作在并发编程中有广泛的应用,例如在实现线程安全的数据结构、同步机制以及锁等时都会用到。由于原子操作具有不可分割的特性,它们通常由硬件指令来支持,以保证其性能和效率。在高级编程语言中,往往有对应的库或函数来封装这些原子操作,使得程序员在编写多线程程序时可以更方便地使用它们。