大家知道咱们社区近期TSMC 12nm ARM Cortexa-A72(1P9M 6Track Metal Stack)已经开班。这里小编要强调一点:不要认为跑了先进工艺的项目就会很有竞争力!如果你仅仅是跑个先进工艺的flow,不懂先进工艺在数字IC后端实现上的不同点,为何有这样的不同点,针对这些不同之处后端实现阶段如何考虑它们,那么你等于0经验!

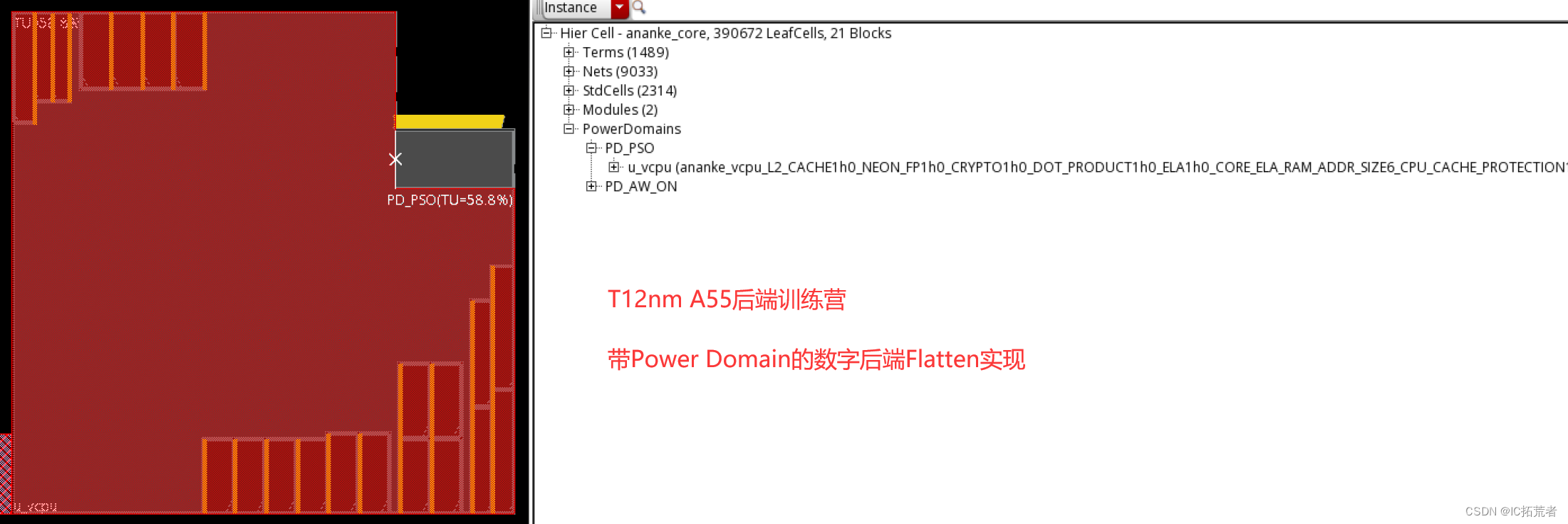

PS: TSMC 12nm ARM A55低功耗设计实现后端训练营也开放预约啦!有需要的可以私信,名额限8人。

所以,小编觉得有必要列举下T12这个工艺后端实现上一些不一样的地方。大家可以针对本文所列的要点进行复盘,如果这些都搞透彻了,你就可以大胆把T12 nm的A72和A55项目写到你的简历中。初步估计这个T12工艺的A72项目会成为新一年IC秋招的标配项目。

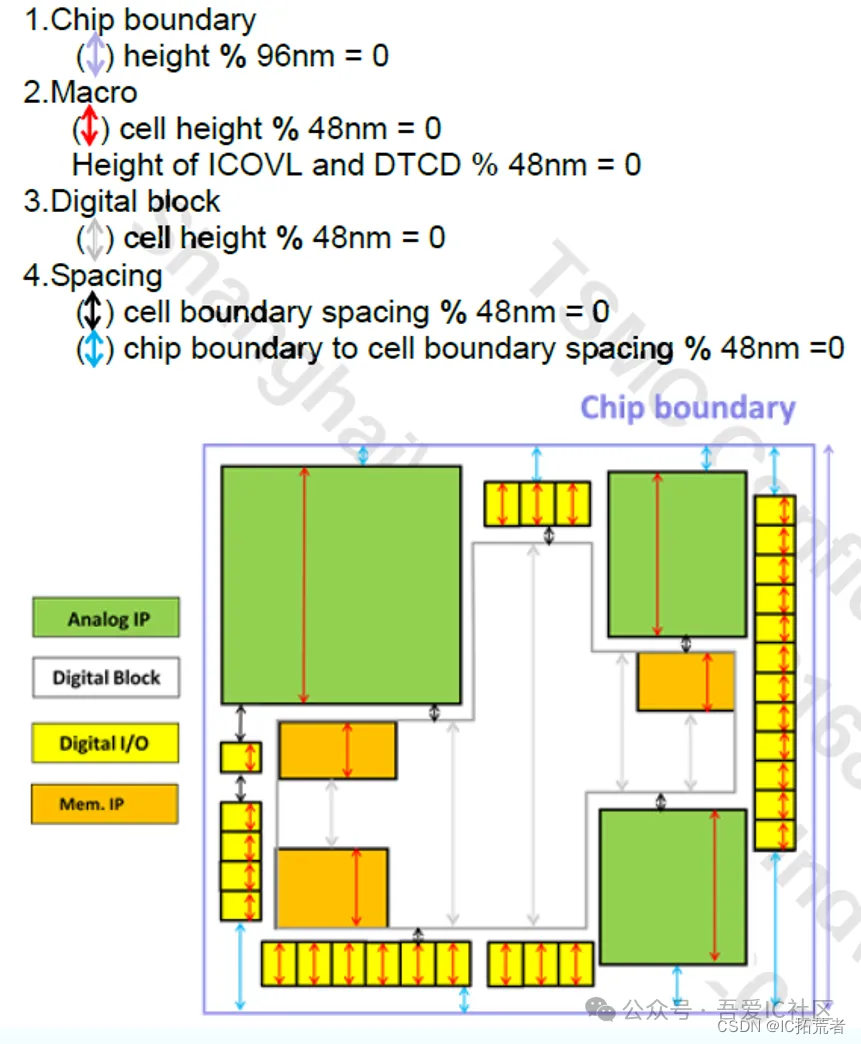

1)Memory,模拟IP,子模块,IO必须摆放到Placement Grid(Fin Grid)上 (DPT Aware Floorplan )

所有各个子模块的形状,彼此之间的间距都是有严格的要求。这里面的48nm和96nm值是怎么来的?这些都要搞通透。

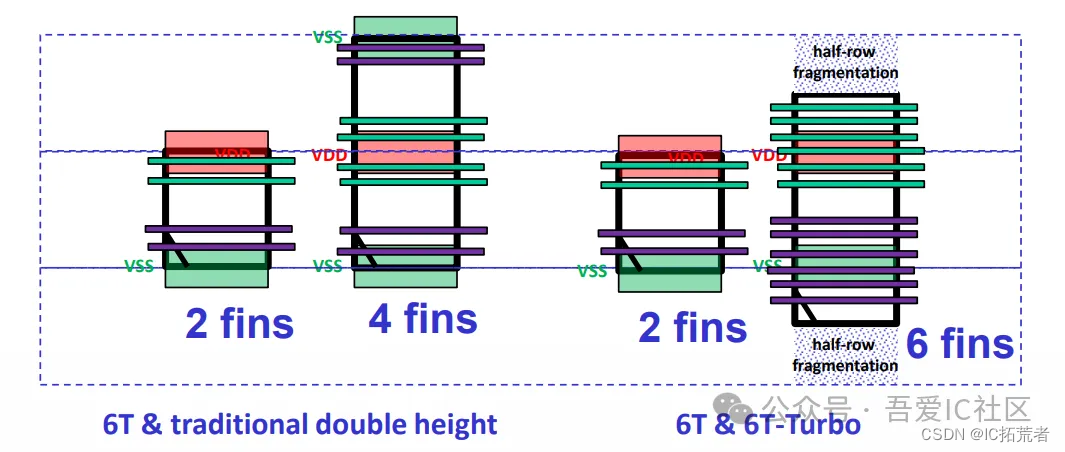

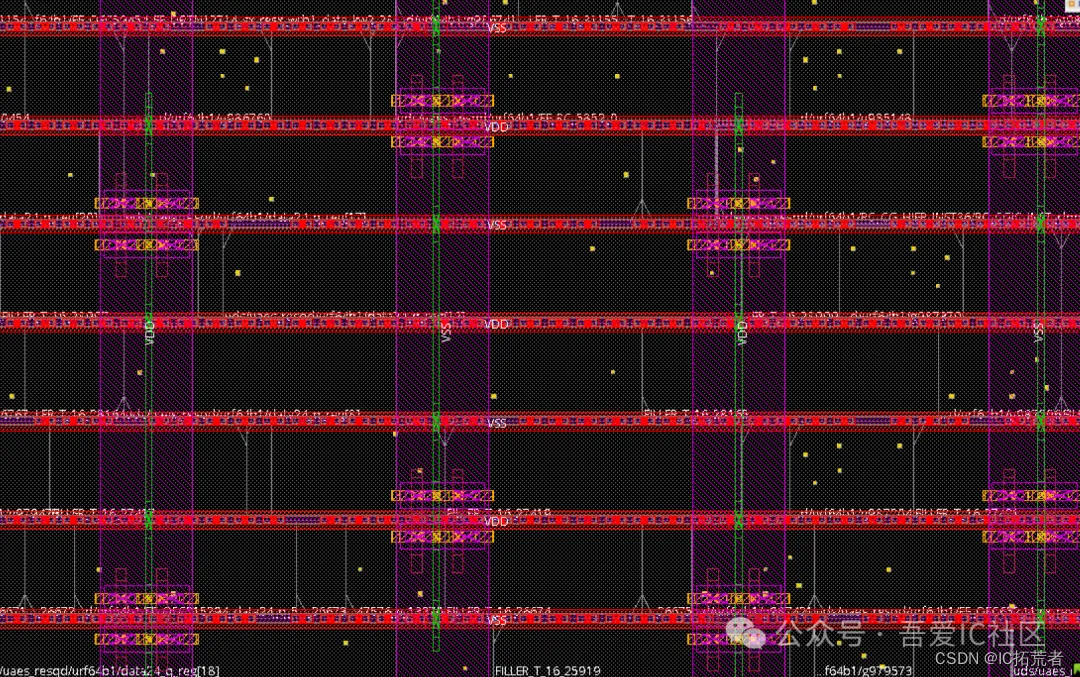

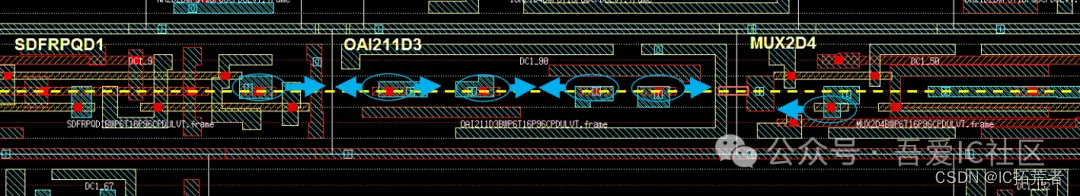

2)PPNN Placement and Filler Insertion

T12 6Track工艺引入了6T-Turbo的cell。为何要用这类cell?使用这类cell的优缺点分别是什么?

使用这类6T-Turbo cell时应该如何插filler?这类6T-Turbo cell的density是否有严格的要求?

3)Via Pillar(Via Stapling)

从T12nm开始powerplan就必须使用via pillar。这样打的目的以及整体powerplan结构需要搞清楚。

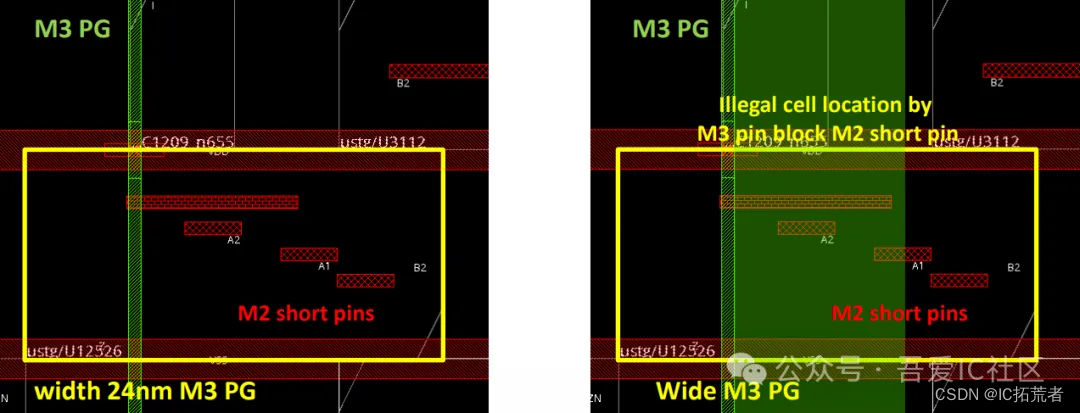

4)M3 PG结构特殊处理

在12nm这个工艺中标准单元存在比较多的M2 short pin,所以在我们规划powerplan结构和PR flow过程中都需要提前考虑好这个情况。

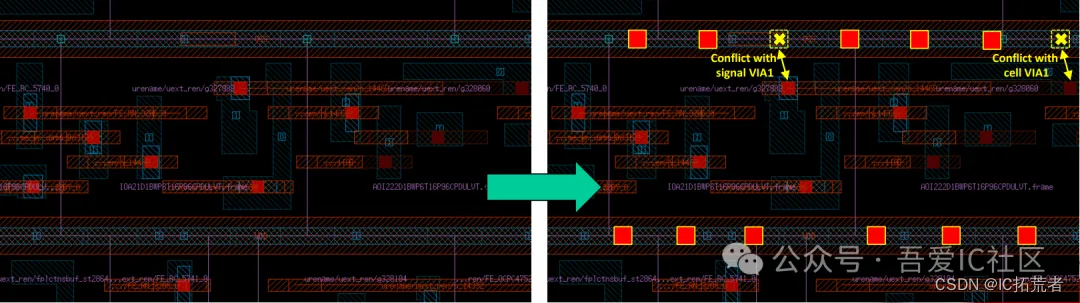

5)M1&M2 Dual Power Rail

使用Dual Power Rail的目的是什么?对于T12工艺是否可以在powerplan阶段就把M1和M2之间的VIA1打上?为什么?

数字IC后端实现Dual Rail实现要点" />

数字IC后端实现Dual Rail实现要点" />

6)模块级io port摆放需要摆放至高层Layer

T12这个工艺的M1-M3属于double pattern layer。在模块级摆放io port时尽量不要使用这些layer!

7)Colorless Placement (与pre-color有何区别?)

什么叫Colorless?它和pre-color有何区别?它们对数字IC后端实现流程有何影响?

CPODE.L.2这条DRC Violation的原因是什么?如何解决?

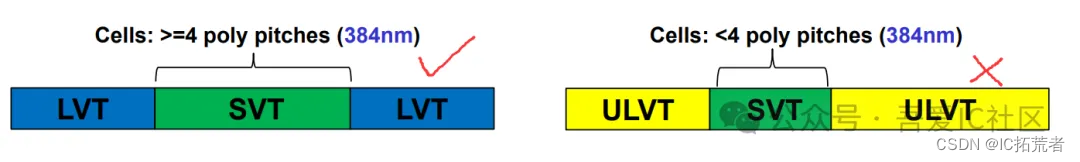

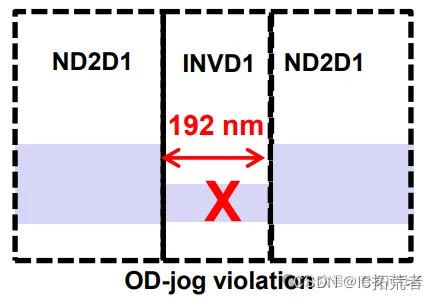

如何在placement阶段避免VT的min width,min area等DRC Violation?

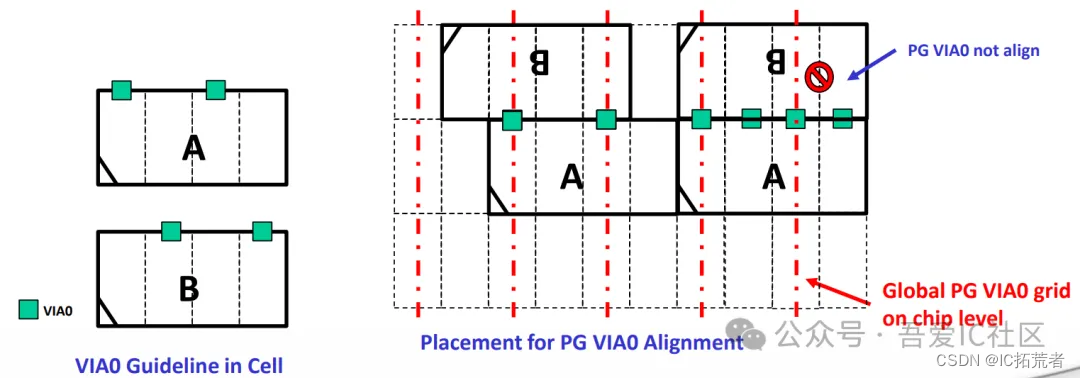

8)VIA0 Align issue

VIA0是什么?它的作用是什么?VIA0特殊的Align要求,如何变成placement相关约束来guide工具做placement?

数字IC后端培训VIA0对齐" />

数字IC后端培训VIA0对齐" />

9)VT layer aware placement

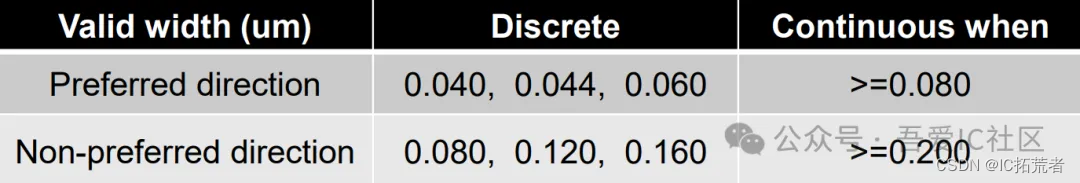

10)New Routing Rule

T12这个工艺也是支持Preferred和Non-prefered两个方向来完成routing的,但是它对它们的最小线宽和最小线间距提出了更严格的要求。

11)M2 short pin延伸技术

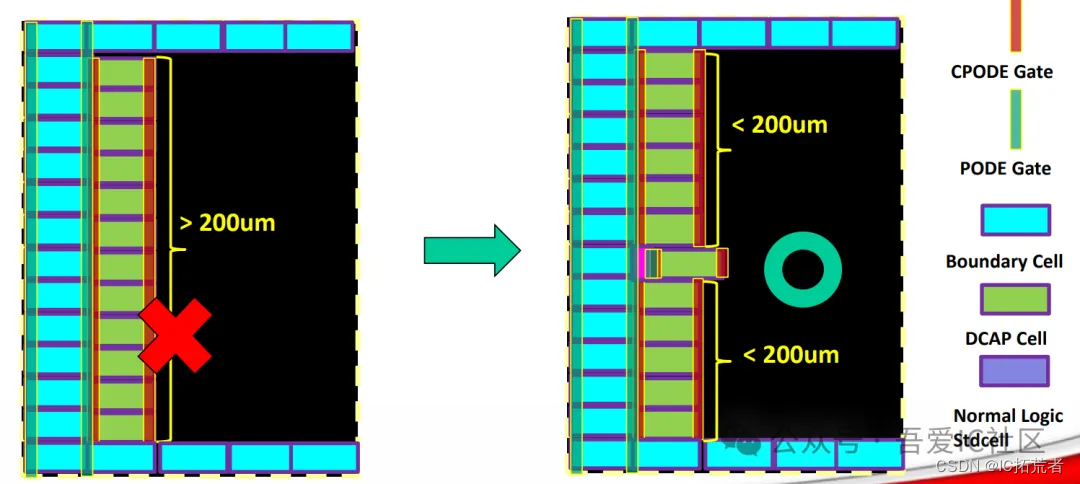

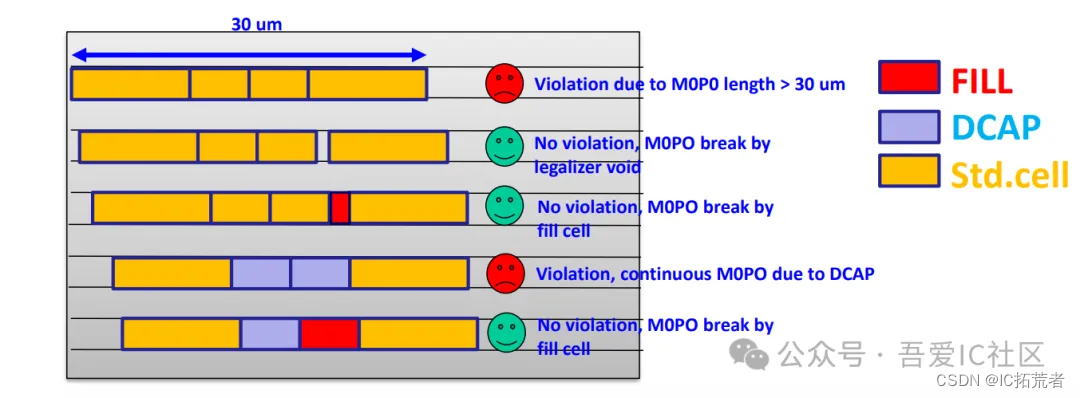

12)MOPO Max Length Violation

数字IC后端设计实现MOPO Violation分析" />

数字IC后端设计实现MOPO Violation分析" />

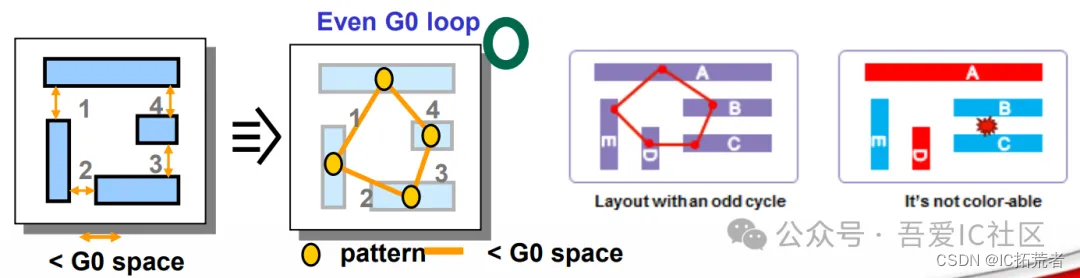

13)Double Pattern Routing (G0 Loop Violation)

G0 Loop Violation的本质问题是什么?如何提前规避?Calibre出现G0 DRC Violation后应该如何修复?

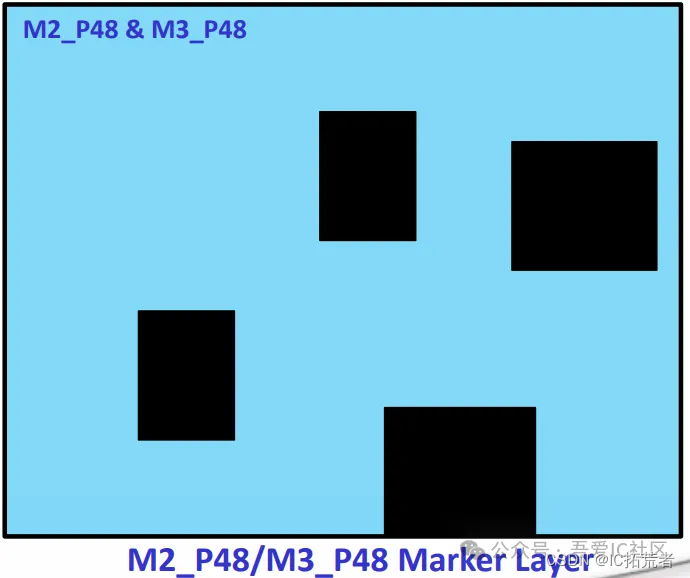

14)M2_P48/M3_P48 marker layer generation

为何要有P48这一层?P48这一层应该在什么阶段添加?这层是否需要参与Tapeout?

TSMC12nm M2 P48和M3 P48 layer添加方法" />

TSMC12nm M2 P48和M3 P48 layer添加方法" />

15)Timing Signoff之SOCV