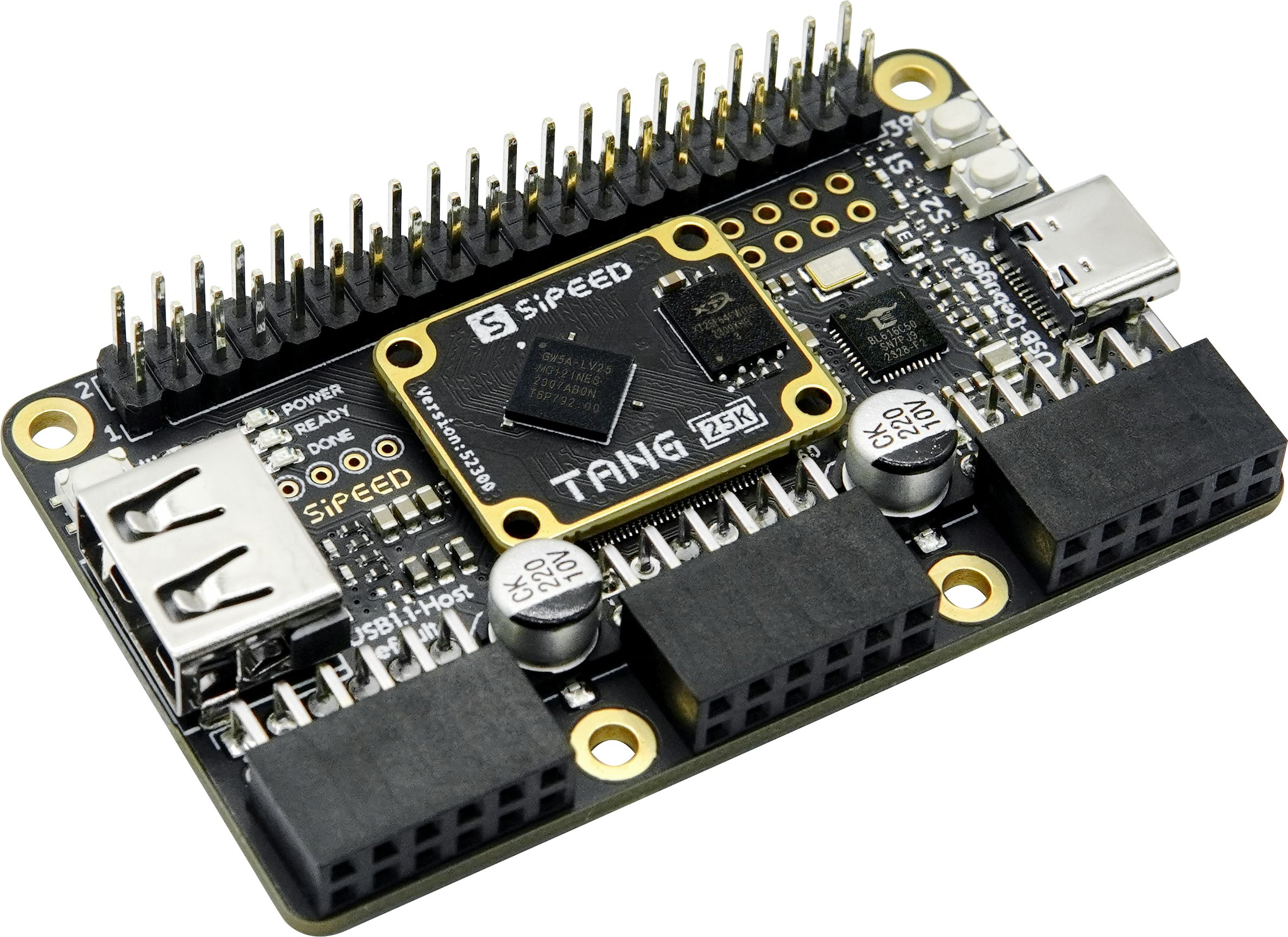

Tang Primer 25K

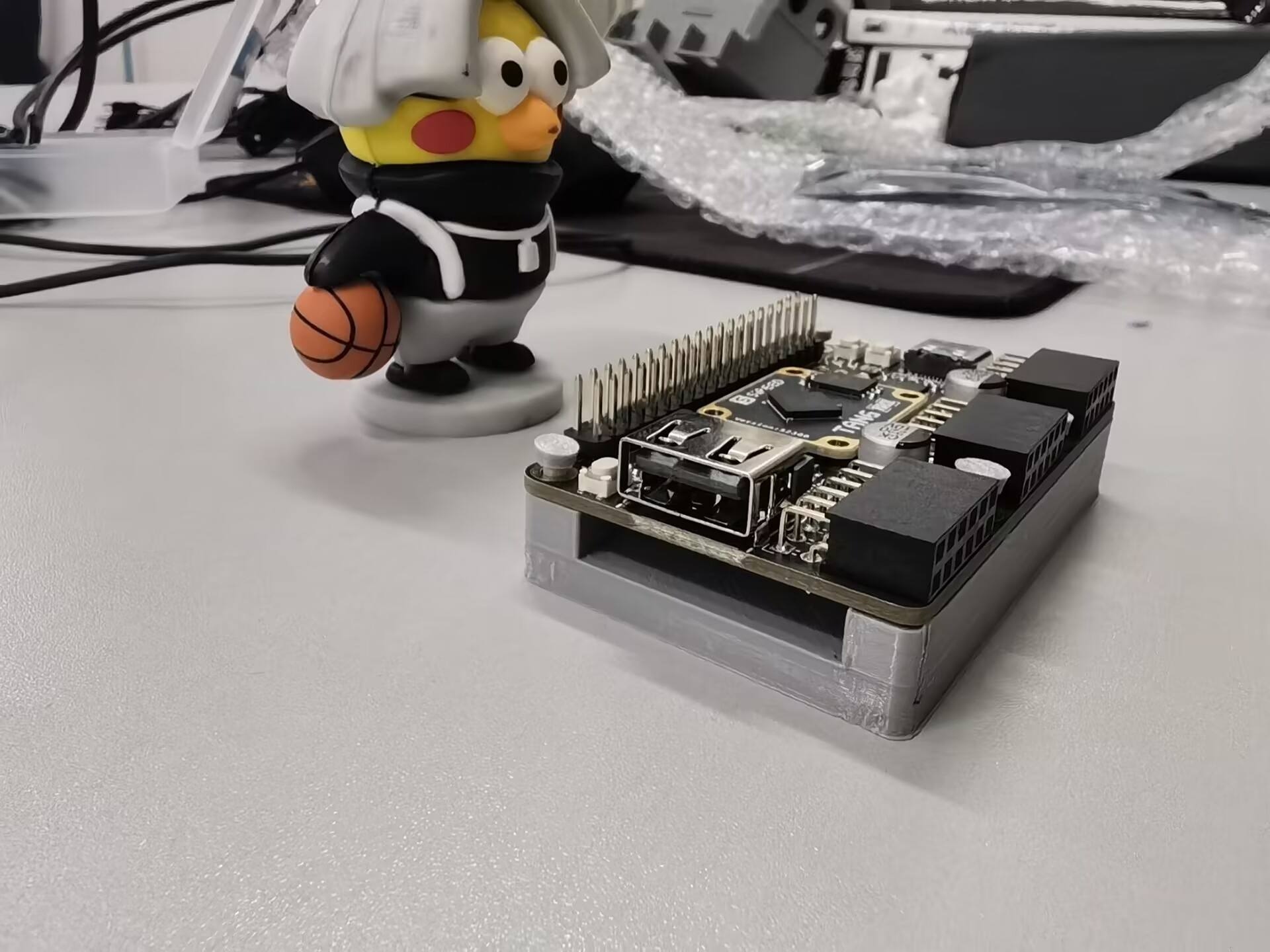

Tang Primer 25K 是基于 GW5A-LV25MG121 所设计的一款极小封装的核心板(23x18mm),并配套全引脚引出(除MIPI高速脚外)的25K Dock底板。(国产高云FPGA),作为学习使用,非常小巧,大家可以购买(底板的3d保护壳可以使用博主的,建议打印一个,因为fpga开发板这种海上比较脆弱,如果碰到静电什么),博主是去年购买了吃灰了好久,现在有空拿出来玩玩。

底板和螺丝百度网盘链接:

链接:https://pan.baidu.com/s/1encetriBSqsJffrh5WDdyw

提取码:23o3

具体资料可以到

链接:https://wiki.sipeed.com/hardware/zh/tang/tang-primer-25k

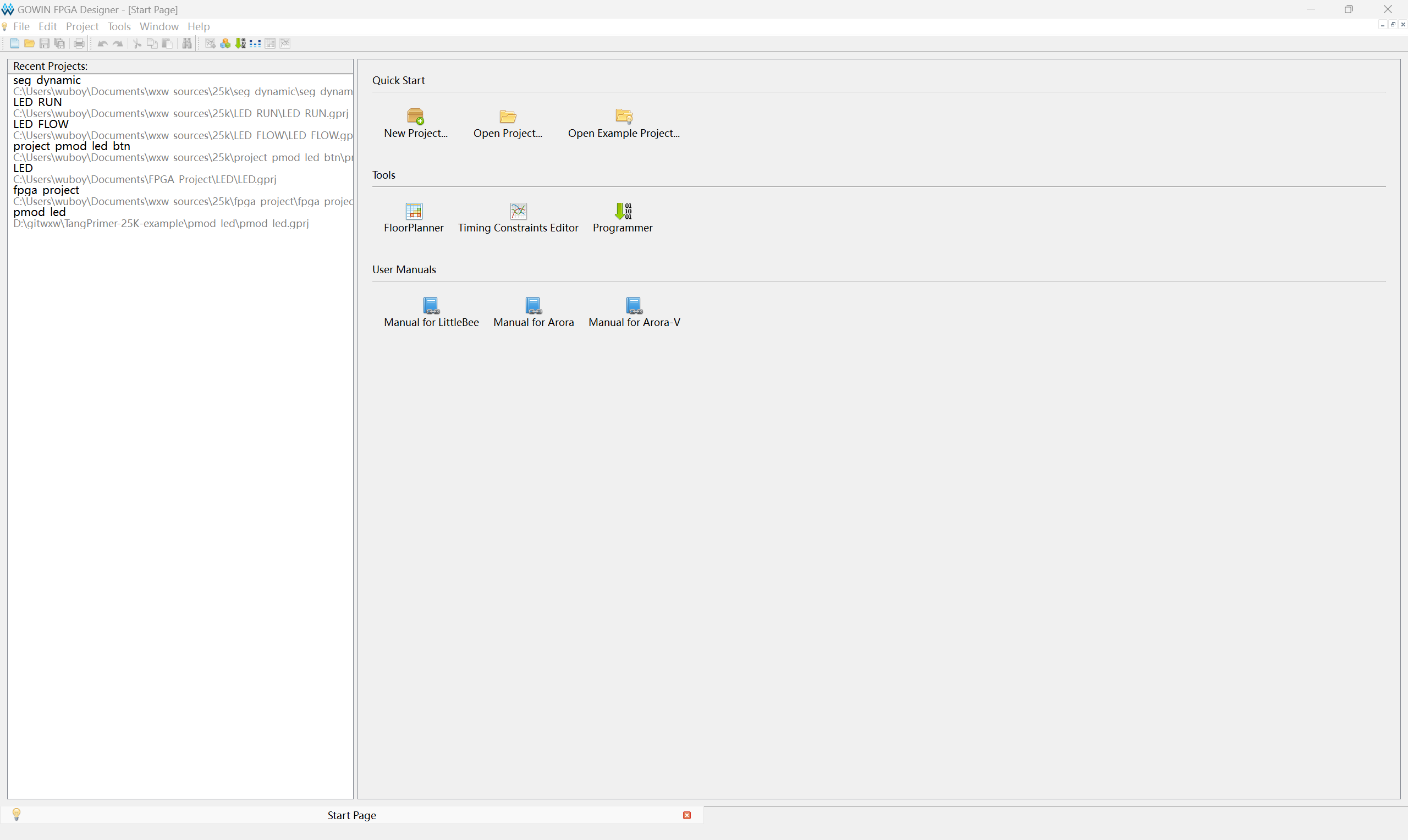

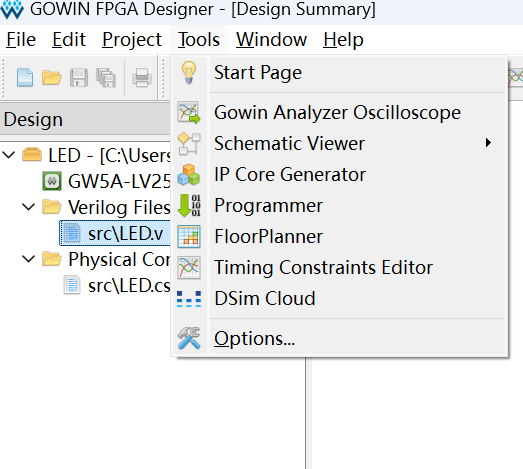

安装Gaowin IDE

注意25K需要使用 V1.9.9Beta-4 或更新的IDE版本(教育版本就ok)

下载链接:http://www.gowinsemi.com.cn/faq.aspx

板子上面芯片为GW5A-LVMG121NES,但是教育版本上是GW5A-LV25MG121NC1/I0,我问过客服,一样使用就ok。

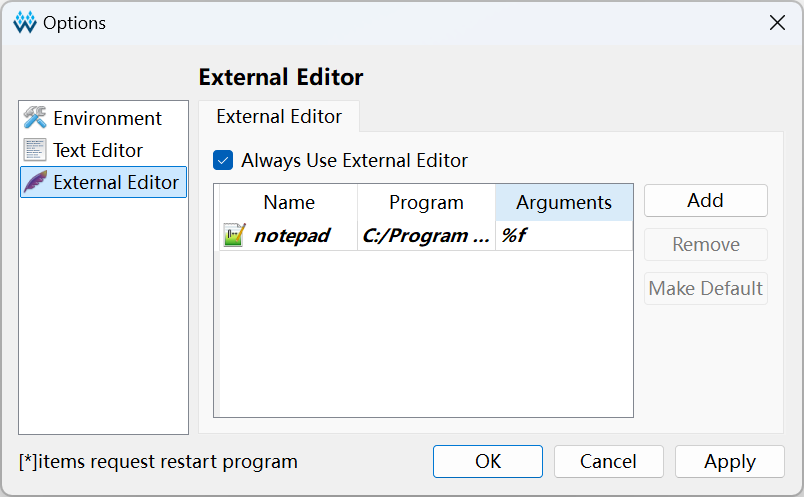

可以设置外部编辑器(vscode或者notepad++)

FPGA学习记录

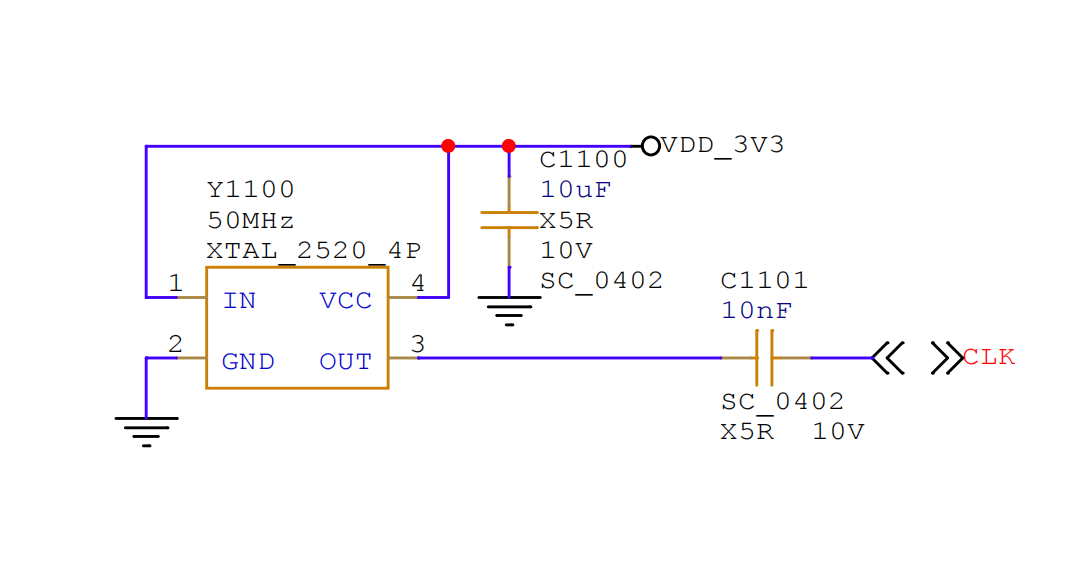

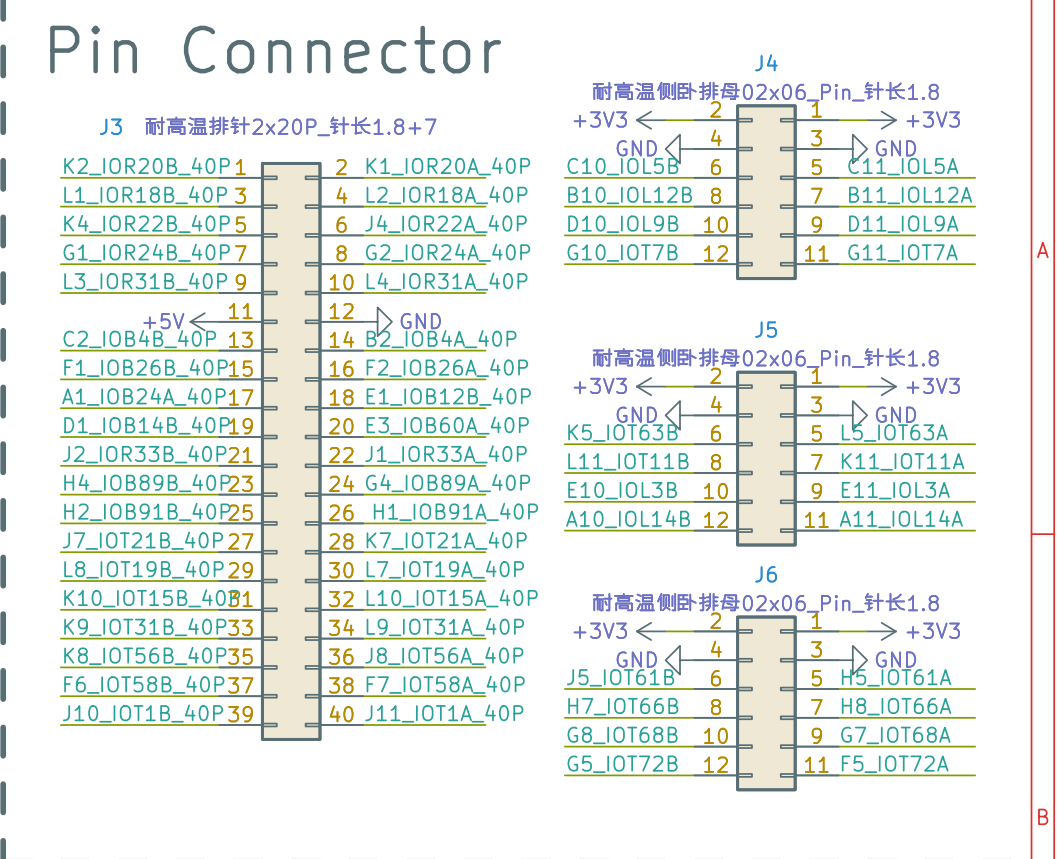

看原理图

点灯

verilog code

module LED_FLOW(input clk,input reset_n,output reg [7:0]led

);reg [25:0] counter;initial

beginled=8'hff;counter=26'd0;

end// 定义参数

parameter CLK_FREQ = 50_000_000; // 时钟频率50MHz

parameter BLINK_PERIOD = 1; // 闪烁周期1秒

localparam COUNTER_MAX = CLK_FREQ * BLINK_PERIOD - 1; // 计数器最大值always @(posedge clk or negedge reset_n)

beginif (!reset_n)counter <= 26'd0;else if (counter < COUNTER_MAX) // 1scounter <= counter + 1'b1;elsecounter <= 26'd0;

endalways @(posedge clk or negedge reset_n)

beginif (!reset_n)led <= 8'hff;else if (counter == COUNTER_MAX) // 1sled<=~led;elseled<=led;

endendmodule

跑马灯

verilog code

module LED_RUN(input clk,input reset_n,output reg [7:0]led

);reg [25:0] counter;initial

beginled=8'hfe;counter=26'd0;

end// 定义参数

parameter CLK_FREQ = 50_000_000; // 时钟频率50MHz

parameter BLINK_PERIOD = 1; // 闪烁周期1秒

localparam COUNTER_MAX = CLK_FREQ * BLINK_PERIOD - 1; // 计数器最大值always @(posedge clk or negedge reset_n)

beginif (!reset_n)counter <= 26'd0;else if (counter < COUNTER_MAX) // 1scounter <= counter + 1'b1;elsecounter <= 26'd0;

endalways @(posedge clk or negedge reset_n)

beginif (!reset_n)led <= 8'hff;else if (counter == COUNTER_MAX) // 1sled<={led[6:0],~led[7]};elseled<=led;

endendmodule

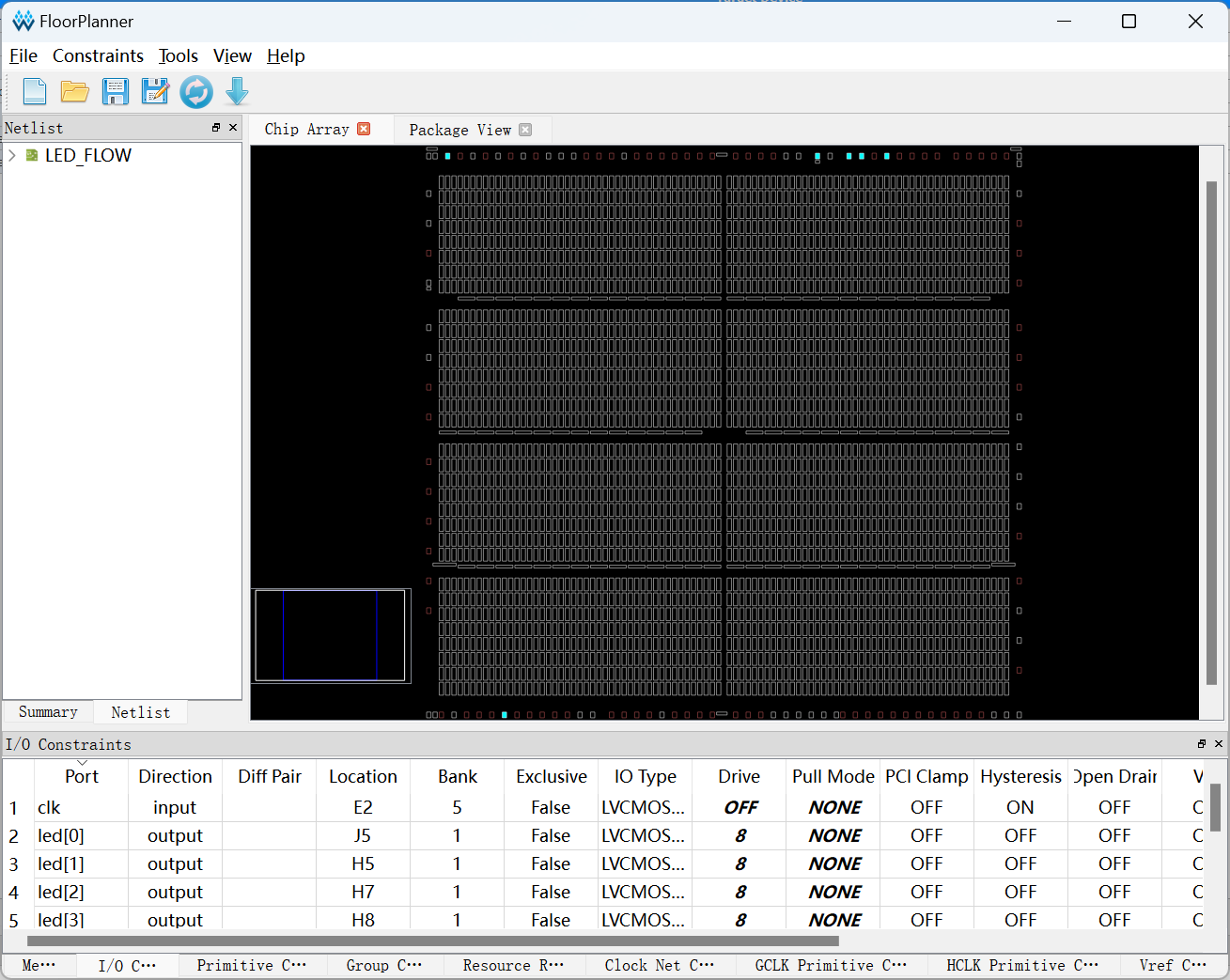

流水灯

verilog code

module LED_FLOW(input clk,input reset_n,output reg [7:0]led

);reg [25:0] counter;initial

beginled=8'hfe;counter=26'd0;

end// 定义参数

parameter CLK_FREQ = 50_000_000; // 时钟频率50MHz

parameter BLINK_PERIOD = 1; // 闪烁周期1秒

localparam COUNTER_MAX = CLK_FREQ * BLINK_PERIOD - 1; // 计数器最大值always @(posedge clk or negedge reset_n)

beginif (!reset_n)counter <= 26'd0;else if (counter < COUNTER_MAX) // 1scounter <= counter + 1'b1;elsecounter <= 26'd0;

endalways @(posedge clk or negedge reset_n)

beginif (!reset_n)led <= 8'hfe;else if (counter == COUNTER_MAX) // 1sled<={led[6:0],led[7]};elseled<=led;

endendmodule

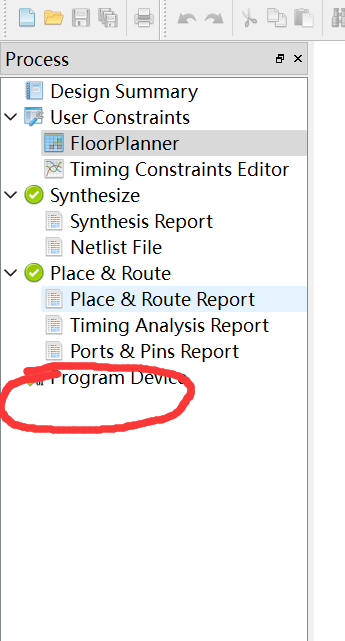

重要注意事项

多少引脚填写H多少就可以,那个原理图里面的。

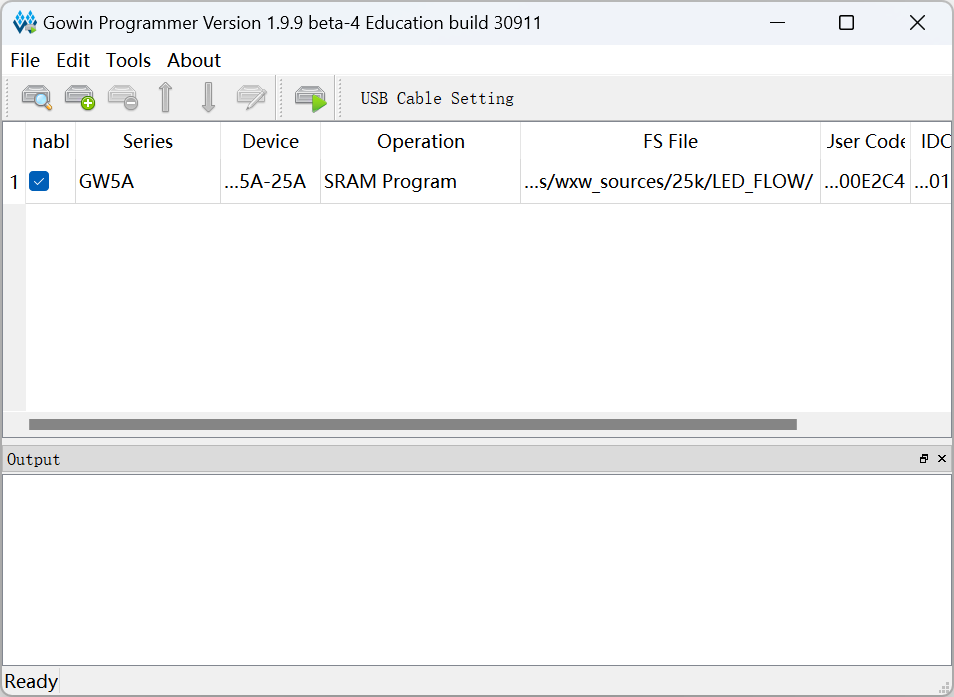

烧写建议烧到sram,节省flash寿命

视频演示

FPGA学习记录