一、串行通信

串行通信分为两种方式:同步串行通信和异步串行通信。

同步串行通信需要通信双方在同一时钟的控制下,同步传输数据。

异步串行通信是指通信双方使用各自的时钟控制数据的发送和接收过程。

二、UART

UART串口通信需要两根信号线来实现,一根用于串口发送,另外一根负责串口接收。

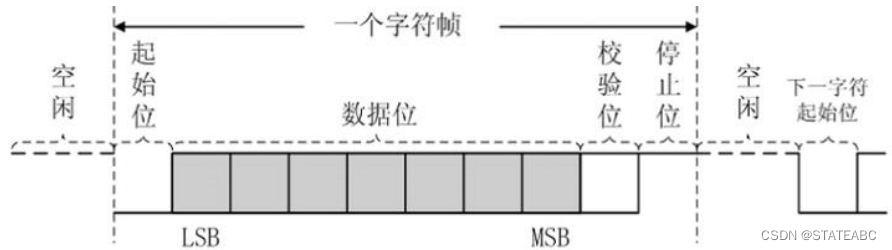

UART在发送或接收过程中的一帧数据由4部分组成,起始位(低电平)、数据位、奇偶校验位和停止位(高电平)。

起始位标志着一帧数据的开始,停止位标志着一帧数据的结束,数据位是一帧数据中的有效数据。

校验位分为奇校验和偶校验,用于检验数据在传输过程中是否出错。奇校验时,发送方应使数据位中1的个数与校验位中1的个数之和为奇数;接收方在接收数据时,对1的个数进行检查,若不为奇数,则说明数据在传输过程中出了差错。同样,偶校验则检查1的个数是否为偶数。

UART通信过程中的数据格式及传输速率是可设置的,数据位可选择为 5、6、7、8位(最常用);校验位可选择奇校验、偶校验或者无校验位;停止位可选择1位(默认),1.5或2位。

串口通信的速率用波特率表示,它表示每秒传输二进制数据的位数,单位是bps(位/秒),常用的波特率有9600、19200、38400、57600以及115200等。

FPGA开发串口中,为了得到串口传输一位数据所需要的系统时钟周期数,需要对系统时钟进行计数,计数方法为FPGA时钟频率/波特率。如时钟频率为50000000hz(50MHz),需要的比特率为9600bps,则需要计数50000000/9600≈5208次

三、串口实现

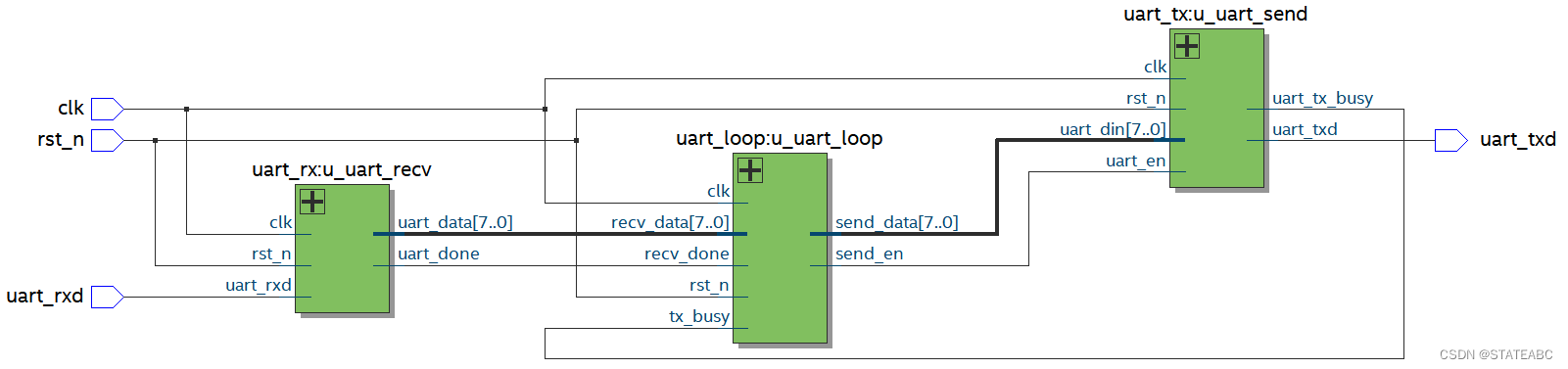

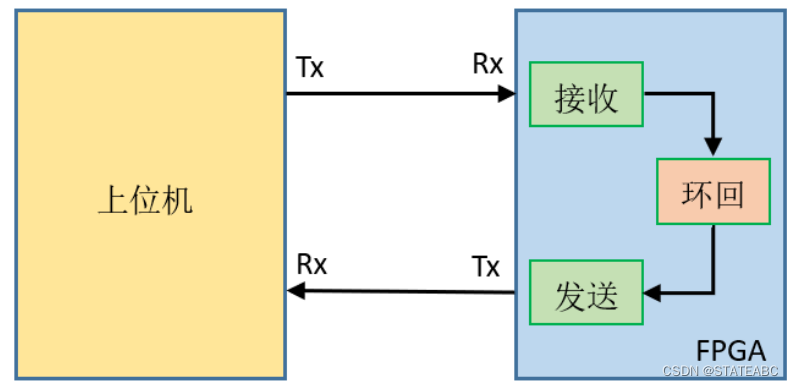

上位机通过串口调试助手发送数据给FPGA,FPGA 通过USB串口接收数据并将接收到的数据发送给上位机,完成串口数据环回。

首先要有一个接收模块,接收串口调试助手发送的数据

module uart_rx(//**************输入**************input clk, //系统50MHz时钟input rst_n, //系统复位,低电平有效 input uart_rxd, //UART接收端口//**************输出**************output reg uart_done, //接收一帧数据完成标志output reg rx_flag, //接收标志位output reg [3:0] rx_cnt, //接收数据计数器output reg [7:0] rxdata, //接收端口数据寄存output reg [7:0] uart_data //接收的数据);//************参数定义************

parameter CLK_FREQ = 50000000; //系统时钟

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //波特率计数,串口传输一位所需要的系统时钟周期数//************信号定义************

reg uart_rxd_1; //异步信号会带来亚稳态,常用处理方式是打拍处理,第一拍

reg uart_rxd_2; //第二拍,通常打两拍就基本上就能避免亚稳态问题

reg [15:0] clk_cnt; //系统时钟计数器wire start_flag; //起始标志位//检测接收端口下降沿来捕获起始位,输出一个时钟周期的脉冲start fag,并进入串口接收过程

assign start_flag = uart_rxd_2 & (~uart_rxd_1); //对UART接收端口的数据延迟两个时钟周期避免亚稳态

always @(posedge clk or negedge rst_n) begin if (!rst_n) begin uart_rxd_1 <= 1'b0;uart_rxd_2 <= 1'b0; endelse beginuart_rxd_1 <= uart_rxd; uart_rxd_2 <= uart_rxd_1;end

end//当脉冲信号start_flag有效,进入数据接收过程

always @(posedge clk or negedge rst_n) begin if (!rst_n)rx_flag <= 1'b0;else begin//检测到起始位,进入数据接收过程,标志位rx_flag拉高if(start_flag)rx_flag <= 1'b1;//当接收数据计数器计数到9(9个波特周期)且在停止位中间(数据寄存已经完成,为检测下一帧数据起始位准备),停止接收,标志位rx_flag拉低 else if((rx_cnt == 4'd9) && (clk_cnt == BPS_CNT/2)) rx_flag <= 1'b0;elserx_flag <= rx_flag;end

end//进入数据接收过程启动系统时钟计数器

always @(posedge clk or negedge rst_n) begin if (!rst_n) clk_cnt <= 16'd0;//标志位rx_flag有效,处于接收过程 else if (rx_flag) begin//计数没到一个波特率周期则一直计数,到了则清零 if (clk_cnt < BPS_CNT - 1)clk_cnt <= clk_cnt + 1'b1;elseclk_cnt <= 16'd0;end//数据接收过程结束,计数器清零else clk_cnt <= 16'd0;

end//进入数据接收过程启动接收数据计数器

always @(posedge clk or negedge rst_n) begin if (!rst_n) rx_cnt <= 4'd0; else if (rx_flag) begin//系统时钟计数到一个波特率周期,接收数据计数器加1,没到则不加if (clk_cnt == BPS_CNT - 1) rx_cnt <= rx_cnt + 1'b1; //可以用来判断当前传输的是第几位elserx_cnt <= rx_cnt; end//接收过程结束,计数器清零elserx_cnt <= 4'd0;

end//根据接收数据计数器来寄存uart接收端口数据

always @(posedge clk or negedge rst_n) begin if (!rst_n) rxdata <= 8'd0; else if(rx_flag)//计数到数据中间的采样结果最稳定if (clk_cnt == BPS_CNT/2) begincase (rx_cnt)//根据rx_cnt的值将uart接收端口的数据寄存到接收数据寄存器对应的位实现串并转换4'd1 : rxdata[0] <= uart_rxd_2; //寄存数据位最低位4'd2 : rxdata[1] <= uart_rxd_2;4'd3 : rxdata[2] <= uart_rxd_2;4'd4 : rxdata[3] <= uart_rxd_2;4'd5 : rxdata[4] <= uart_rxd_2;4'd6 : rxdata[5] <= uart_rxd_2;4'd7 : rxdata[6] <= uart_rxd_2;4'd8 : rxdata[7] <= uart_rxd_2; //寄存数据位最高位default:; endcaseendelse rxdata <= rxdata;elserxdata <= 8'd0;

end//数据接收完毕后给出标志信号并寄存输出接收到的数据

always @(posedge clk or negedge rst_n) begin if (!rst_n) beginuart_data <= 8'd0; uart_done <= 1'b0;end//接收数据计数器计数到停止位时,寄存输出接收到的数据并将接收完成标志位拉高else if(rx_cnt == 4'd9) begin uart_data <= rxdata; uart_done <= 1'b1; endelse beginuart_data <= 8'd0; uart_done <= 1'b0; end

endendmodule 然后还需要一个发送模块,将数据发送给PC端,原理同接收模块大部分一致

module uart_tx(//**************输入************** input clk, //系统50MHz时钟input rst_n, //系统复位,低电平有效 input uart_en, //发送使能信号input [ 7:0] uart_din, //待发送数据//**************输出**************output uart_tx_busy, //发送忙状态标志 output en_flag, //使能标志位output reg tx_flag, //发送过程标志信号output reg [ 7:0] tx_data, //寄存发送数据output reg [ 3:0] tx_cnt, //发送数据计数器output reg uart_txd //UART发送端口);//************参数定义************

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //波特率计数,串口传输一位所需要的系统时钟周期数//************信号定义************

reg uart_en_1;

reg uart_en_2;

reg [15:0] clk_cnt; //系统时钟计数器//在串口发送过程中给出忙状态标志,其他模块就可以判断串口发送模块是否处于空闲状态

assign uart_tx_busy = tx_flag;//捕获uart_en上升沿,得到一个时钟周期的脉冲信号,进入数据发送过程

assign en_flag = (~uart_en_2) & uart_en_1;//对发送使能信号uart_en延迟两个时钟周期避免亚稳态

always @(posedge clk or negedge rst_n) begin if (!rst_n) beginuart_en_1 <= 1'b0; uart_en_2 <= 1'b0;end else begin uart_en_1 <= uart_en; uart_en_2 <= uart_en_1; end

end//当脉冲信号en_flag到达时,寄存待发送的数据,进入发送过程

always @(posedge clk or negedge rst_n) begin if (!rst_n) begin tx_flag <= 1'b0;tx_data <= 8'd0;end //检测到发送使能上升沿,进入发送过程,标志位tx_flag拉高,寄存待发送数据else if (en_flag) begin tx_flag <= 1'b1;tx_data <= uart_din;end//计数到停止位结束时,停止发送过程,标志位tx_flag拉低 else if ((tx_cnt == 4'd9) && (clk_cnt == BPS_CNT - (BPS_CNT/16))) begin //提前1/16个停止位拉低,保证发送数据时间略小于接收数据时间,避免数据积累造成丢失tx_flag <= 1'b0; tx_data <= 8'd0;endelse begintx_flag <= tx_flag;tx_data <= tx_data;end

end//进入发送过程后,启动系统时钟计数器

always @(posedge clk or negedge rst_n) begin if (!rst_n) clk_cnt <= 16'd0; else if (tx_flag) begin if (clk_cnt < BPS_CNT - 1)clk_cnt <= clk_cnt + 1'b1;elseclk_cnt <= 16'd0; endelse clk_cnt <= 16'd0;

end//进入发送过程后,启动发送数据计数器

always @(posedge clk or negedge rst_n) begin if (!rst_n) tx_cnt <= 4'd0;else if (tx_flag) begin if (clk_cnt == BPS_CNT - 1) tx_cnt <= tx_cnt + 1'b1;elsetx_cnt <= tx_cnt; endelse tx_cnt <= 4'd0;

end//根据发送数据计数器来给uart发送端口赋值

always @(posedge clk or negedge rst_n) begin if (!rst_n) uart_txd <= 1'b1; else if (tx_flag)case(tx_cnt)4'd0: uart_txd <= 1'b0; //起始位 4'd1: uart_txd <= tx_data[0]; //数据位最低位4'd2: uart_txd <= tx_data[1];4'd3: uart_txd <= tx_data[2];4'd4: uart_txd <= tx_data[3];4'd5: uart_txd <= tx_data[4];4'd6: uart_txd <= tx_data[5];4'd7: uart_txd <= tx_data[6];4'd8: uart_txd <= tx_data[7]; //数据位最高位4'd9: uart_txd <= 1'b1; //停止位default: ;endcaseelse uart_txd <= 1'b1; //空闲时发送端口为高电平

endendmodule 环回模块将串口接收模块接收到的数据发送给串口发送模块

module uart_loop(//**************输入**************input clk, //系统时钟input rst_n, //系统复位,低电平有效input recv_done, //接收一帧数据完成标志input [7:0] recv_data, //接收的数据input tx_busy, //发送忙状态标志 //**************输出************** output reg send_en, //发送使能信号output reg [7:0] send_data //待发送数据);//************信号定义************

reg recv_done_d0;

reg recv_done_d1;

reg tx_ready;//wire define

wire recv_done_flag;//检测到recv_done上升沿,得到一个时钟周期的脉冲信号,标志着串口接收模块接收到了一帧数据

assign recv_done_flag = (~recv_done_d1) & recv_done_d0;//对发送使能信号recv_done延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) beginrecv_done_d0 <= 1'b0; recv_done_d1 <= 1'b0;end else begin recv_done_d0 <= recv_done; recv_done_d1 <= recv_done_d0; end

end//判断接收完成信号,并在串口发送模块空闲时给出发送使能信号

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begintx_ready <= 1'b0; send_en <= 1'b0;send_data <= 8'd0;end else begin if(recv_done_flag)begintx_ready <= 1'b1 //将tx_ready信号拉高,表示已经准备好了待发送的数据send_en <= 1'b0; //将send_en信号拉低,为接下来产生一个上升沿作准备send_data <= recv_data; //寄存接收到的数据recv_data到send_data中endelse if(tx_ready && (~tx_busy)) begin //检测串口发送模块处于空闲状态tx_ready <= 1'b0; //准备过程结束,等待下一个串口接收数据的到来send_en <= 1'b1; //拉高发送使能信号以启动串口发送模块的发送过程将寄存到send_data中的数据发送出去endend

endendmodule 顶层文件

module uart(//**************输入**************input clk, //外部50M时钟input rst_n, //外部复位信号,低有效input uart_rxd, //UART接收端口//**************输出**************output uart_txd //UART发送端口);//************参数定义************

parameter CLK_FREQ = 50000000; //定义系统时钟频率

parameter UART_BPS = 115200; //定义串口波特率//************信号定义************

wire uart_recv_done; //UART接收完成

wire [7:0] uart_recv_data; //UART接收数据

wire uart_send_en; //UART发送使能

wire [7:0] uart_send_data; //UART发送数据

wire uart_tx_busy; //UART发送忙状态标志//串口接收模块

uart_rx #( .CLK_FREQ (CLK_FREQ), //设置系统时钟频率.UART_BPS (UART_BPS)) //设置串口接收波特率

u_uart_recv( .clk (clk), .rst_n (rst_n),.uart_rxd (uart_rxd),.uart_done (uart_recv_done),.uart_data (uart_recv_data));//串口发送模块

uart_tx #( .CLK_FREQ (CLK_FREQ), //设置系统时钟频率.UART_BPS (UART_BPS)) //设置串口发送波特率

u_uart_send( .clk (clk),.rst_n (rst_n),.uart_en (uart_send_en),.uart_din (uart_send_data),.uart_tx_busy (uart_tx_busy),.uart_txd (uart_txd));//串口环回模块

uart_loop u_uart_loop(.clk (clk), .rst_n (rst_n), .recv_done (uart_recv_done), //接收一帧数据完成标志信号.recv_data (uart_recv_data), //接收的数据.tx_busy (uart_tx_busy), //发送忙状态标志 .send_en (uart_send_en), //发送使能信号.send_data (uart_send_data) //待发送数据);endmodule