转载https://www.mianbaoban.cn/blog/443713-205259.html

本文可以了解什么?

- DDR-DDR4内存模块的差异以及对比;

- 逻辑BANK的概念与定义;

- 芯片的位宽的解释。

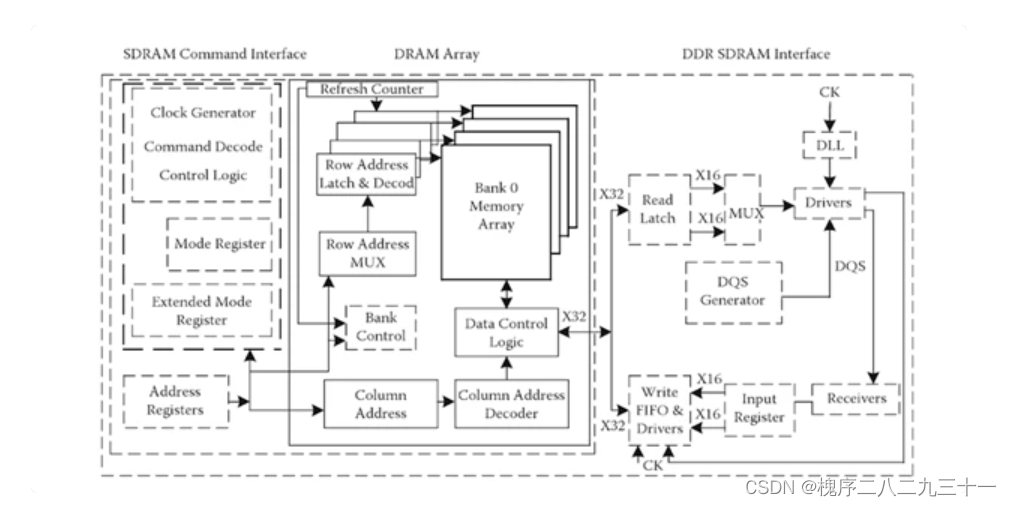

下图是DDR3的PHY IP Core的定义规范。

DDR-DDR4的物理结构差异

首先,我们来对比一下DDR, DDR2, DDR3 SDRAM, and DDR4 SDRAM物理结构上的差别,如下图所示。

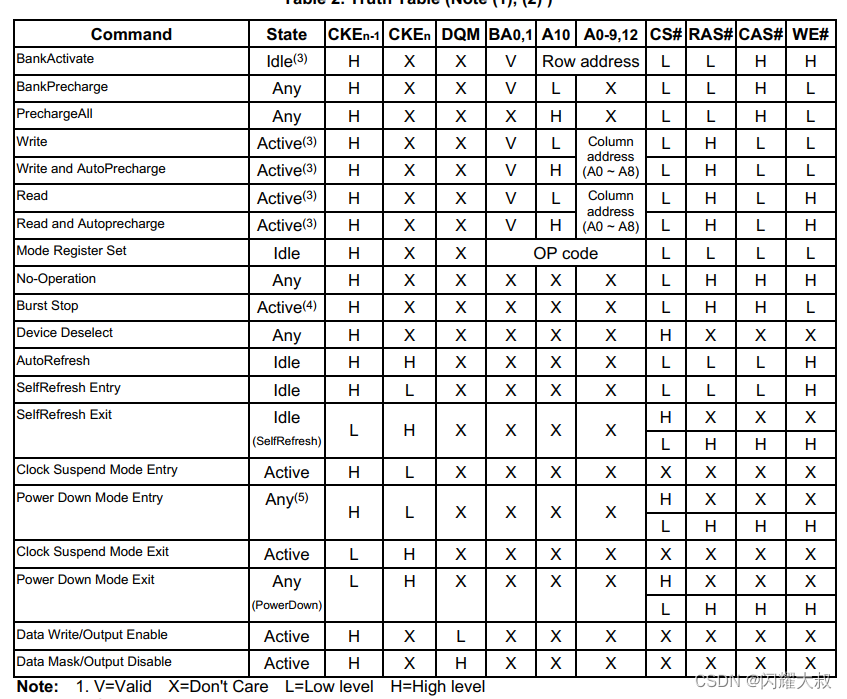

下表是SDRAM-DDR4前后的电压,时钟,速率的对比详图。

SDRAM, DDR1, DDR2, DDR3以及DDR4对比表

逻辑BANK与芯片位宽

我们平时看到的SDRAM都是以模组形式出现,即便是手机或者pad中的内存单元,一般一会是好几颗,为什么要做成这种形式呢?要解释这个问题,首先要接触到两个概念:物理Bank与芯片位宽。

1、逻辑Bank

简单地说,SDRAM的内部是一个存储阵列。由于采用管道式存储(如同排队买票),就很难做到随机访问了。

阵列就如同表格一样,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确定位所需要的单元格,这就是内存芯片寻址的基本原理。对于内存来说,这个单元格可称为存储单元,那么这个表格(存储阵列)我们就称之为逻辑Bank(Logical Bank)。

由于SDRAM的工作原理限制,单一的逻辑Bank将会造成非常严重的寻址冲突,大幅降低内存效率,因此由于技术、成本等各方面原因,不可能一颗芯片只做一个全容量的逻辑Bank。所以架构师在SDRAM内部分割成多个L-Bank,在DDR2的标准中,逻辑Bank的数量是8个。

这样一来,在进行寻址时就要先确定是哪个逻辑Bank,然后再在这个选定的逻辑Bank中选择相应的行与列定位内存单元进行寻址。可见对内存的访问,一次只能是一个逻辑Bank工作,而每次交换的数据就是逻辑Bank存储阵列中一个“存储单元”的容量。

2、芯片位宽

传统内存系统为了保证CPU的正常工作,必须一次传输完CPU在一个传输周期内所需要的数据。而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。当时控制内存与CPU之间数据交换的芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,内存的位宽需要与CPU对应,才能正常运行。

SDRAM内存系统必须要组成一个物理Bank的位宽,才能使CPU正常工作,那么这个物理Bank位宽怎么得到呢?这就涉及到了内存芯片的结构。

每个内存芯片也有自己的位宽,即每个传输周期能提供的数据量。理论上,完全可以做出一个位宽为64bit的芯片来满足物理Bank的需要,但这对技术的要求很高,在成本和实用性方面也都处于劣势。所以芯片的位宽一般都较小。对于台式机市场所用的SDRAM芯片位宽最高也就是16bit,常见的则是8bit。这样,为了组成物理Bank所需的位宽,就需要多颗芯片并联工作。对于16bit芯片,需要4颗(4×16bit=64bit)。对于8bit芯片,则就需要8颗了。

这样大概可以说清楚芯片位宽、芯片数量与物理Bank的关系。物理Bank其实就是一组内存芯片的集合,这个集合的容量不限,但这个集合的总位宽必须与CPU数据位宽相符。