文章来自International Conference on Architectural Support for Programming Languages and Operating Systems,ASPLOS,2023

0.所有作者及单位

- Hasan Al Maruf,Mosharaf Chowdhury,密歇根大学

- Hao Wang,Niket Agarwal,Pallab Bhattacharya,英伟达

- Abhishek Dhanotia,Johannes Weiner,Chris Petersen,Shobhit Kanaujia,Prakash Chauhan,Meta公司(2021年10月28日,创始人马克・扎克伯格宣布公司由Facebook更名为Meta)

1. Background

超大规模应用对内存的需求不断增加,导致内存成为数据中心总体支出的很大一部分。 CXL 等相干接口的出现实现了主存储器扩展,并为该问题提供了有效的解决方案。在此类系统中,主存储器可以构成具有不同特性的不同存储器技术。然而,如果没有有效的内存管理,此类系统可能会显着降低性能。

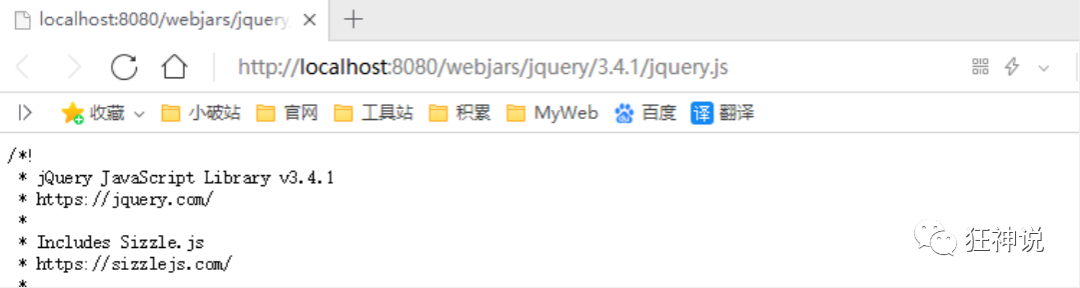

- CXL 是一种基于 PCI Express (PCIe) 接口的开放式、工业界支持的互连接口。

- 它支持主机处理器和设备(例如加速器、内存缓冲区、智能 I/O 设备等)之间的高速、低延迟通信。

- CXL 在同一物理地址空间中提供字节可寻址内存,并允许使用标准内存分配 API 进行透明内存分配。

- CXL-Memory 访问延迟也与 NUMA