文章目录

- 概要

- 网络结构

- 一维卷积介绍(科普性质)

- FPGA架构

- FPGA端口定义

- 操作步骤

- 结果演示

- 总结

概要

本文介绍一种基于FPGA的1维卷积神经网络算法加速实现的方案,其中为了进一步提升运算速度,除了第一层卷积采用的是普通卷积运算(CONV),其余卷积层和池化层采用的是二值化运算,即二值化的卷积与池化。

运算过程包含了卷积层、池化层、批标准化层、全局池化、二值化卷积、全连接层、激活函数层,均采用RTL级代码实现,即全部采用Verilog HDL代码实现,兼容Intel Altera FPGA 与 AMD Xilinx FPGA,便于移植。

网络结构

具体网络结构如下表所示:

此项目先用python代码实现训练和推理过程,获得权重,然后再将推理过程移植到FPGA上进行。

python运算过程一共分为17层,在FPGA实现时将其划分为7个大层,运算过程包含了卷积层、池化层、批标准化层、全局池化、二值化卷积、全连接层、激活函数层,均采用RTL级代码实现,即全部采用Verilog HDL代码实现,兼容Intel Altera FPGA 与 AMD Xilinx FPGA。

一维卷积介绍(科普性质)

1D-CNN是指一维卷积神经网络(1D Convolutional Neural Network),它是卷积神经网络的一种变体。1D-CNN主要用于处理一维序列数据,比如音频、文本等。与传统的全连接神经网络相比,1D-CNN可以更好地处理序列数据中的局部关系,因此在语音识别、自然语言处理、时间序列预测等任务中表现较好。

1D-CNN使用卷积层来提取序列数据中的特征。卷积层通过滑动一个固定大小的窗口在输入数据上进行卷积操作,提取窗口内的特征,然后将这些特征映射到下一层。与二维卷积神经网络(2D-CNN)类似,1D-CNN还可以使用池化层来减少特征映射的维度和计算量。

1D-CNN通常由多个卷积层和池化层交替组成,最后使用全连接层将提取的特征映射到输出。在训练过程中,1D-CNN使用反向传播算法来更新模型参数,以最小化损失函数。

1D-CNN主要由以下几部分组成:

输入层:接收一维序列数据作为模型的输入。

卷积层:使用一系列可训练的卷积核在输入数据上滑动并提取特征。卷积操作能够有效地提取局部信息,从而捕捉输入序列的局部模式。

批标准化(Batch Normalization):用于加速网络收敛和提高模型的鲁棒性,使得模型更易于训练。

激活函数:对卷积层的输出进行非线性变换,增强模型的表达能力。

池化层:通过对卷积层输出进行降维,减少计算量,同时提高模型的鲁棒性和泛化能力。

全连接层:将池化层的输出映射到模型的输出,通常用于分类、回归等任务。

在使用1D-CNN时,我们通常需要设置一些超参数,比如卷积核的大小、卷积层的个数、池化操作的方式、激活函数的选择等等。这些超参数的选择会影响模型的性能和效率,需要通过实验进行调整。

1D-CNN在处理时间序列数据方面表现良好,比如音频信号处理、文本分类、情感分析、股票价格预测等任务。它能够自动提取数据中的重要特征,从而减少人工特征提取的工作量,同时具有较好的泛化性能。

本节内容转载自:机器朗读 https://www.bilibili.com/read/cv23110682?from=search&spm_id_from=333.337.0.0 出处:bilibili

FPGA架构

包含按键消抖、串口接收、串口发送、卷积算法模块

FPGA端口定义

module fpga_top(input sys_clk, //外部50M时钟input sys_rst_n, //外部复位信号,低有效input [1:0] key , //按键,低有效output [1:0] led , //LED,低有效-未使用input uart_rxd, //UART接收端口output uart_txd //UART发送端口);操作步骤

- 1.加载程序,打开串口,波特率:9600

- 2.按下key0,将串口RAM地址清零;

- 3.将准备好输入数据通过串口下发给FPGA(以16进制格式发送)

- 4.按下key1,启动卷积推理运算;

- 5.运算完成后,结果将以串口形式返回

- 6.串口接收端:设置为ASCII码格式接收,将返回最大值对应的索引值。

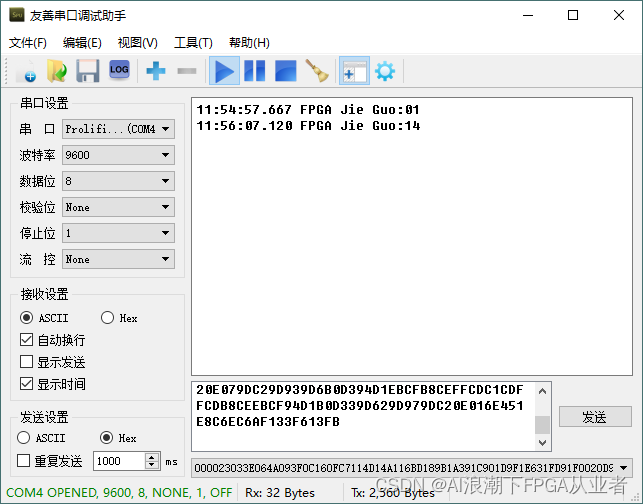

结果演示

提示:这里可以添加总结

总结

以上即为基于FPGA的1D-CNN或BNN的大致介绍,该项目非常便于移植到各种不同应用场景,欢迎交流沟通,本项目在Altera FPGA和Xilinx FPGA开发板上均通过上板验证。如需代码,请私信获取。

另外,本人专业从事图像处理算法、AI深度学习算法、各种神经网络算法的FPGA加速实现多年,可基于Matlab、Python的算法代码进行FPGA加速实现,如需合作,欢迎私信沟通。