文章目录

- 一、HDMI 基本介绍

- 二、TMDS基本介绍

- 三、传输流程

- 四、传输周期

- 五、Data Island Packet结构

- 六、Audio Clock

- 七、HotPlug

- 八、HDMI Sink

- 九、HDMI版权内容保护之HDCP

- 十、模块编码

一、HDMI 基本介绍

对于初学者先了解VGA,再来看HDMI会更容易理解,有关VGA原理在我的博客中有详细说明。FPGA-VGA显示

HDMI,高清晰度多媒体接口(High Definition Multimedia Interface)是标准的数字化视频/音频接口技术,可用于机顶盒、DVD播放机、个人电脑与电视机。HDMI可以同时传送音频和影音信号,能高品质地传输未经压缩的高清视频和多声道音频数据,最高数据传输速度为 50Gbps 左右。

HDMI 向下兼容 DVI,但是 DVI(数字视频接口)只能用来传输视频,而不能同时传输音频,这是两者最主要的差别。此外,DVI 接口的尺寸明显大于 HDMI 接口,如下图所示

VGA、DVI、HDMI相互转换的说明:

1、VGA和DVI互转:模拟信号和数字信号的转换,视频信号损失,造成失真。最好不要这样转换。

2、DVI和HDMI互转:都是数字信号,转换不会发生失真。可以转换。但是从HDMI转换成DVI时会自动舍去音频信号。

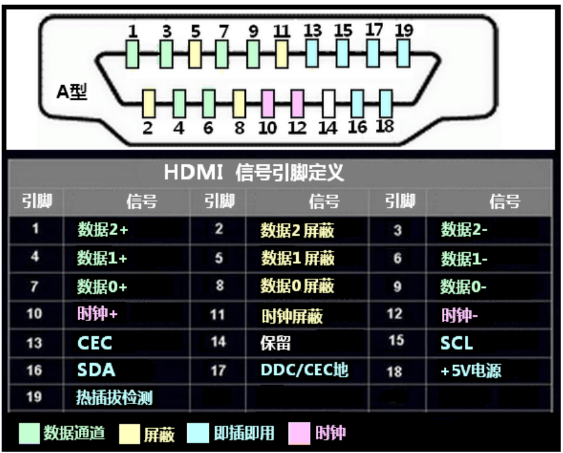

HDMI引脚:

HDMI有A,B,C,D,E五种引脚类型,目前市面中比较常见的就是Type A

- 1-9 都是TMDS数据传输实际上用到的引脚,分为0,1,2三组

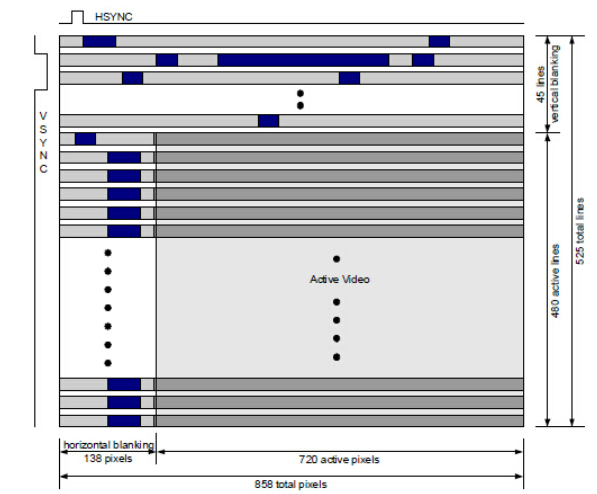

- 10-12 为TMDS时钟信号,如当前Video Timing为480p@60Hz(Htotal:800,Vtotal:525),则TMDS clock = 800x525x60 = 25.2MHz。TMDS clock就像是对像素的打包,一个clock分别在三个Channel传输一个像素的R、G、B(8bit)信号。

- 13 为CEC(consumer electronic control)类似一种扩展的HDMI功能,供厂家自己定制HDMI消息,(比如说你有一台sony的DVD与TV,两者用HDMI线接上,如果你用TV的遥控器可以控制DVD,另DVD执行某种功能,那么该功能的命令信号就是通过TV与DVD间的CEC引脚传输的)

- 14 为保留引脚,未使用(或者也可以为CEC提供多一个引脚)

- 15-16 为I2C引脚,用于DDC(Display Data Channel,主要用于EDID与HDCP的传输)传输。在HDMI的流程中,DDC通信几乎是最先做的(前有Hotplug),因为HDMI的主从两个设备需要通过DDC来获得他们对方设备的EDID,从而得到各种信息,并且通过比较timming以确定以后送出来的timming为最合适的

- 17 为接地引脚

- 18 为5v的AC引脚

- 19 为Hotplug(热拔插)引脚(用于监测HDMI设备有没有存在,如果存在(Hotplug为high)那么可以通过DDC去读EDID),HDMI有规定在HDMI 5vAC断电时source device可以读reciever device的EDID,也就是需要Hotplug为High。其中有两种Hotplug相关的情况会导致HDMI被识别为DVI:

1. Hotplug为High,不过EDID并没有准备好,那么信号源设备会由于无法读到EDID而认为接收设备为DVI,这样会导致HDMI有图像无声的问题。

2. Hotplug为Low,也会导致信号源无法读到EDID而认为接收设备为DVI,从而导致HDMI有图无声

3. 在TV这种有多个HDMI通道的情况下,有时会在多个HDMI通道进行切换,切换后HDMI通道应当先初始化,即先把Hotplug拉低,通知HDMI source device之前所用的EDID已经改变,需要重新读取,那么source device在Hotplug被拉高的时候会去读取新的EDID,但是拉低这个过程至少需要100ms,否则source device有可能不会去读取新的EDID,从而输出DVI信号

下图为 HDMI 链路的框架图:

二、TMDS基本介绍

过渡调制差分信号,也被称为最小化传输差分信号,是指通过异或及异或非等逻辑算法将原始信号数据转换成 10 位,前 8 位数据由原始信号经运算后获得,第9位指示运算的方式,第 10 位用来对应直流平衡(DC-balanced,就是指在编码过程中保证信道中直流偏移为零,电平转化实现不同逻辑接口间的匹配),转换后的数据以差分传动方式传送。

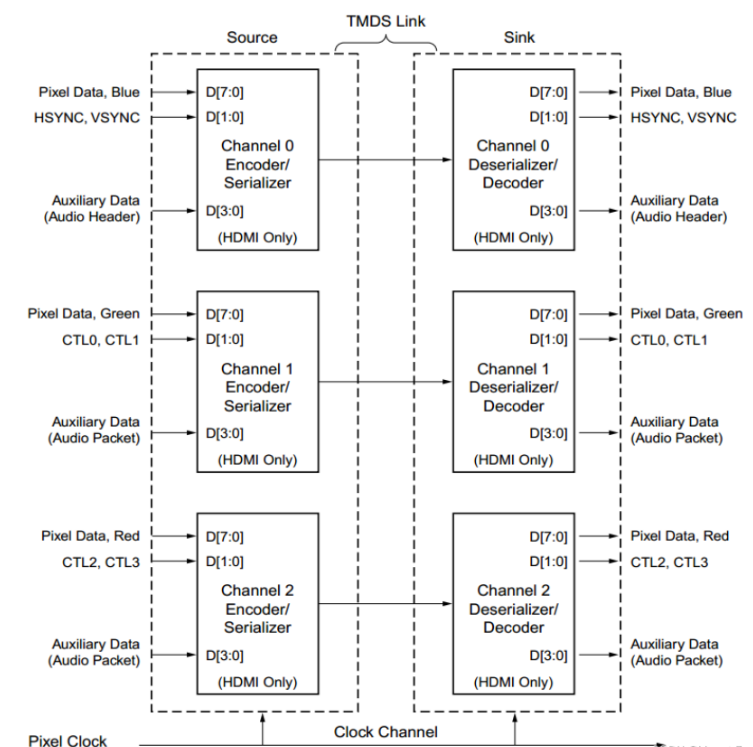

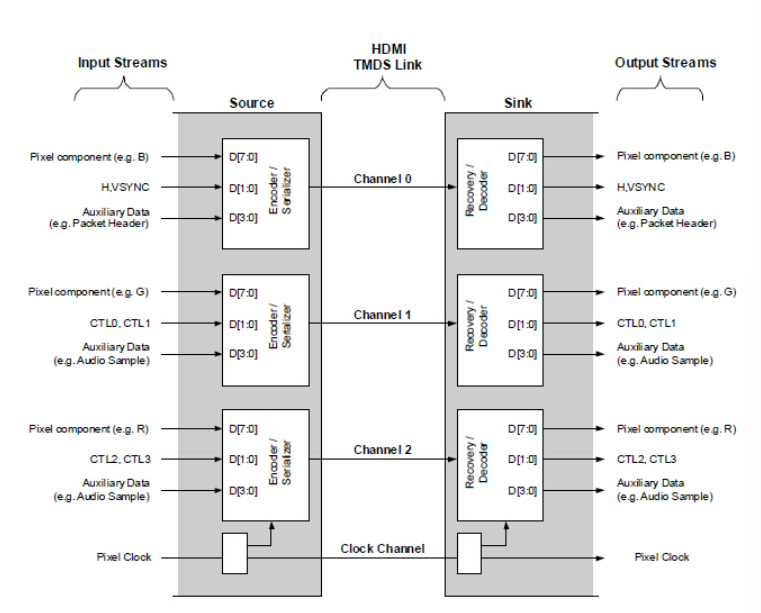

TMDS 的链路要有两部分:source 和 sink 端,source 端为传输数据的起始端,sink 端为传输数据的目的端。同时链路由四条通道组成,分别为蓝色通道、、绿色通道、红色通道和时钟通道。

蓝色通道

蓝色通道包含8位的蓝色数据通道,两位的行同步和场同步信号,以及四位的音频信号。

绿色通道

绿色通道包含8位的绿色数据通道,两位的控制信号,以及四位的音频信号。

红色通道

红色通道包含8位的红色数据通道,两位的控制信号,以及四位的音频信号。

时钟通道

为了使source端和sink端的数据保持在同一个pixel clock下,便于数据的稳定发送和接收。

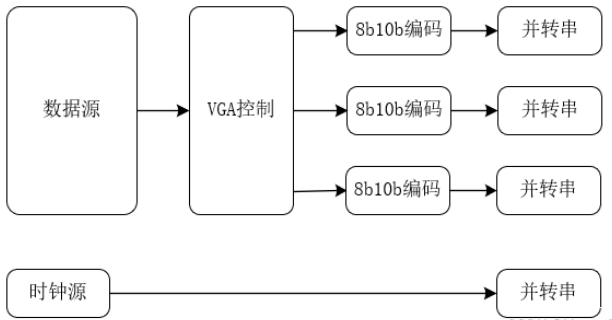

在 source 端:每个通道的中还包含 Encoder 和 Serializer 模块,即编码模块和并转串模块,对应到 sink 端为解码模块和串转并模块。

在编码阶段:编码器将视频源中的像素数据、HDMI的音频/附件数据,以及行、场同步信号分别编码成10位的字符流。

在并串转换阶段将上述的10位字符流转换成串行数据流,并将其从三个差分输出通道发送出去。这个10:1的并转串过程所产生的串行速率是实际像素时钟速率的10倍。但是在并转串中采用的为DDR即双沿采样,因此时钟频率可以减小为原来的一半,也就是像素时钟的 5 倍。

三、传输流程

HDMI TMDS传输的数据类型有三种(加上Hsync与Vsync就算4种):

- Preamble(控制信息),主要用于控制接下来传输的数据是Data Island或者Video Data

- Data Island(数据包),各种类型的包信息,包括音频数据包,图像信息包等

- Video Data (视频信息),视频像素数据,HDMI可以传输RGB与YUV两种格式的像素数据

- Hsync与Vsync

如果是8bit的数据进入TMDS编码器,得到抗干扰性强的10bit TMDS信号,然后再进行串行化输出;在接收端收到串行的HDMI信号后,进行信号复原,得到10bit的TMDS信号,最后用TMDS解码器解码得到原来的8bit数据。

总体传输流程如下:

| 传输对象 | bit | 说明 |

|---|---|---|

| Video Data | 24bit | Channel0[7:0]传输B,Channel1[7:0]传输G,Channel2[7:0]传输R |

| Data Island | 10bit | Channel0[3:2]用于传输Data Island Header(包头),Channel1[3:0]与Channel2[3:0]用于传输Data Island Content(包内数据) |

| Preamble | 4bit | Channel1[1:0]与Channel2[1:0]分别为CTL0,CTL1,CTL2,CTL3,用于判断接下来输入的是Video Data或者Data Island |

| Hsync与VSync | 2bit | Channel0[0]为Hsync,Channel0[1]为Vsync |

| CTL0 | CTL1 | CTL2 | CTL3 | Data Period Yype |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | Video Data Period |

| 1 | 0 | 1 | 0 | Data Island Period |

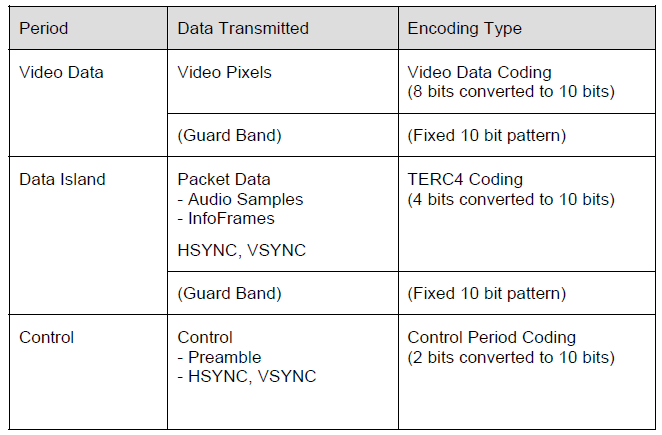

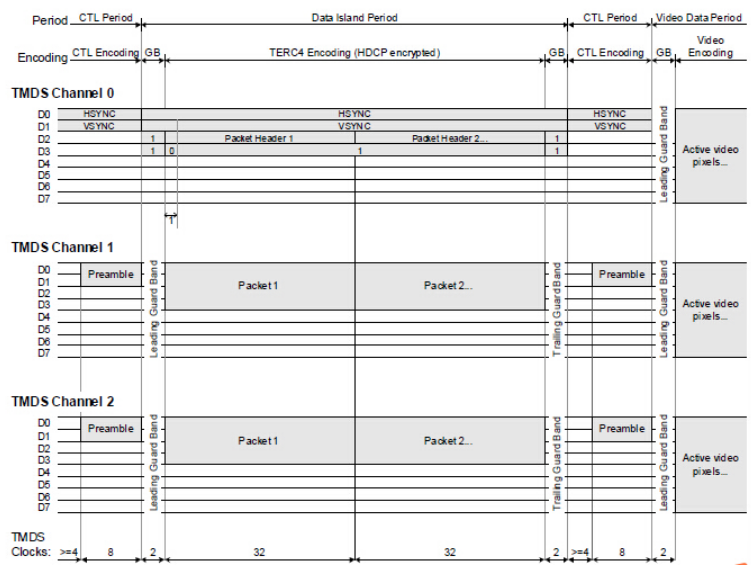

四、传输周期

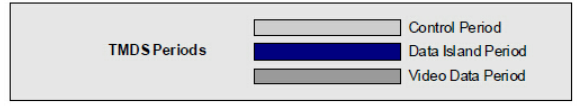

HDMI的TMDS数据传输可以分为三个传输周期:

- Control Period期间会传输Hsync,Vsync,并且在该时期的最后阶段会传输Preamble

- Data Island Period期间会传输Data Island(数据包),也会有Hsync与Vsync

- Video Data Period期间会传输Video Data(视频像素数据)

一帧总体周期:

三个传输周期的过渡如下:

| 左边 | 中间 | 右边 |

|---|---|---|

| Control Period | Data Island Period | Data Island Period |

| 传输有Hsync,Vsync与Preamble | 传输有Hsync,Vsync,以及两个Packet Header与Packet(每32个clock 一个packet);另外Data Island的两端会用Guard Band保护并隔开Data Island的数据,因为这个阶段传输的数据大多是非常重要的,比如其中就有图像分辨率,决定后面的Video Data数据的显示方式 | 传输有Hsync,Vsync,以及两个Packet Header与Packet(每32个clock 一个packet);另外Data Island的两端会用Guard Band保护并隔开Data Island的数据,因为这个阶段传输的数据大多是非常重要的,比如其中就有图像分辨率,决定后面的Video Data数据的显示方式 |

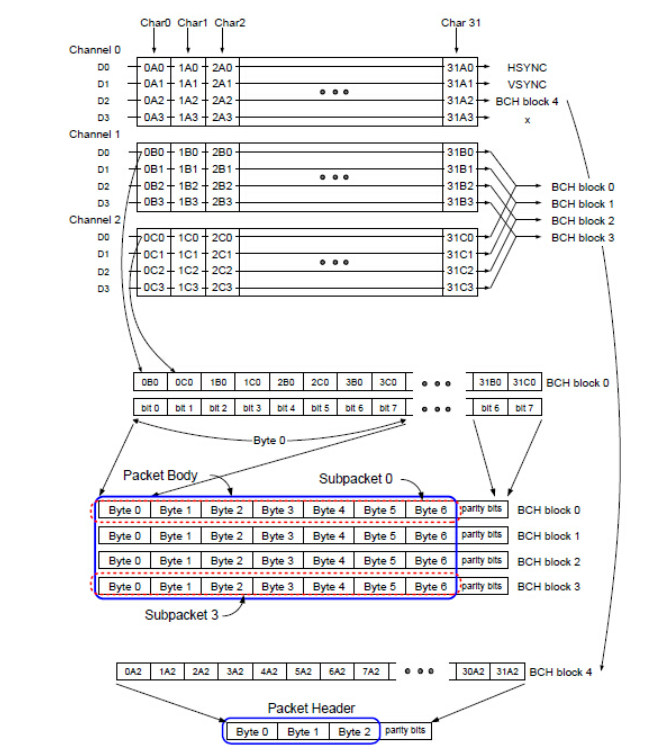

五、Data Island Packet结构

所有Data Island Packet都以32个时钟脉冲为一个周期,也就是说每32 clk传输一个包。

说明:

| 包 | bolck | 传输通道 | 说明 |

|---|---|---|---|

| 包头(Packet Header | BCH block 4 | Channel0[2] | 前三个byte为包头,最后一byte为校验码 |

| 包体(Packet Body | BCH block 0,1,2,3 | Channel1,Channel2 | 共8根线传输,共有28byte包体与4byte的校验码 |

Parity Bits校验码是用于检验HDMI Cable传输过程中是否发生了错误,如果该Packet在HDMI接收端校验错误,如果只有一个bit的错误,那么可以修正,超过1bit的错误会被判别为无效Packet(由于HDMI是一直在发送数据因此无法重发错误Packet)

所以在接收端,在解完包之后,需要取出各个BCH block的Parity bit,进行Calibration(校验)

六、Audio Clock

七、HotPlug

八、HDMI Sink

九、HDMI版权内容保护之HDCP

十、模块编码

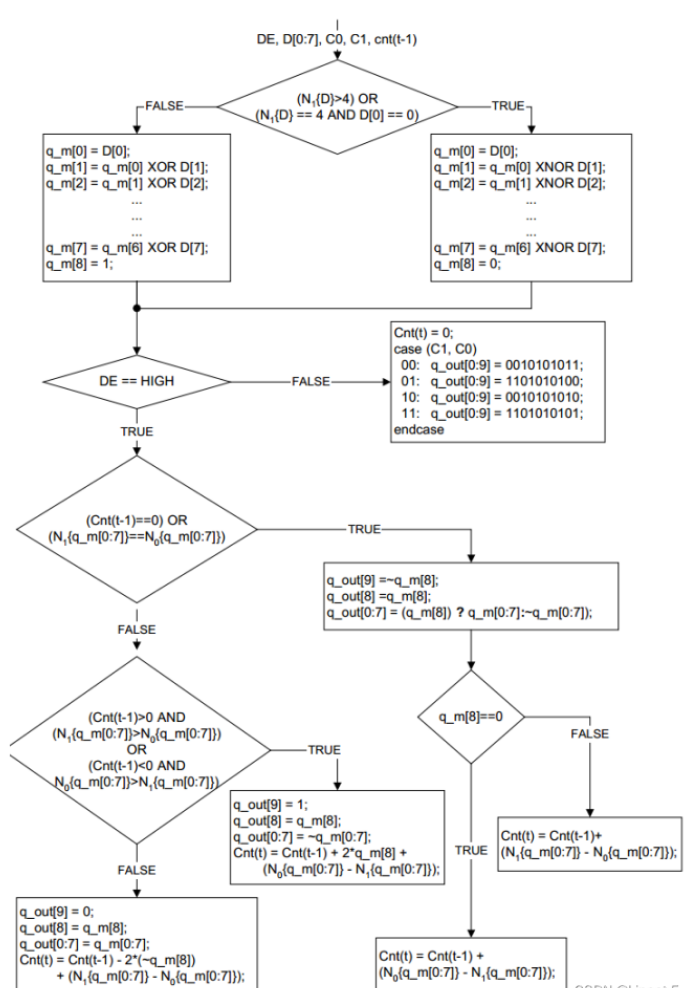

每一个数据通道都通过编码算法,将 8 位的视、音频数据转换成最小化传输、直流平衡的 10 位数据。这使得数据的传输和恢复更加可靠。最小化传输差分信号是通过异或及异或非等逻辑算法将原始 8位信号数据转换成 10 位,前 8 为数据由原始信号经运算后获得,第 9 位指示运算的方式,第 10位用来对应直流平衡。这种算法可以减小传输信号过程的上冲和下冲,什么是上冲和下冲呢,顾名思义上冲就是由0转变为1,下冲就是由1转变为0,如果频繁的上下冲就会导致信号传输不稳定,而DC平衡使信号对传输线的电磁干扰减少,DC平衡指的是在码流中0和1的个数相当。总结来说,信号频繁的0、1变化和0和1数量不均衡都会影响信号的质量,编码的目的就在于此。

参考 HDMI介绍与流程