1 概述

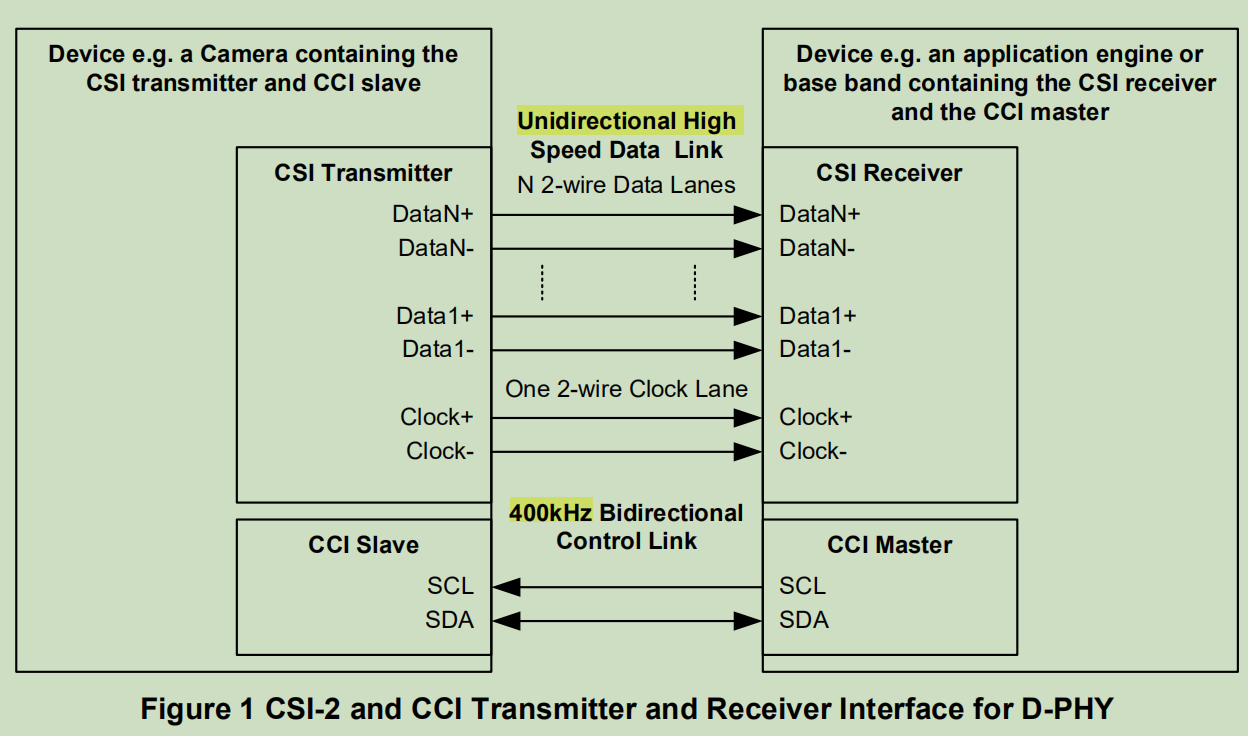

如上图:

- CSI-2包括若干单向Data lane,用于传输图像数据

- clock lane是必须的,data lane 1-4个

- CCI,camera control interface,用于配置

- 物理层详见D-PHY,lane配置为:LP也需要,进出HS模式需要LP control mode若干操作

The minimum D-PHY physical layer requirement for a CSI-2 transmitter is

• Data Lane Module: Unidirectional master, HS-TX, LP-TX and a CIL-MFEN function

• Clock Lane Module: Unidirectional master, HS-TX, LP-TX and a CIL-MCNN function

The minimum D-PHY physical layer requirement for a CSI-2 receiver is

• Data Lane Module: Unidirectional slave, HS-RX, LP-RX, and a CIL-SFEN function

• Clock Lane Module: Unidirectional slave, HS-RX, LP-RX, and a CIL-SCNN function

2 CCI

- CCI,camera control interface,是I2C协议的子集,与I2C基本一致

- 支持多种位宽的寄存器, 由于I2C是字节流读写,多Bytes寄存器的原子操作要由硬件实现来保证。例如32bit reg, write时,写完最后一个Byte,才会真正写入寄存器;read时,4Bytes的值是读第一个Byte时的值

- MS Byte at lowest address

8-bit – generic setup registers

16-bit – parameters like line-length, frame-length and exposure values

32-bit – high precision setup values

64-bit – for needs of future sensors

3 CSI-2协议层总览

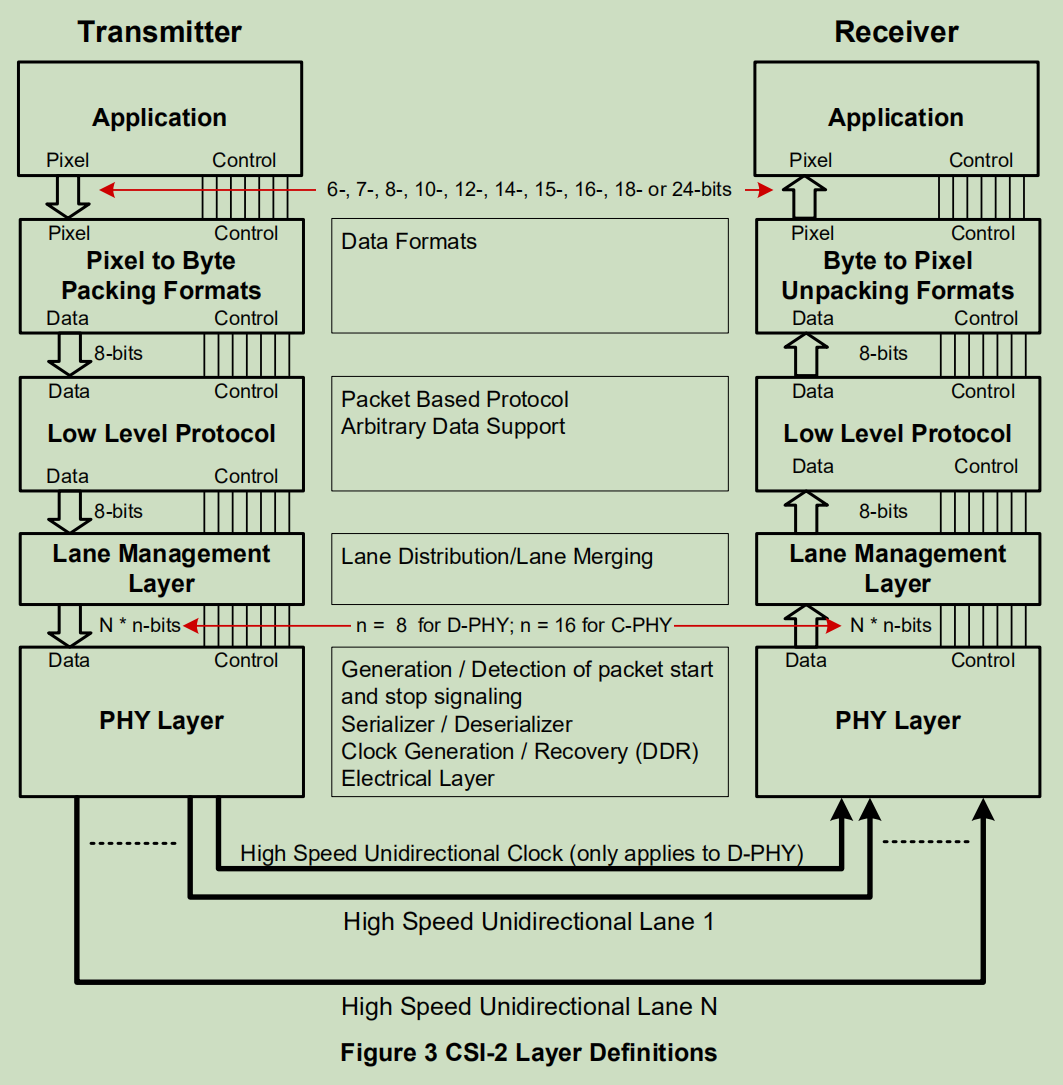

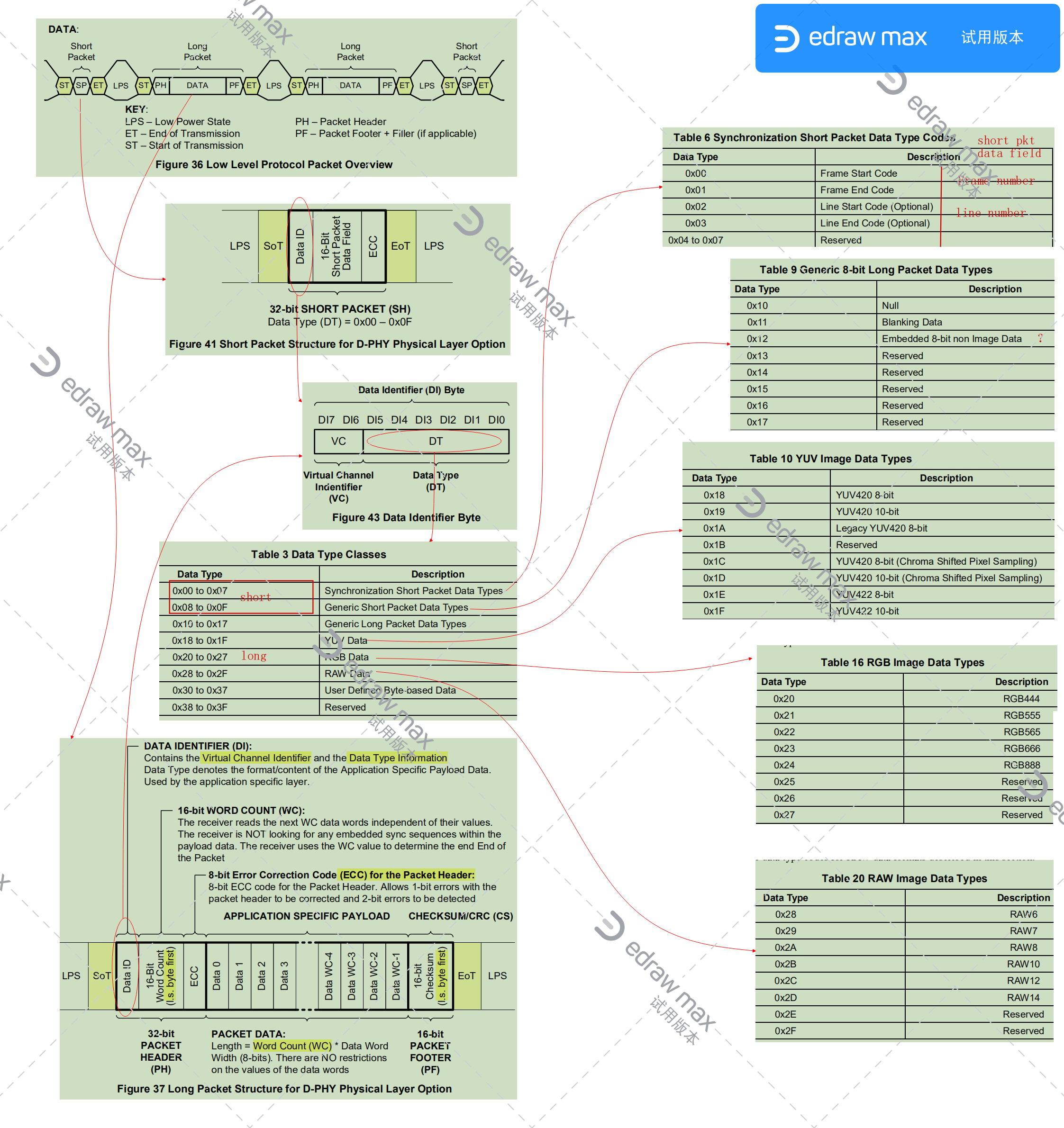

CSI-2的Protocol layer分为三层:

- Pixel/Byte Packing/Unpacking Layer, 理解APP层不同Data formats,即不同格式的图像信息,例如YUV、RGB、RAW等

- Low Level Protocol, LLP,组织串行数据

- Lane Distribution/Lane Merging, TX时串行数据分发到多个lane, RX从多个lane获取数据并merge成串行数据

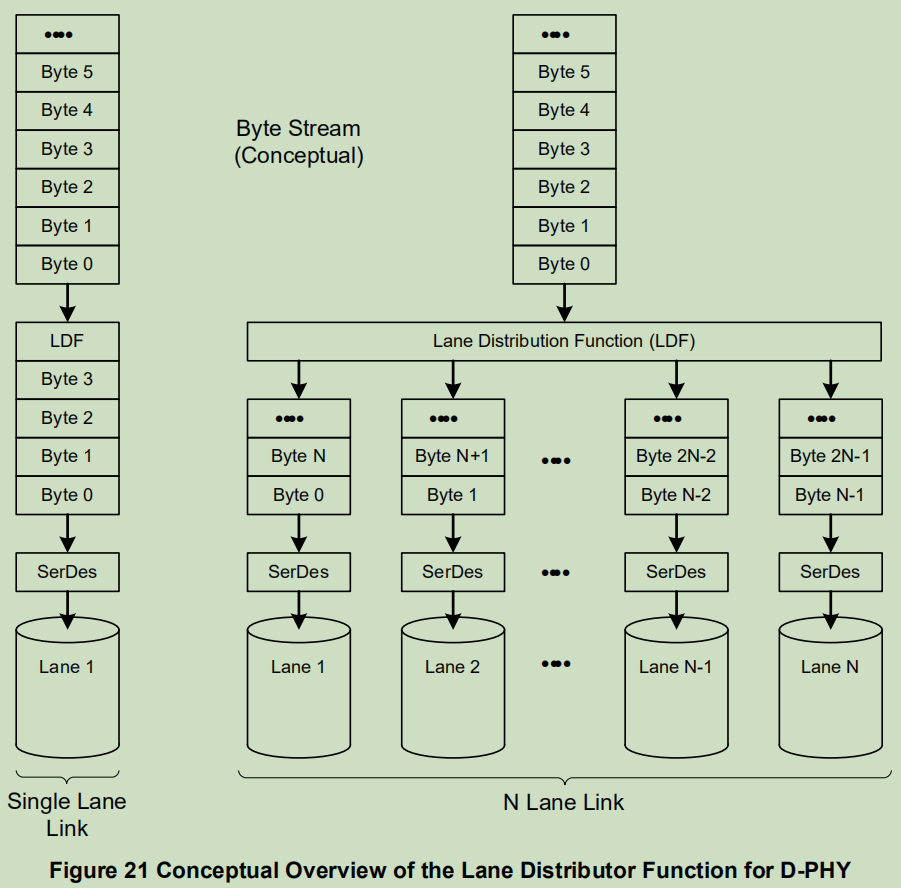

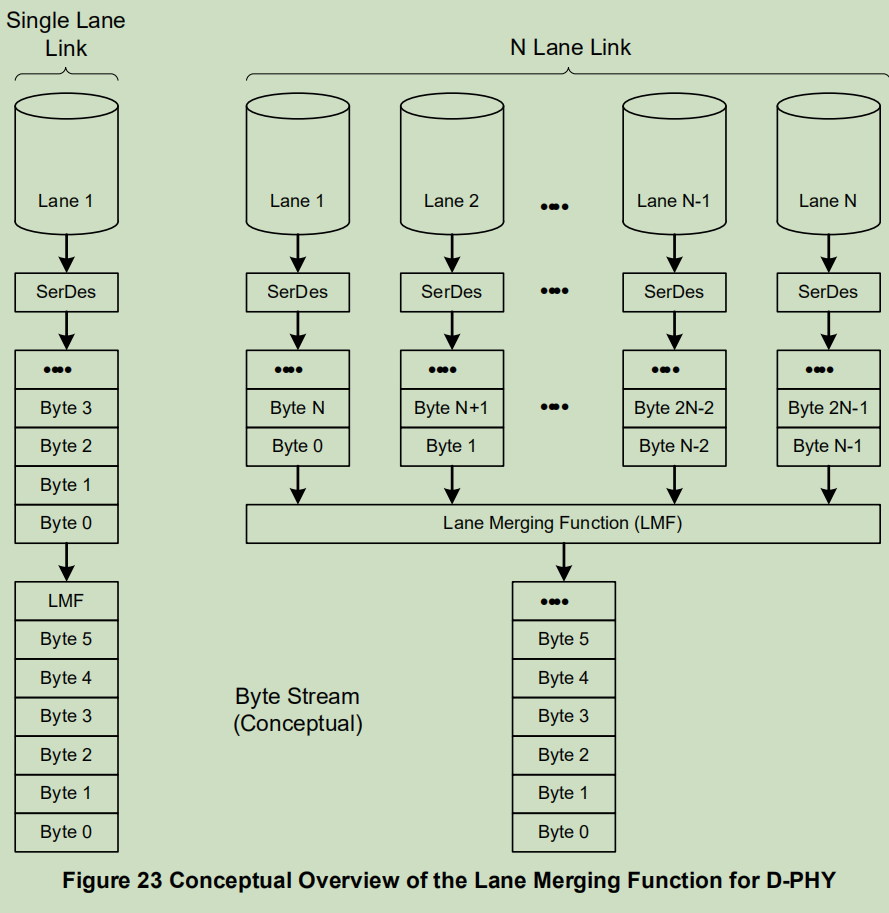

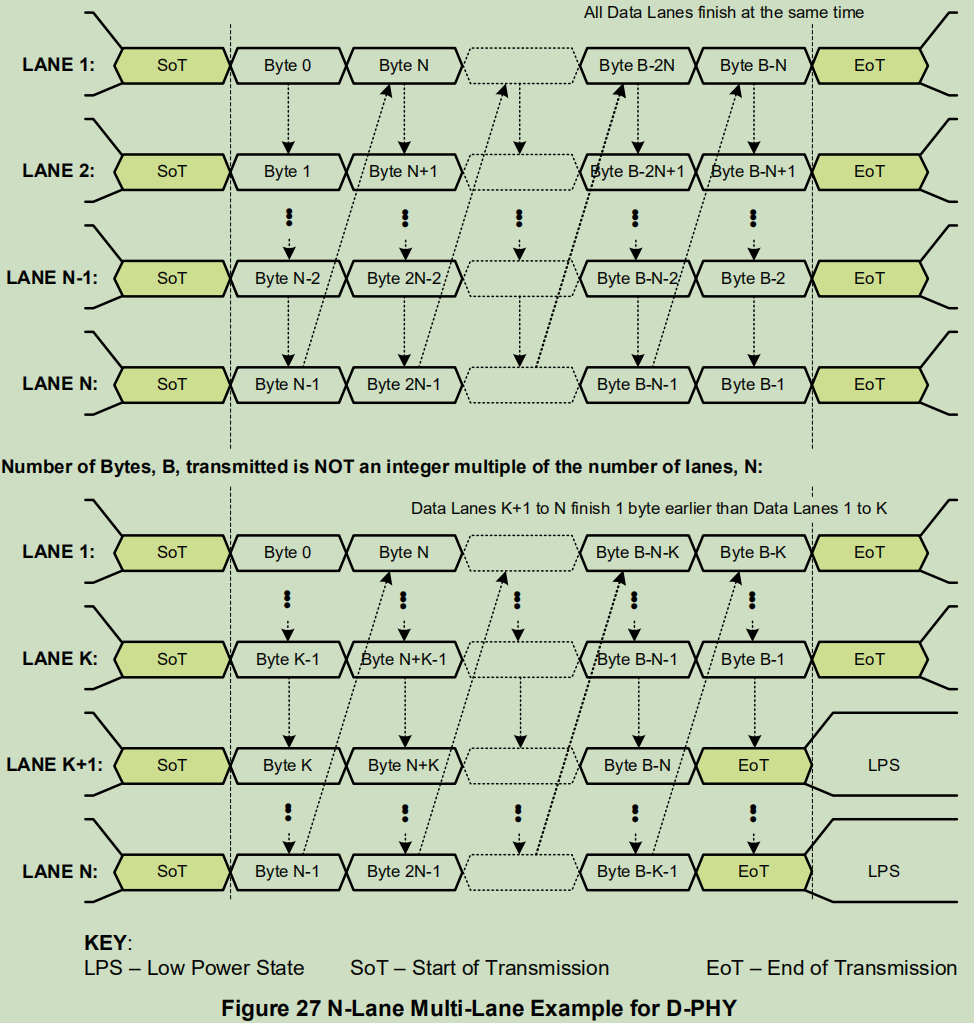

4 Lane Distribution/Lane Merging

- dispatch和merge时,以Bytes为单位,不是bit

- 不同lane传输长度可以不同,因为Bytes数不一定是lane数的整数倍

5 Low Level Protocol

6 Pixel/Byte Packing/Unpacking Layer

主要描述YUV/RGB/RAW等格式的存储,详见specification.

7 参考

Specification for CSI-2, V1.3