文章目录

- SIMD

- 指令集架构类型

- CISC的产生、发展和现状

- RISC的产生、发展和现状

- IA-64(EPIC)产生、发展和现状

- RISC与 IA-64(EPIC)相比

- 指令集介绍

- 一、X86

- 二、X64

- 三、ARM

- 四、SSE指令集

- 五、SSE2指令集

- 六、SSE3指令集

- 七、SSE4指令集

- 八、3D Now!扩展指令集

- 九、EM64T指令集

- 十、RISC指令集

- 十一、3DNow!+指令集

- 十二、AVX指令集

- Intel指令手册地址:https://software.intel.com/sites/landingpage/IntrinsicsGuide/

之前在《游戏引擎架构》中SIMD类型部分不清楚。

这次抽空补充学习一下。

SIMD

先来段代码对比:

代码功能为

r e s = ( a 2 + b 2 ) res = \sqrt{(a^2 + b^2)} res=(a2+b2)

* 其中:a,b,res均为数组。

void normal(float data1[], float data2[], int len, float out[])

{int i;for (i = 0; i < len; i++){out[i] = sqrt(data1[i]* data1[i] + data2[i] * data2[i]);}

}

void simd(float *data1, float *data2, int len, float out[])

{assert(len % 4 == 0);__m128 *a,*b,*res,t1,t2,t3;// = _mm256_set_ps(1, 1, 1, 1, 1, 1, 1, 1);int i,tlen = len/4;a = (__m128*)data1;b = (__m128*)data2;res = (__m128*)out;for (i = 0; i < tlen; i++){t1 = _mm_mul_ps(*a, *a);t2 = _mm_mul_ps(*b, *b);t3 = _mm_add_ps(t1, t2);*res = _mm_sqrt_ps(t3);a++;b++;res++;}

}

void simd256(float* data1, float* data2, int len, float out[])

{assert(len % 8 == 0);__m256* a, * b, * res, t1, t2, t3;// = _mm256_set_ps(1, 1, 1, 1, 1, 1, 1, 1);int i, tlen = len / 8;a = (__m256*)data1;b = (__m256*)data2;res = (__m256*)out;for (i = 0; i < tlen; i++){t1 = _mm256_mul_ps(*a, *a);t2 = _mm256_mul_ps(*b, *b);t3 = _mm256_add_ps(t1, t2);*res = _mm256_sqrt_ps(t3);a++;b++;res++;}

}

问题规模:16*10000000

| 函数 | 运行时间(s) |

|---|---|

| normal | 1.414000 |

| simd | 0.357000 |

| simd256 | 0.119000 |

本来我在这里想用__m512,结果报错:Illegal Instruction。原因为缺少AVX512指令。桌面端缺少AVX512指令,只有服务器上才有。

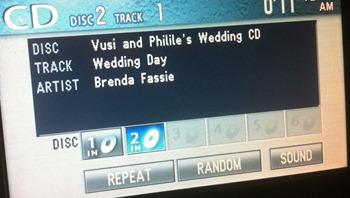

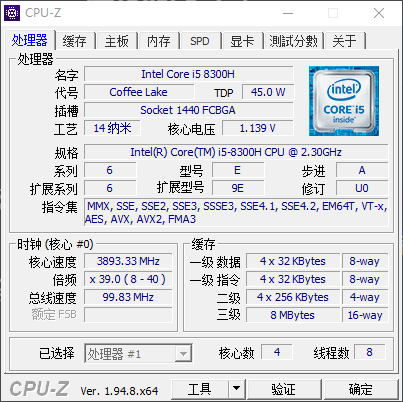

这里使用CPUZ软件检测,笔者电脑上支持的指令集为MMX,SSE,SSE2,SSE3,SSE3,SSE4.1,SSE4.2,EM64T,VT-X,AES,AVX,AVX2,FMA3

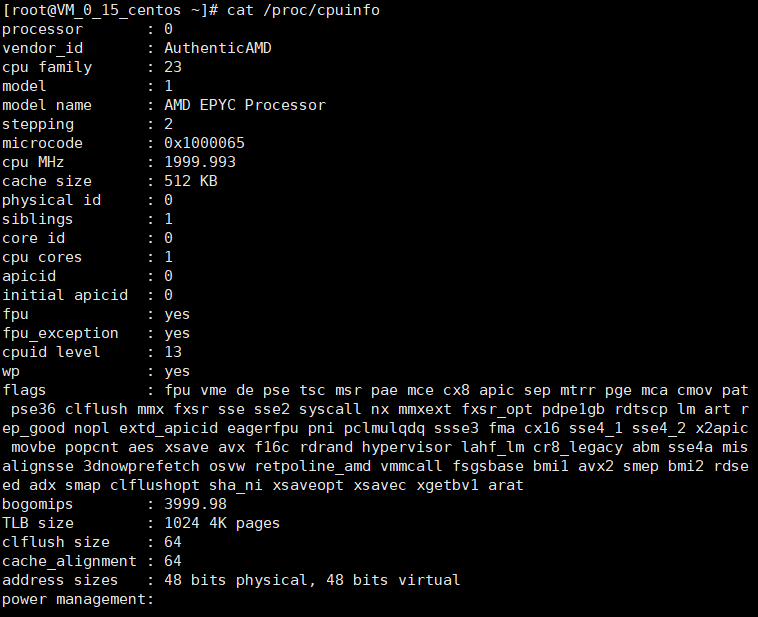

CentOS输入cat /proc/cpuinfo即可查看CPU信息。以下是我腾讯云服务器信息。

SIMD(single-instruction, multiple-data)是一种使用单道指令处理多道数据流的CPU执行模式,即在一个CPU指令执行周期内用一道指令完成处理多个数据的操作。

支持指令fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush mmx fxsr sse sse2 syscall nx mmxext fxsr_opt pdpe1gb rdtscp lm art rep_good nopl extd_apicid eagerfpu pni pclmulqdq ssse3 fma cx16 sse4_1 sse4_2 x2apic movbe popcnt aes xsave avx f16c rdrand hypervisor lahf_lm cr8_legacy abm sse4a misalignsse 3dnowprefetch osvw retpoline_amd vmmcall fsgsbase bmi1 avx2 smep bmi2 rdseed adx smap clflushopt sha_ni xsaveopt xsavec xgetbv1 arat

指令集架构类型

CISC的产生、发展和现状

一开始,计算机的指令系统只有很少一些基本指令,而其他的复杂指令全靠软件编译时通过简单指令的组合来实现。

举个最简单的例子:一个a乘以b的操作就 可以转换为a个b相加来做,这样就用不着乘法指令了。当然,最早的指令系统就已经有乘法指令了,这是为什么呢?因为用硬件实现乘法比加法组合来得快得多。

由于那时的计算机部件相当昂贵,而且速度很慢,为了提高速度,越来越多的复杂指令被加入了指令系统中。

但是,很快又有一个问题:一个指令系统的指令数是受指令操作码的位数所限制的,如果操作码为8位,那么指令数最多为256条(2的8次方)。

那么怎么办呢?指令的宽度是很难增加的,聪明的设计师们又想出了一种方案:操作码扩展。前面说过,操作码的后面跟的是地址码,而有些指令是用不着地址码或只用少量的地址码的。那么,就可以把操作码扩展到这些位置。

举个简单的例子:如果一个指令系统的操作码为2位,那么可以有00、01、10、11四条不同的指令。现在把11作为保留,把操作码扩展到4位,那么 就可以有00、01、10、1100、1101、1110、1111七条指令。其中1100、1101、1110、1111这四条指令的地址码必须少两位。

然后,为了达到操作码扩展的先决条件:减少地址码,设计师们又动足了脑筋,发明了各种各样的寻址方式,如基址寻址、相对寻址等,用以最大限度的压缩地址码长度,为操作码留出空间。

就这样,慢慢地,CISC指令系统就形成了,大量的复杂指令、可变的指令长度、多种的寻址方式是CISC的特点,也是CISC的缺点:因为这些都大大 增加了解码的难度,而在现在的高速硬件发展下,复杂指令所带来的速度提升早已不及在解码上浪费点的时间。除了个人PC市场还在用x86指令集外,服务器以 及更大的系统都早已不用CISC了。x86仍然存在的唯一理由就是为了兼容大量的x86平台上的软件。

在CISC微处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

RISC的产生、发展和现状

RISC(Reduced Instruction Set Computing,精简指令集)。

1975年,IBM的设计师John Cocke研究了当时的IBM370CISC系统,发现其中占总指令数仅20%的简单指令却在程序调用中占了80%,而占指令数80%的复杂指令却只有20%的机会用到。由此,他提出了RISC的概念。

复杂的指令系统必然增加微处理器的复杂性,使处理器的研制时间长,成本高。并且复杂指令需要复杂的操作,必然会降低计算机的速度。基于上述原因,20世纪80年代RISC型CPU诞生了,相对于CISC型CPU ,RISC型CPU不仅精简了指令系统,还采用了一种叫做“超标量和超流水线结构”,大大增加了并行处理能力(并行处理并行处理是指一台服务器有多个CPU同时处理。并行处理能够大大提升服务器的数据处理能力。部门级、企业级的服务器应支持CPU并行处理技术)。也就是说,架构在同等频率下,采用RISC架构的CPU比CISC架构的CPU性能高很多,这是由CPU的技术特征决定的

RISC体系结构和设计思想是80年代初出现的,RISC与CISC指令系统是完全不同,完全决裂的指令系统。

它的基本思路是:抓住CISC指令系统指令种类太多(其中80%以上都是程序中很少使用的指令)、指令格式不规范、寻址方式太多的缺点(例如,VAX 780的指令操作类型超过1000种,而Alpha只有不到50种指令),通过减少指令种类、规范指令格式和简化寻址方式,大量利用寄存器间操作,大大简化处理器的结构、优化VLSI器件使用效率,从而大幅度地提高处理器性能、并行处理能力和性价比。

到80年代后期,RISC技术已经发展成为支持高端服务器系统的主流技术,各厂商纷纷推出了32位RISC微处理器。(如:IBM的PowerPC和Power2,Sun的SPARC,HP的PA-RISC 7000和MIPS的R系列等。)

基于32位RISC芯片的产品在取得了很大的成功,应用日益广泛、软件大量积累、在市场上也产生巨大的影响。

后来,Alpha作为64位RISC技术的领头羊,开创了64位RISC计算的新时代。

各主要厂商也都在90年代先后推出了自己的64位RISC微处理器(包括:IBM的Power和PowerPC系列、HP的PA-RISC 8000系列、Sun的UltraSPARC系列和MIPS的R10K系列等)。在此期间,Alpha始终保持了性能领先的地位。

由于RISC指令集自身的优势,64位RISC微处理器主要在高端服务器领域和高端企业市场上运用。

事实证明,RISC是成功的。80年代末,各公司的RISC CPU如雨后春笋般大量出现,占据了大量的市场。到了90年代,Intel推出了Pentium处理器,从Pentium pro构架开始,也开始使用一种混合的CISC/RISC构架(注意:这里X86架构上有改变,但仍然是IA-32,是32位处理器,直到AMD推出了X86-64及Intel跟随推出IA-32e之后,才有64位技术)。

RISC的最大特点是指令长度固定,指令格式种类少,寻址方式种类少,大多数是简单指令且都能在一个时钟周期内完成,易于设计超标量与流水线,寄存器 数量多,大量操作在寄存器之间进行。

IA-64(EPIC)产生、发展和现状

IA-64 (Intel Architechure-64,英特尔64位体系架构)

EPIC (EPIC–Explicitly Parallel Instruction Computing;显性并行指令计算)

到90年代末,32位芯片的“霸主”Intel宣布与HP合作推出64位IA-64体系结构的处理器。

Inter和HP从1994年开始合作开发新型的64位芯片,它们选择了一个与大多数RISC微处理器大不相同的方向,推出了一种新的64位指令系统体系结构IA-64。它们把这一体系结构称为EPIC(显性并行指令计算)。

EPIC既不是RISC也不是CISC,它实质上是一种吸收了两者长处体系结构。IA-64的EPIC体系结构又在这两者教训基础上另辟蹊径。

EPIC与Cydrome公司(一个80年代走向失败的小巨型机公司)的VLIW体系结构 (Very Long Instruction Word,超长指令集架构)有一定程度的相象之处。

IA-64(EPIC)架构的处理器,目前只应用在Intel的Itanium(安腾)处理器(目前最高端的处理器)上,基于它专为要求苛刻的企业和技术应用而设计,是瞄准高端企业市场的。

Intel 和HP合作开发的IA-64 EPIC体系结构安腾系列的先进性和开放性以及发展潜力,它将要取代64位RISC芯片成为未来系统设计和企业应用的主流平台。

RISC与 IA-64(EPIC)相比

64位RISC和IA-64(EPIC)架构的CPU,主要是应用在要求苛刻的技术应用和企业的高端服务器平台上。

IA-64CPU(安腾)可以说是目前最高端的处理器,基于IA-64先进性和开放性以及发展潜力,它必将要取代64位RISC芯片成为未来系统设计和企业应用的主流平台。

但这向CPU历史上的技术革命,基于其技术架构、成本等各方面的因素,发展到主流民用市场的话,还有非常长的路要走。

【来源】:https://blog.csdn.net/gftygff/article/details/86769126

指令集介绍

一、X86

是微处理器执行的计算机语言指令集,指一个intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合,属于CISC。

1.1、简介

X86指令集是美国Intel公司为其第一块16位CPU(i8086)专门开发的,美国IBM公司1981年推出的世界第一台PC机中的CPU i8088(i8086简化版)使用的也是X86指令,同时电脑中为提高浮点数据处理能力而增加的X87芯片系列数学协处理器则另外使用X87指令,以后就将X86指令集和X87指令集统称为X86指令集。虽然随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium Ⅲ(以下简为PⅢ)系列,但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel公司所生产的所有CPU仍然继续使用X86指令集,所以它的CPU仍属于X86系列。 另外除Intel公司之外,AMD和Cyrix等厂家也相继生产出能使用X86指令集的CPU,由于这些CPU能运行所有的为Intel CPU所开发的各种软件,所以电脑业内人士就将这些CPU列为Intel的CPU兼容产品。由于Intel X86系列及其兼容CPU都使用X86指令集,所以就形成了今天庞大的X86系列及兼容CPU阵容。当然在目前的台式(便携式)电脑中并不都是使用X86系列CPU。

1.2、特点

x86 是一种为了便于编程和提高记忆体访问效率的芯片设计体系,包括两大主要特点:一是使用微代码,指令集可以直接在微代码记忆体里执行,新设计的处理器,只需增加较少的电晶体就可以执行同样的指令集,也可以很快地编写新的指令集程式;二是拥有庞大的指令集,x86拥有包括双运算元格式、寄存器到寄存器、寄存器到记忆体以及记忆体到寄存器的多种指令类型,为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器指令功能外,还通过存于只读存储器(ROM)中的微程序来实现极强的功能,微处理器在分析完每一条指令之后执行一系列初级指令运算来完成所需的功能。

1.3、优缺点

优点:x86指令体系的优势体现在能够有效缩短新指令的微代码设计时间,允许实现CISC体系机器的向上兼容,新的系统可以使用一个包含早期系统的指令集合。另外微程式指令的格式与高阶语言相匹配,因而编译器并不一定要重新编写。

缺点:

- 通用寄存器规模小,x86指令集只有8个通用寄存器,CPU大多数时间是在访问存储器中的数据,影响整个系统的执行速度。而RISC系统往往具有非常多的通用寄存器,并采用了重叠寄存器窗口和寄存器堆等技术,使寄存器资源得到充分的利用

- 解码器影响性能表现,解码器的作用是把长度不定的x86指令转换为长度固定的类似于RISC的指令,并交给RISC内核。解码分为硬件解码和微解码,对于简单的x86指令只要硬件解码即可,速度较快,而遇到复杂的x86指令则需要进行微解码,并把它分成若干条简单指令,速度较慢且很复杂。

- 寻址范围小,约束用户需要。

- 单个指令长度不同,运算能力强大,不过相对来说结构复杂,很难将CISC全部硬件集成在一颗芯片上。

1.4、汇编指令

- 数据传送指令

- 数据传送指令

- 逻辑运算指令

- 串操作指令

- 控制转移指令

- 处理器控制指令

- 保护方式指令

二、X64

又叫“x86-64”,简称为“x64”,是64位微处理器架构及其相应指令集的一种,也是Intel x86架构的延伸产品,也是属于CISC。

2.1、简介

“x86-64”1999由AMD设计,AMD首次公开64位集以扩充给IA-32,称为x86-64(后来改名为AMD64)。其后也为英特尔所采用,现时英特尔称之为“Intel 64”,在之前曾使用过Clackamas Technology (CT)、IA-32e及EM64T。外界多使用"x86-64"或"x64"去称呼此64位架构,从而保持中立,不偏袒任何厂商。

2.2、特点

主要是与X86兼容,既有支持64位通用暂存器、64位整数及逻辑运算,以及64位虚拟地址。设计人员也为架构作出不少改进,部份重大改变如下:新增暂存器,地址阔度加长,“禁止运行”比特 (NX-bit): AMD64其中一个特色是拥有“禁止运行”(No-Execute, NX)的比特,可以防止蠕虫病毒以缓冲器满溢的方式来进行攻击(也称:缓存溢出攻击,Buffer Overflow)。

2.3、优缺点

由于源自X86,都是CSIC,所以具有X86差不多的缺点,跟X86比较,有如下优势:

- 64位寻址空间

- 扩展的寄存器组

- 开发者熟悉的命令集

- 可以在64位结构的操作系统上运行32位程序

- 可以直接使用32位操作系统

2.4、汇编指令

基本跟X86一样,大多数X86指令在X64的64位模式下是有效的。在64位模式不常使用的指令不在支持。如:BCD码算术指令。

三、ARM

曾称进阶精简指令集机器(Advanced RISC Machine)更早称作Acorn RISC Machine,是一个32位精简指令集(RISC)处理器架构。还有基于ARM设计的派生产品,重要产品包括Marvell的XScale架构和德州仪器的OMAP系列。ARM家族占比所有32位嵌入式处理器的75%,成为占全世界最多数的32位架构。是为了提高处理器运行速度而设计的芯片体系,它的关键技术在于流水线操作即在一个时钟周期里完成多条指令。属于RISC。

3.1、简介

一颗主要用于路由器的Conexant ARM处理器是Acorn电脑公司(Acorn Computers Ltd)于1983年开始的开发计划。这个团队由Roger Wilson和Steve Furber带领,着手开发一种新架构,类似进阶的MOS Technology 6502处理器。Acorn有一大堆建构在6502架构上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。团队在1985年时开发出ARM1 Sample版,而首颗"真正"的产能型ARM2于次年量产。ARM2具有32位的数据总线、26位的寻址空间,并提供64 Mbyte的寻址范围与16个32-bit的暂存器。这些暂存器其中有一颗做为(word大小)程式计数器,其前面6 bits和后面2 bits用来保存处理器状态标记(Processor Status Flags)。ARM2可能是全世界最简单实用的32位微处理器,其仅容纳了30,000个晶体管(相较于Motorola六年后的68000其包含了70,000颗)。主要应用于工控/嵌入式和手持设备等领域。

3.2、特点

ARM指令集架构的主要特点:一是体积小、低功耗、低成本、高性能;二是大量使用寄存器且大多数数据操作都在寄存器中完成,指令执行速度更快;三是寻址方式灵活简单,执行效率高;四是指令长度固定,可通过多流水线方式提高处理效率。

3.3、优缺点

- 体积小,低功耗,低成本,高性能;

- 支持 Thumb ( 16 位) /ARM ( 32 位)双指令集,能很好的兼容 8 位 /16 位器件; 大量使用寄存器,指令执行速度更快;大多数数据操作都在寄存器中完成;

- 寻址方式灵活简单,执行效率高;

- 指令长度固定;

- 流水线处理方式

- Load_store结构:在RISC中,所有的计算都要求在寄存器中完成。而寄存器和内存的通信则由单独的指令来完成。而在CSIC中,CPU是可以直接对内存进行操作的。

3.4、汇编指令

- 算数和逻辑指令

- 比较指令

- 跳转指令

- 移位指令

- 程序状态字访问指令存

- 储器访问指令

3.5 主要的指令集体系结构版本:

-

ARMv1:该版本的原型机是ARM1,没有用于商业产品。

-

ARMv2:对V1版进行了扩展,包含了对32位结果的乘法指令和协处理器指令的支持。

-

ARMv3:ARM公司第一个微处理器ARM6核心是版本3的,它作为IP核、独立的处理器、具有片上高速缓存、MMU和写缓冲的集成CPU。

-

ARMv4:当前应用最广泛的ARM指令集版本。

ARM7TDMI、ARM720T、ARM9TDMI、ARM940T、ARM920T、Intel的StrongARM等是基于ARMv4T版本。 -

ARMv5:ARM9E-S、ARM966E-S、ARM1020E、ARM 1022E以及XScale是ARMv5TE的。ARM9EJ-S、ARM926EJ-S、ARM7EJ-S、ARM1026EJ-S是基于ARMv5EJ的。ARM10也采用。

其中后缀意义如下:

E:增强型DSP指令集。包括全部算法和16位乘法操作。

J:支持新的Java。 -

ARMv6:采用ARMv6核的处理器是ARM11系列。

ARM1136J(F)-S基于ARMv6主要特性有SIMD、Thumb、Jazelle、DBX、(VFP)、MMU。

ARM1156T2(F)-S基于ARMv6T2 主要特性有SIMD、Thumb-2、(VFP)、MPU。

ARM1176JZ(F)-S基于ARMv6KZ 在 ARM1136EJ(F)-S 基础上增加MMU、TrustZone。

ARM11 MPCore基于ARMv6K 在ARM1136EJ(F)-S基础上可以包括1-4 核SMP、MMU。 -

ARMv7:Cortex-A,Cortex-M,Cortex-R

ARMv7提供了三个概要文件:ARMv7-A :

- 实现具有多种模式的传统ARM体系结构。

- 支持基于内存管理单元(MMU)的虚拟内存系统体系结构(VMSA)。

- ARMv7-A实现可以称为VMSAv7实现。支持ARM和Thumb指令集。

ARMv7-R :实时配置文件

- 实现具有多种模式的传统ARM体系结构。

- 支持基于内存保护单元(MPU)的受保护内存系统体系结构(PMSA)。

- ARMv7-R实现可以称为PMSAv7实现。支持ARM和Thumb指令集。

ARMv7-M :在ARMv7-M体系结构参考手册中描述的 微控制器配置文件:

- 实现一个为低延迟中断处理设计的程序员模型,使用寄存器的硬件堆栈和对用高级语言编写中断处理程序的支持。

- 实现ARMv7 PMSA的变体。

- 支持ARM和Thumb指令集。

-

ARMv8:ARMv8架构包含两个执行状态:AArch64和AArch32。AArch64执行状态针对64位处理技术,引入了一个全新指令集A64;而AArch32执行状态将支持现有的ARM指令集。ARMv7架构的主要特性都将在ARMv8架构中得以保留或进一步拓展,如:TrustZone技术、虚拟化技术及NEON advanced SIMD技术,等。

-

ARMv9:???

ARM处理器内核

| 架构 | 处理器家族 |

|---|---|

| ARMv1 | ARM1 |

| ARMv2 | ARM2、ARM3 |

| ARMv3 | ARM6、ARM7 |

| ARMv4 | StrongARM、ARM7TDMI、ARM9TDMI |

| ARMv5 | ARM7EJ、ARM9E、ARM10E、XScale |

| ARMv6 | ARM11、ARM Cortex-M |

| ARMv7 | ARM Cortex-A、ARM Cortex-M、ARM Cortex-R |

| ARMv8 | Cortex-A35、Cortex-A50系列[14]、Cortex-A72、Cortex-A73 |

| 家族 | 架构 | 内核 | 特色 | 缓存 (I/D)/MMU | 常规 MIPS 于 MHz | 应用 |

|---|---|---|---|---|---|---|

| ARM1 | ARMv1 | ARM1 | 无 | |||

| ARM2 | ARMv2 | ARM2 | Architecture 2 加入了MUL(乘法)指令 | 无 | 4 MIPS @ 8MHz | Acorn Archimedes,Chessmachine |

| ARMv2a | ARM250 | Integrated MEMC (MMU),图像与IO处理器。Architecture 2a 加入了SWP和SWPB(置换)指令。 | 无,MEMC1a | 7 MIPS @ 12MHz | Acorn Archimedes | |

| ARM3 | ARMv2a | ARM2a | 首次在ARM架构上使用处理器缓存 | 均为4K | 12 MIPS @ 25MHz | Acorn Archimedes |

| ARM6 | ARMv3 | ARM610 | v3 架构首创支援定址32位元的内存(针对26位元) | 均为4K | 28 MIPS @ 33MHz | Acorn Risc PC 600,Apple Newton |

| ARM7 | ARMv3 | |||||

| ARM7TDMI | ARMv4T | ARM7TDMI(-S) | 三级流水线 | 无 | 15 MIPS @ 16.8 MHz | Game Boy Advance,Nintendo DS,iPod |

| ARM710T | 均为8KB, MMU | 36 MIPS @ 40 MHz | Acorn Risc PC 700,Psion 5 series,Apple eMate 300 | |||

| ARM720T | 均为8KB, MMU | 60 MIPS @ 59.8 MHz | Zipit | |||

| ARM740T | MPU | |||||

| ARMv5TEJ | ARM7EJ-S | Jazelle DBX | 无 | |||

| StrongARM | ARMv4 | |||||

| ARM8 | ARMv4 | |||||

| ARM9TDMI | ARMv4T | ARM9TDMI | 五级流水线 | 无 | ||

| ARM920T | 16KB/16KB, MMU | 200 MIPS @ 180 MHz | Armadillo,GP32,GP2X(第一颗内核), Tapwave Zodiac(Motorola i. MX1) | |||

| ARM922T | 8KB/8KB, MMU | |||||

| ARM940T | 4KB/4KB, MPU | GP2X(第二颗内核) | ||||

| ARM9E | ARMv5TE | ARM946E-S | 可变动,tightly coupled memories, MPU | Nintendo DS,Nokia N-Gage Conexant 802.11 chips | ||

| ARM966E-S | 无缓存,TCMs | ST Micro STR91xF,包含Ethernet [1] | ||||

| ARM968E-S | 无缓存,TCMs | |||||

| ARMv5TEJ | ARM926EJ-S | Jazelle DBX | 可变动,TCMs, MMU | 220 MIPS @ 200 MHz | 移动电话:Sony Ericsson(K, W系列),明基西门子(x65 系列和新版的) | |

| ARMv5TE | ARM996HS | 无振荡器处理器 | 无缓存,TCMs, MPU | |||

| ARM10E | ARMv5TE | ARM1020E | (VFP),六级流水线 | 32KB/32KB, MMU | ||

| ARM1022E | (VFP) | 16KB/16KB, MMU | ||||

| ARMv5TEJ | ARM1026EJ-S | Jazelle DBX | 可变动,MMU or MPU | |||

| XScale | ARMv5TE | 80200/IOP310/IOP315 | I/O处理器 | |||

| 80219 | 400/600MHz | Thecus N2100 | ||||

| IOP321 | 600 BogoMips @ 600 MHz | Iyonix | ||||

| IOP33x | ||||||

| IOP34x | 1-2核,RAID加速器 | 32K/32K L1, 512K L2, MMU | ||||

| PXA210/PXA250 | 应用处理器,七级流水线 | Zaurus SL-5600 | ||||

| PXA255 | 32KB/32KB, MMU | 400 BogoMips @ 400 MHz | Gumstix,Palm Tungsten E2 | |||

| PXA26x | 可达 400 MHz | Tungsten T3 | ||||

| PXA27x | 800 MIPS @ 624 MHz | HTC Universal、Zaurus SL-C1000、3000、3100、3200、Dell Axim x30、x50和 x51 系列 | ||||

| PXA800(E)F | ||||||

| Monahans | 1000 MIPS @ 1.25 GHz | Mavell PXA300/PXA310/PXA320, Max frequency : PXA300@624Mhz, PXA310/PXA320@806Mhz | ||||

| PXA900 | Blackberry 8700, Blackberry Pearl (8100) | |||||

| IXC1100 | Control Plane Processor | |||||

| IXP2400/IXP2800 | ||||||

| IXP2850 | ||||||

| IXP2325/IXP2350 | ||||||

| IXP42x | NSLU2 | |||||

| IXP460/IXP465 | ||||||

| ARM11 | ARMv6 | ARM1136J(F)-S | SIMD, Jazelle DBX, (VFP),八级流水线 | 可变动,MMU | ?? @ 532-665MHz (i.MX31 SoC) | Nokia N93,Zune,Nokia N800 |

| ARMv6T2 | ARM1156T2(F)-S | SIMD, Thumb-2, (VFP),九级流水线 | 可变动,MPU | |||

| ARMv6KZ | ARM1176JZ(F)-S | SIMD, Jazelle DBX, (VFP) | 可变动,MMU+TrustZone | |||

| ARMv6K | ARM11 MPCore | 1-4核对称多处理器,SIMD, Jazelle DBX, (VFP) | 可变动,MMU | |||

| Cortex-A (32 bit) | ARMv7-A | Cortex-A7 | 1.75 DMIPS/MHz 1 GHz到1.2GHz | 全志a31、MediaTek MT6589,MT6572 | ||

| Cortex-A8 | Application profile, VFP, NEON, Jazelle RCT, Thumb-2, 13-stage pipeline | 可变动 (L1+L2), MMU+TrustZone | 2.0 DMIPS/MHz 从600 MHz到超过1 GHz | Texas Instruments OMAP3、Apple A4 | ||

| Cortex-A9 | 2.50 DMIPS @ 1GHz | Apple A5、Apple A5X、MediaTek MT6577,MT6575、Rockchip RK3088,RK3188, VIA Elite-E1000 | ||||

| Cortex-A12 | 大约3.00 DMIPS @ 1.4GHz 28nm | 预估等同Apple A6、Apple A6X水平。 | ||||

| Cortex-A15 | Thumb-2 TrustZone® NEON DSP & SVFPv4 | 从3.50 DMIPS到超过4.0 DMIPS @ 从1.4MHz到超过2.5GHz | Tegra 4 Exynos5250 | |||

| Cortex-A9 MPCore | ||||||

| Cortex-R | ARMv7-R | Cortex-R4(F) | Embedded profile, (FPU) | 可变动缓存,MMU可选配 | 600 DMIPS | Broadcom is a user |

| Cortex-M | ARMv7-M | Cortex-M3 | Microcontroller profile | 无缓存,(MPU) | 120 DMIPS @ 100MHz | Luminary Micro[2] 微控制器家族 |

| ARMv6-M | Cortex-M0 | |||||

| Cortex-M1 | ||||||

| ARMv7-ME | Cortex-M4 | Optional 8 region MPU with sub regions and background region | 1.25 DMIPS/MHz |

四、SSE指令集

Streaming SIMD Extensions

由于MMX指令并没有带来3D游戏性能的显著提升,1999年Intel公司在[Pentium III](https://baike.baidu.com/item/Pentium III)CPU产品中推出了数据流单指令序列扩展指令(SSE)。SSE兼容MMX指令,它可以通过SIMD(单指令多数据技术)和单时钟周期并行处理多个浮点来有效地提高浮点运算速度。在MMX指令集中,借用了浮点处理器的8个寄存器,这样导致了浮点运算速度降低。而在SSE指令集推出时,Intel公司在Pentium III CPU中增加了8个128位的SSE指令专用寄存器。而且SSE指令寄存器可以全速运行,保证了与浮点运算的并行性。

五、SSE2指令集

在Pentium 4 CPU中,Intel公司开发了新指令集SSE2。这一次新开发的SSE2指令一共144条,包括浮点SIMD指令、整形SIMD指令、SIMD浮点和整形数据之间转换、数据在MMX寄存器中转换等几大部分。其中重要的改进包括引入新的数据格式,如:128位SIMD整数运算和64位双精度浮点运算等。为了更好地利用高速缓存。另外,在Pentium 4中还新增加了几条缓存指令,允许程序员控制已经缓存过的数据。

六、SSE3指令集

相对于SSE2,SSE3又新增加了13条新指令,此前它们被统称为pni(prescott new instructions)。13条指令中,一条用于视频解码,两条用于线程同步,其余用于复杂的数学运算、浮点到整数转换和SIMD浮点运算。

七、SSE4指令集

SSE4又增加了50条新的增加性能的指令,这些指令有助于编译、媒体、字符/文本处理和程序指向加速。

SSE4指令集将作为Intel公司未来“显著视频增强”平台的一部分。该平台的其他视频增强功能还有Clear Video技术(CVT)和统一显示接口(UDI)支持等,其中前者是对ATi AVIVO技术的回应,支持高级解码、后处理和增强型3D功能。

八、3D Now!扩展指令集

2010年AMD官方宣布放弃3DNow!指令集!

1996年,Intel Pentium处理器率先加入了MMX指令集,极大地提高了多媒体处理能力,但仅支持整数运算,浮点运算仍然要使用传统的x87协处理器指令。随后在1998年,AMD推出了包含21条新指令的3DNow!指令集*(据说是3D No Waiting!的缩写)*,并用于其K6-2处理器,使之成为第一个能够执行浮点SIMD指令的x86处理器,实现了x86架构下最快的浮点单元,四倍于x87协处理器。

3DNow!指令集赢得了业界的广泛支持,包括微软DX7都对其进行了优化,AMD处理器的游戏性能得以第一次超越Intel,K6-2和随后的K6-III成为市场上的热门产品。

1999年,AMD Athlon处理器发布,3DNow!指令集也增加了5条新指令,成为扩展3DNow!,但是同年Intel又推出了SSE指令集,在提供3DNow!几乎所有功能的同时大大提高了单精度浮点处理速度,还完全支持IEEE754标准,3DNow!优势不再。

之后主流操作系统和软件都开始支持SSE指令集并为其优化,AMD 2000年的新款Athlon处理器(代号雷鸟)中也加入了SSE。之后的时间里,AMD开始致力于AMD64架构的开发,SIMD指令集方面则跟随Intel,连续添加了SSE2、SSE3,不再改进3DNow!。

九、EM64T指令集

Intel公司的EM64T(Extended Memory 64 Technology)即64位内存扩展技术。该技术为服务器和工作站平台应用提供扩充的内存寻址能力,拥有更多的内存地址空间,可带来更大的应用灵活性,特别有利于提升音频视频编辑、CAD设计等复杂工程软件及游戏软件的应用。常说的64位指的是AMD公司出的64位CPU,而EM64T则是Intel公司按照自己的意思理解出来的64位,也就是和AMD公司的64位对应的另一种叫法。

十、RISC指令集

RISC指令集是以后高性能CPU的发展方向。它与传统的CISC(复杂指令集)相对。相比而言,RISC的指令格式统一,种类比较少,寻址方式也比复杂指令集少。使用RISC指令集的体系结构主要有ARM、MIPS。

十一、3DNow!+指令集

在原有的指令集基础上,增加到52条指令,其中包含了部分SSE指令,该指令集主要用于新型的AMD CPU上。

十二、AVX指令集

Intel AVX指令集在SIMD计算性能增强的同时也沿用了的MMX/SSE指令集。不过和MMX/SSE的不同点在于增强的AVX指令,从指令的格式上就发生了很大的变化。x86(IA-32/Intel 64)架构的基础上增加了prefix(Prefix),所以实现了新的命令,也使更加复杂的指令得以实现,从而提升了x86 CPU的性能。

AVX并不是x86 CPU的扩展指令集,可以实现更高的效率,同时和CPU硬件兼容性也更好,并且也有着足够的扩展空间,这都和其全新的命令格式系统有关。更加流畅的架构就是AVX发展的方向,换言之,就是摆脱传统x86的不足,在SSE指令的基础上AVX也使SSE指令接口更加易用。

针对AVX的最新的命令编码系统,Intel也给出了更加详细的介绍,其中包括了大幅度扩充指令集的可能性。比如Sandy Bridge所带来的融合了乘法的双指令支持。从而可以更加容易地实现512bits和1024bits的扩展。而在2008年末到2009年推出的meniikoaCPU“Larrabee(LARAB)”处理器,就会采用AVX指令集。从地位上来看AVX也开始了Intel处理器指令集的新篇章。