FPGA芯片在正常工作的时候需要系统提供三套供电机制——外部端口供电机制、内部逻辑供电机制和专有电路供电机制。

一、外部端口供电

1、意义

FPGA芯片通过IO资源接收外界相关电平信号或者按要求发送相关电平信号来与外界电路通信,而保证正确通信的前提就是FPGA芯片的IO端口应该具有和外界电路相统一的电平标准。这就是外部端口供电机制的作用。

一般来说,在接口资源中命名类似VCCIO的管脚即为用户IO资源的供电管脚。

2、常见接口电平

TTL电平标准与低压TTL电平标准

- TTL

工作于TTL接口标准下的数字电路,其内部有源器件的标准电源供给应为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V;

- 低压TTL电平标准-LVTTL3V3 (标准电源供给为3.3V)

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V;

- 低压TTL电平标准-LVTTL2V5(标准电源供给为2.5V)

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.2V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V。

CMOS电平标准与低压CMOS电平标准

- CMOS

工作于CMOS接口标准下的数字电路,其内部有源器件的标准电源供给为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于4.45V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于3.5V,状态0的判定要求为小于等于1.5V。

- 低压CMOS电平标准-LVCOMS3V3(标准电源供给为3.3V)

对于输出端,状态1的电压要求为大于等于3.2V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.7V。

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V。

更多接口电压标准内容,详见数字系统中接口电平标准汇总

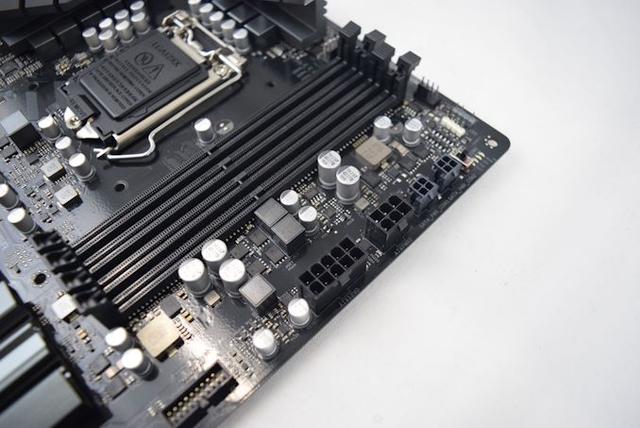

3、IO Bank

FPGA芯片集成度很高,一片FPGA芯片上具有大量IO资源。如果所有IO资源支持同一种电平标准显然是不合理的,因为外部设备的电平标准是各种何样的。

因此,FPGA会根据位置关系,将IO资源划分成若干的IO Bank,而每一个IO Bank具有单独的VCCIO接口资源,从而使得一片FPGA芯片的IO资源可以支持多种接口电平通信。(各自工作,互不影响)

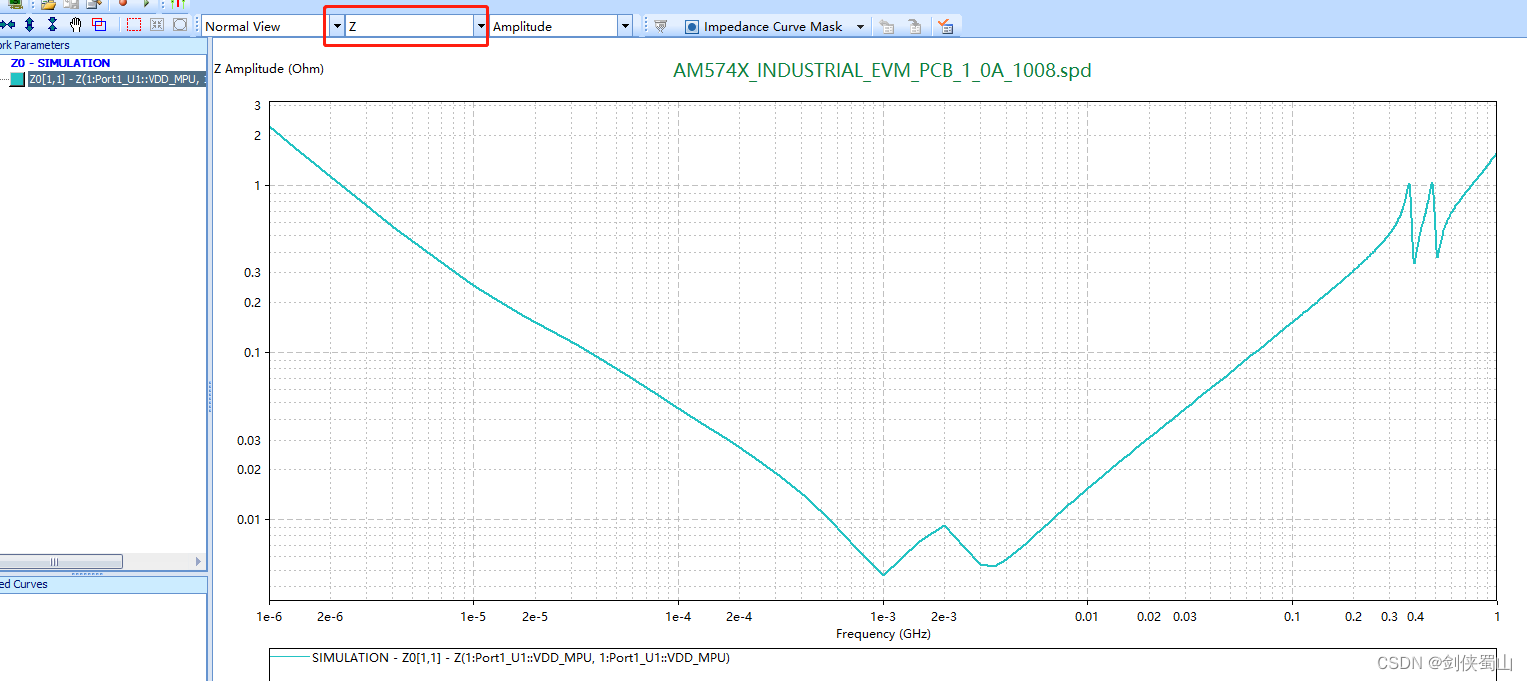

二、内部逻辑供电

一般来说,在接口资源中命名类似VCCINT的管脚即为内部逻辑供电的管脚。

一片FPGA芯片可以支持多种VCCINT电平标准,但是每次工作的时候,只能选定其中的一种为内部逻辑进行供电。

原因:

1、FPGA芯片内部供电与外部端口供电有差异:外部端口通信看重电压的变化,而对电流要求较低;而内部逻辑一般具有低电压高电流的特性;

2、端口因要满足众多接口标准,因而具有多种供电电平;而内部逻辑与不受接口电平标准影响,外部不同电平标准经IO后均转换为统一的高低电平;

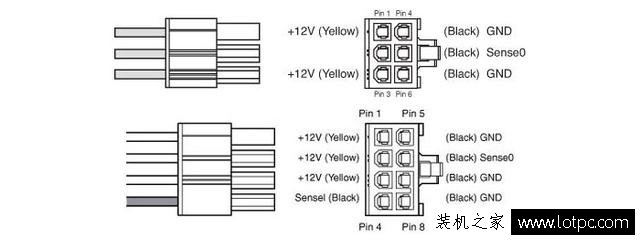

三、专有电路供电

顾名思义,FPGA中有些资源对电源的要求是比较特殊的,需要专门的供电电路供电驱动;

四、参考文献

https://baike.baidu.com/item/TTL%E7%94%B5%E5%B9%B3/5904345?fr=aladdin

FPGA之道(11)FPGA芯片的供电系统

数字系统中接口电平标准汇总