👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

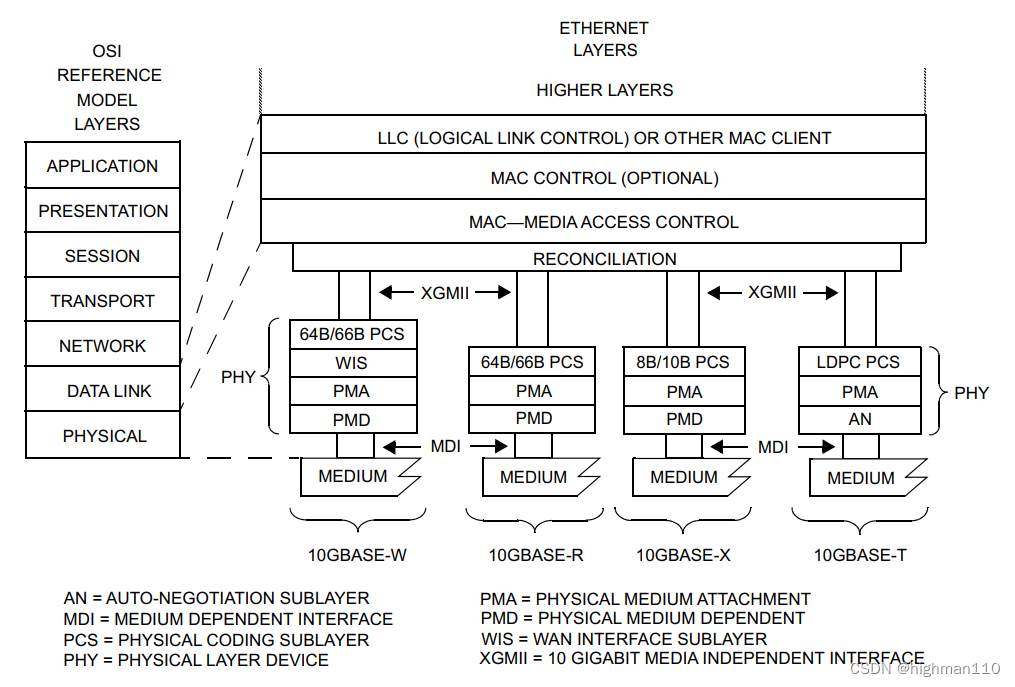

本篇开始讲述10G以太网。802.3定义了多种10G物理接口实体,如下表所示:

按照我们之前分享过的接口命名规则,X表示在10G以太网中使用8B/10B编码,R表示10G以太网中使用64B/66B编码,按照不同的PCS层,可分为以下几类:

10Gbase-SW、10Gbase-LW、10Gbase-EW、10Gbase-SR、10Gbase-LR、10Gbase-ER:使用64B/66B编码。使用不同距离的多模或单模光模块连接,其中W表示广域网接口。

10Gbase-LX4、10Gbase-LX4:使用8B/10B编码。使用4lane光模块连接。

10Gbase-T:使用LDPC编码。使用双绞线连接。

下面我们对以上三种PCS子层的相关功能进行阐述,PMD和PMA子层的功能与1000base-X类似,PMA主要是数据的串行/解串以及线路时钟恢复,PMD主要是NRZ编码和解码以及光信号检测,这里不再赘述。

64B/66B PCS

10Gbase-W、10Gbase-R使用,功能框图如下:

主要实现以下功能:

a)将8个XGMII数据字节编码到66位块(64B/66B)。

b)通过Gearbox将66bit数据以16bit传输到PMA。

c)当连接到WAN PMD时,删除(插入)空闲码字以补偿MAC和PMD之间的速率差。(10Gbase-W速率9.95328Gb/s,10Gbase-R速率10.3125Gb/s)

d)进行同步头和误码监控。

e)数据的加扰和解扰。

f)可选的EEE功能控制。

g)支持clause 45规定的MDIO接口和寄存器集,以报告状态并实现对PCS的控制。

8B/10B PCS:

10Gbase-X使用,功能框图如下:

主要实现以下功能:

a)将32个XGMII数据位和4个XGMII控制位编码到四个并行通道,每个通道传输10位代码组,用于与底层PMA通信。

b)四个PMA并行通道的解码,每个通道传输10位代码组,到32个XGMII数据位和4个XGMII控制位。

c)同步每条lane上的代码组,以确定代码组边界。

d)对所有lane上的代码组做deskew,获得对齐的码型。

e)支持clause 45规定的MDIO接口和寄存器集,以报告状态并实现对PCS的控制。

f)将XGMII空闲控制字符转换为随机序列的代码组,以实现串行lane同步、时钟频率补偿和lane到lane对齐。

g)时钟频率补偿协议。

h)发送和接收空闲序列时进行链路初始化。

i) 故障条件的链路状态报告。

LDPC PCS:

10Gbase-T使用,功能框图如下:

10Gbase-T以太网PCS层功能和1000base-T类似,主要完成数据的编解码功能,编码方式为LDPC(低密度奇偶校验)和DSQ128,下面详细展开说明。

10Gbase-T编码原理描述:

从《【以太网硬件六】1000base-T物理层编码究竟是怎么编的?》一文中我们知道,1000Base-T 使用了 PAM5 ( 5 级脉冲调幅技术)调制技术。在 PAM5 模式下,介质中传输的信号不再是简单的 0 和 1 ,而是分成了 5 个级别( -2 , -1 , 0 , 1 , 2 )。这个被分为 5 个级别的电平信号称之为码元, 1 个码元所能携带的多少个 bit 的信息取决于码元的特性和编码的方式。比如 PAM5 ,每个 PAM5 码元最多携带 2.32 个bit( 2^2.32=5 ),考虑到编码的效率及需要纠错码和同步码,所以最终 1000Base-T 每个码元携带 2 个 bit 的信息。

根据奈氏准则,理想低通信道下的最高码元传输速率= 2* 带宽,我们知道 1000Base-T 的码元速率为 125MBd/ 秒,所以要求至少有 62.5Mhz 的传输带宽。如果沿用 1000Base-T 的技术,那 10GBase-T 的码元传输速率为 1250MBd/ 秒,系统最小传输带宽为 625MHz 。这对传输系统的性能提出了很高的要求;但如果提高码元的性能,让一个码元携带更多的 Bit ,降低系统最小带宽,就需要强大的处理器进行编解码处理,那意味着成本的增加,这是一对矛盾。最后经过性能和成本的平衡, 10GBase-T 使用了 PAM16 技术( 16 级脉冲调幅,采用 (-15 , -13 , -11 , -9 , -7 , -5 , -3 , -1 , 1 , 3 , 5 , 7 , 9 , 11 , 13 , 15 ),800M 每秒的码元速率,最小带宽要求 400Mhz。

为了让 PAM16 能够安全的传输 10Gbps ( BER=10E-12 ),就需要设置一定的编码规则。在 10Gbase-T 系统中, 2 个连续的 PAM16 码元背靠背形成了 16*16 的二维矩阵,选取其中的 128 个点组成 128 双矩阵( 128 point Double Square )进行信号编码。相邻 2 个点之间的距离由原来的 D 增加到了√2D ,最大限度的拉开了相邻点之间的距离。此举提高了大约 3 个 dB 的信噪比。

为了能够提高 BER ,还要加入校验码进行前向纠错, 10GBase-T 采用的 LDPC 码 ( 低密度奇偶校验码 ) 是一种线性分组码 , 具有优越的纠错性能和巨大的实用价值 , 被认为是迄今为止性能最好的纠错码。 LDPC 码的性能能够逼近香农极限 , 同时这种逼近又是在不太高的译码复杂度下实现的,硬件实现简单。同样兼顾性能和成本 10GBase-T 在 128DSQ 的上采用了前 3 位无编码保护和后 4 位 LDPC(1723,2048) 编码保护的混合方式。

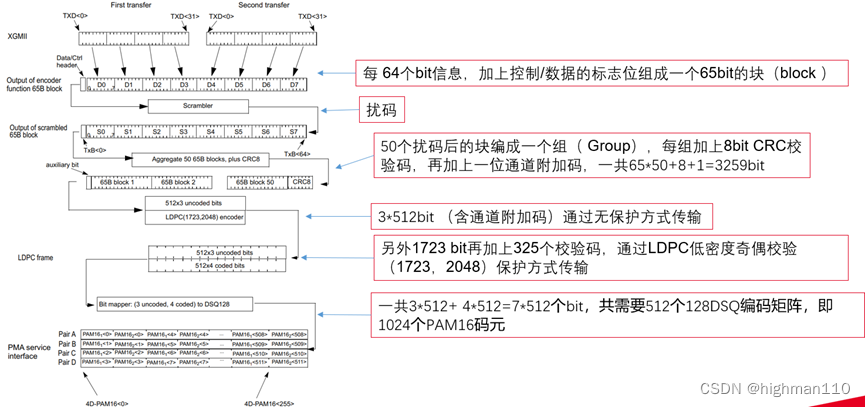

10Gbase-T编码过程描述:

上图是发送方向的编码过程:

每64个bit信息,加上控制/数据的标志位组成一个65bit的块(block),然后将这个块做扰码,将 50个扰码后的块编成一个组( Group),每个组加上8bit CRC校验码。一共生成65*50+8=3258个bit,再附加上一个通道附加码一共是3259个bit。

3259个bit分成2个部分,3*512bit (含通道附加码)通过无保护方式传输,另外1723 bit再加上325个校验码,通过LDPC(1723,2048)保护方式传输,这样共需要512个128DSQ编码( 3*512+4*512=512个7bit标签帧,7bit总共对应有128种编码),也就是1024个PAM16(一个128DSQ由两个PAM16背靠背形成)符号矩阵。最终相当于每个PAM16携带3.125个bit信息(64*50/1024=3.125),双绞线上波特率为800MBd,数据速率为3.125*800M*4=10G bps。