前言

之前网上的教程都是基于Vivado2018的,后来接手一个未完工的项目,是使用Vivado2020.1创建的,非常尴尬,只能打开,不能编辑。千辛万苦把2020.1安装好,当然此时不仅仅是Vivado2020.1了,而是vitis 2020.1。安装完,又发现之前熟悉的SDK怎么不见了,一番折腾之后原来是xilinx公司改变的策略,把PL与PS的开发直接分开了,一言难尽,还是按照老套路来干吧。

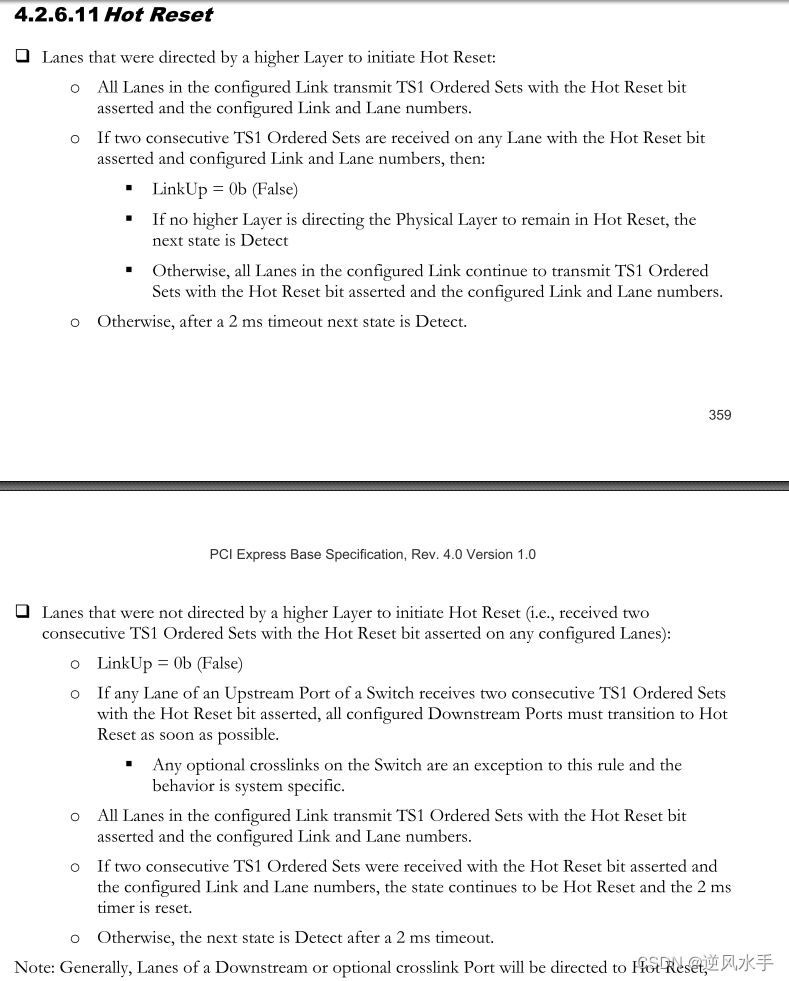

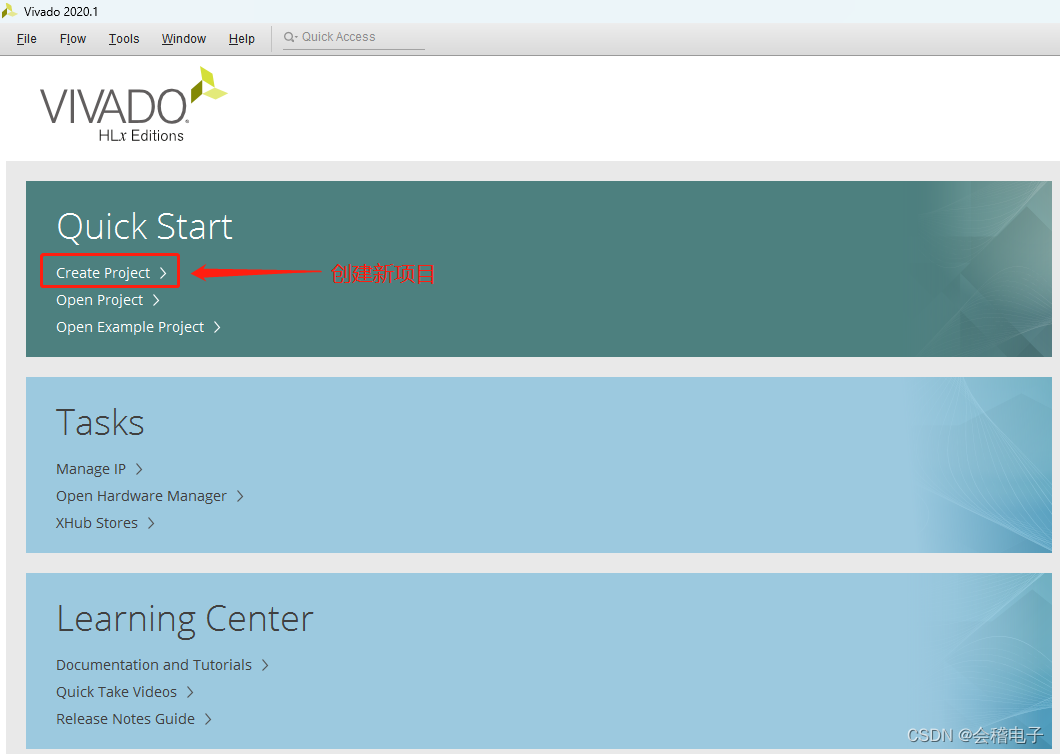

1、双击Vivado2020.1图标,在弹出的界面上,点击Quick Start 栏的Create Project,创建新项目

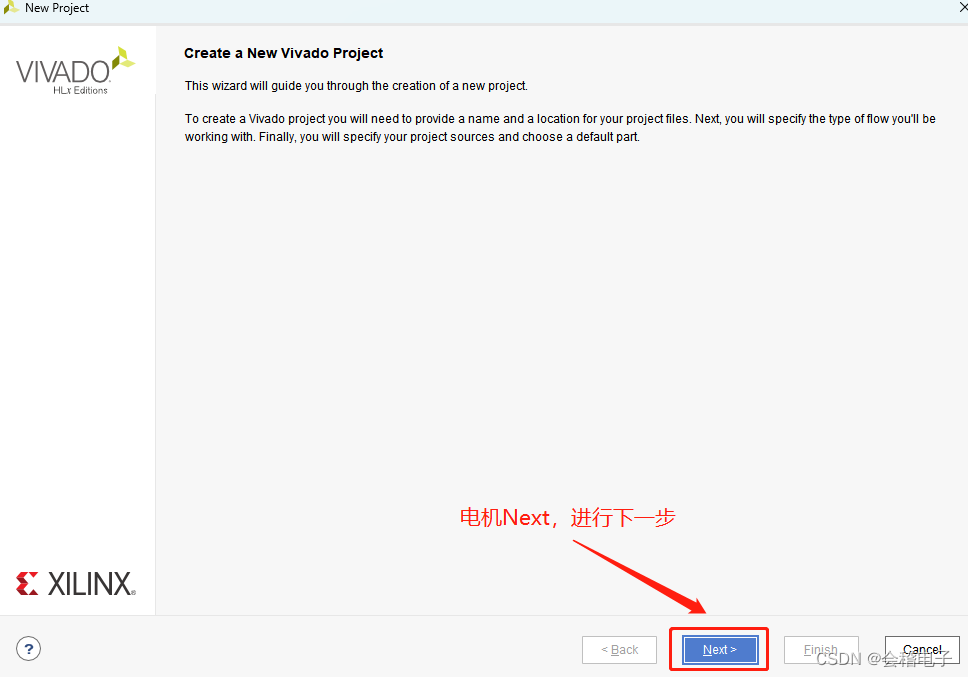

2、在弹出的界面,点击Next

3、修改一下项目名称和保存路径,点击Next

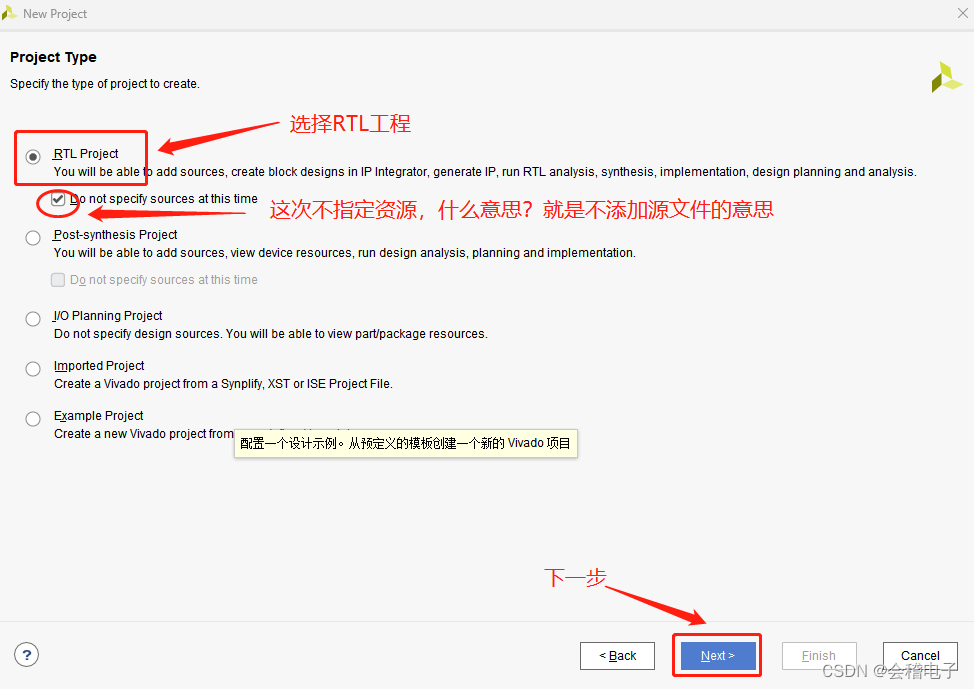

4、在弹出的界面选择项目类型,点击Next

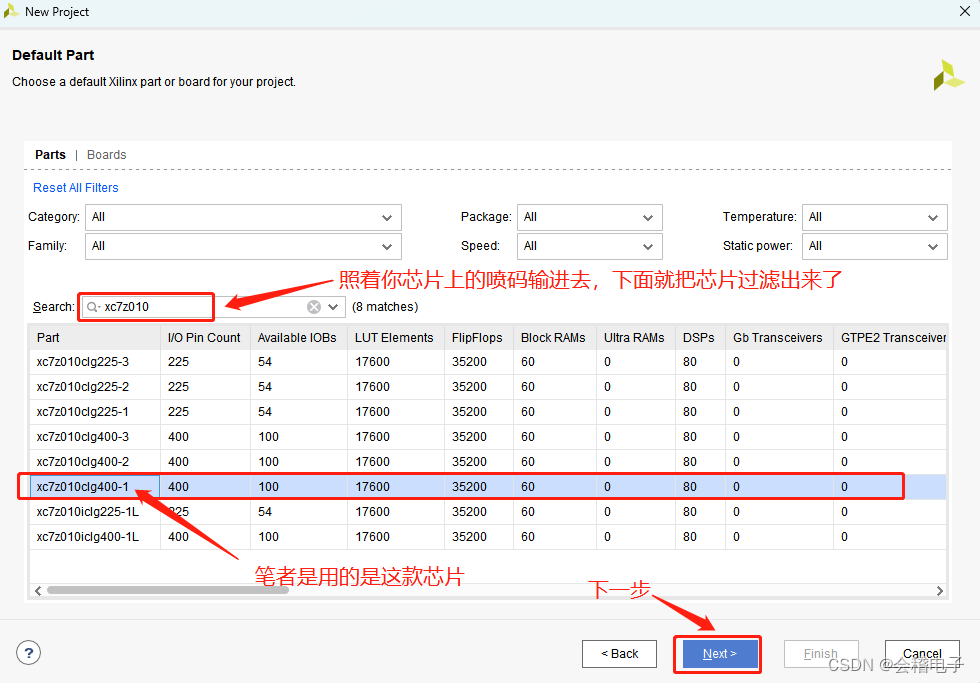

5、在弹出的界面,选择使用的芯片,点击Next

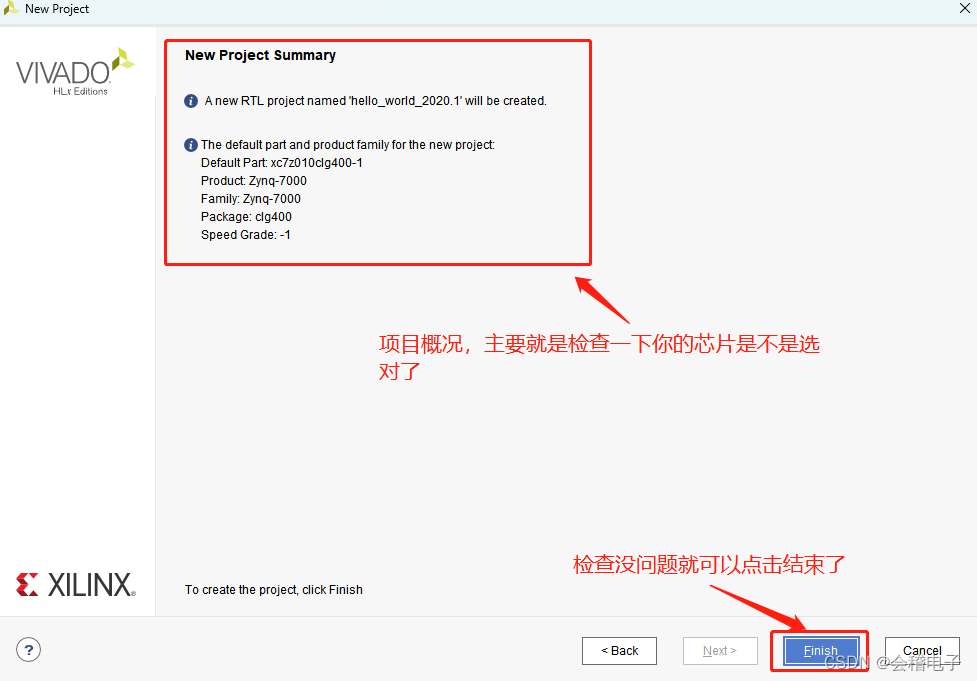

6、在弹出的界面,检查一下芯片是否选对了,然后点击Finish

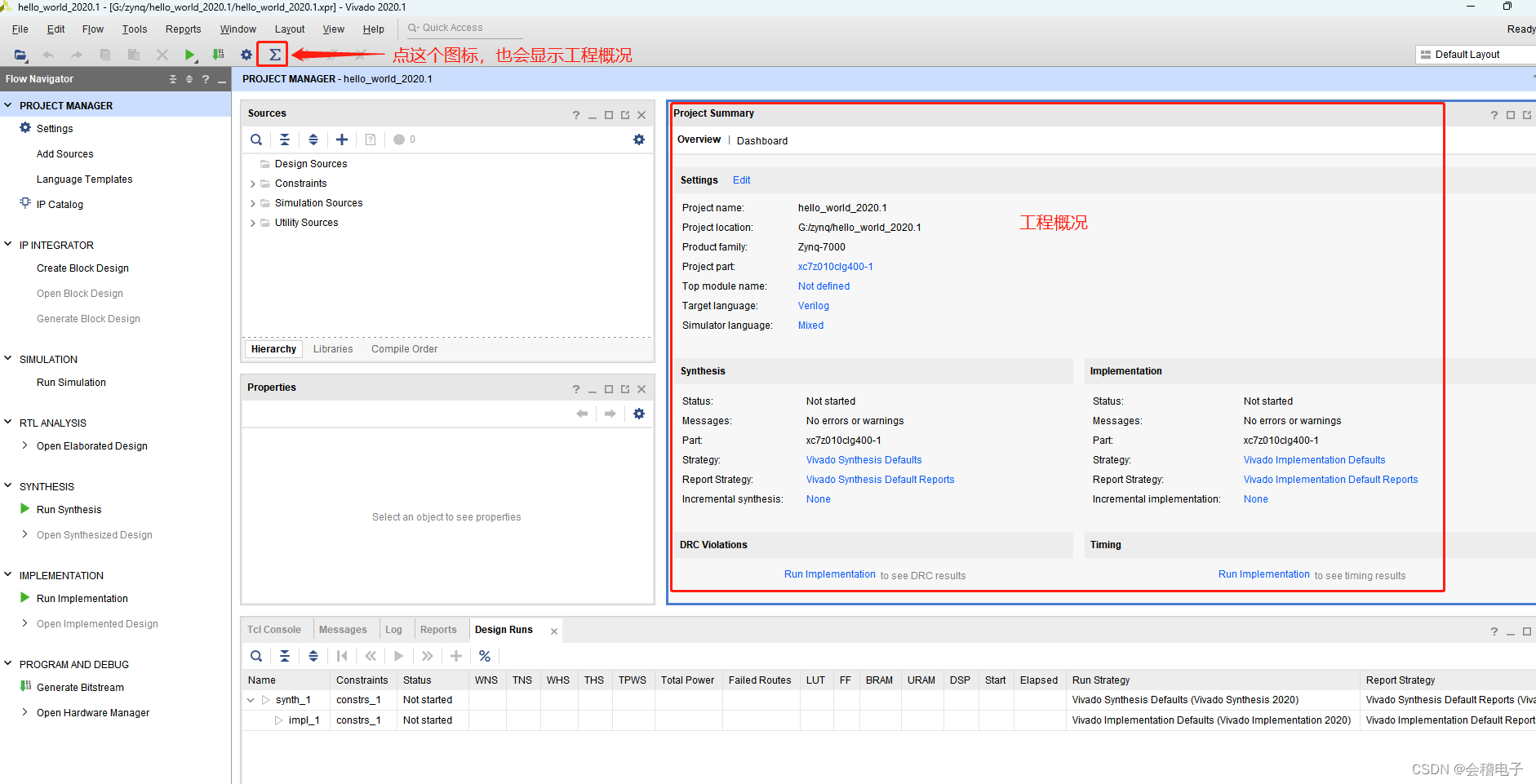

7、至此,空的工程就建好了,界面如下

8、往工程里面添加模块,在流程导航栏Flow Navigator下,找到IP INTEGRATOR,点击下面的Create Block Design

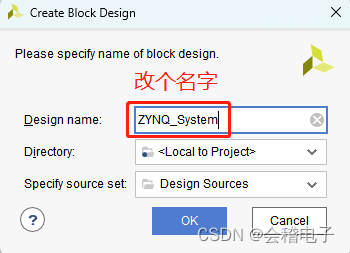

9、在弹窗中修改一下模块的名字,点击OK

10、整个界面就变成了下面这样,主要是在Diagram中添加各种IP核,用以设计

11、点击Diagram框中的“+”符号,添加IP核,也可以在框中,右击选择Add IP...

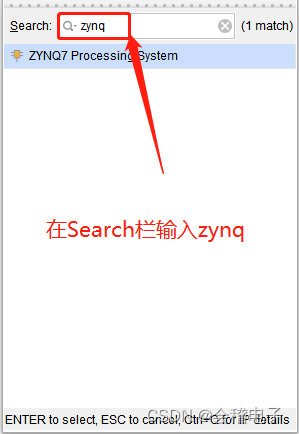

12、在弹出的界面中,Search栏输入zynq,就会出现ZYNQ7 Processing System,这就是我们目标处理器的IP

13、双击ZYNQ7 Processing System,将其添加到设计中,此时Diagram栏就变成下图这样

14、接下来就是对这个ZYNQ IP的配置 ,双击ZYNQ IP,就会弹出配置界面

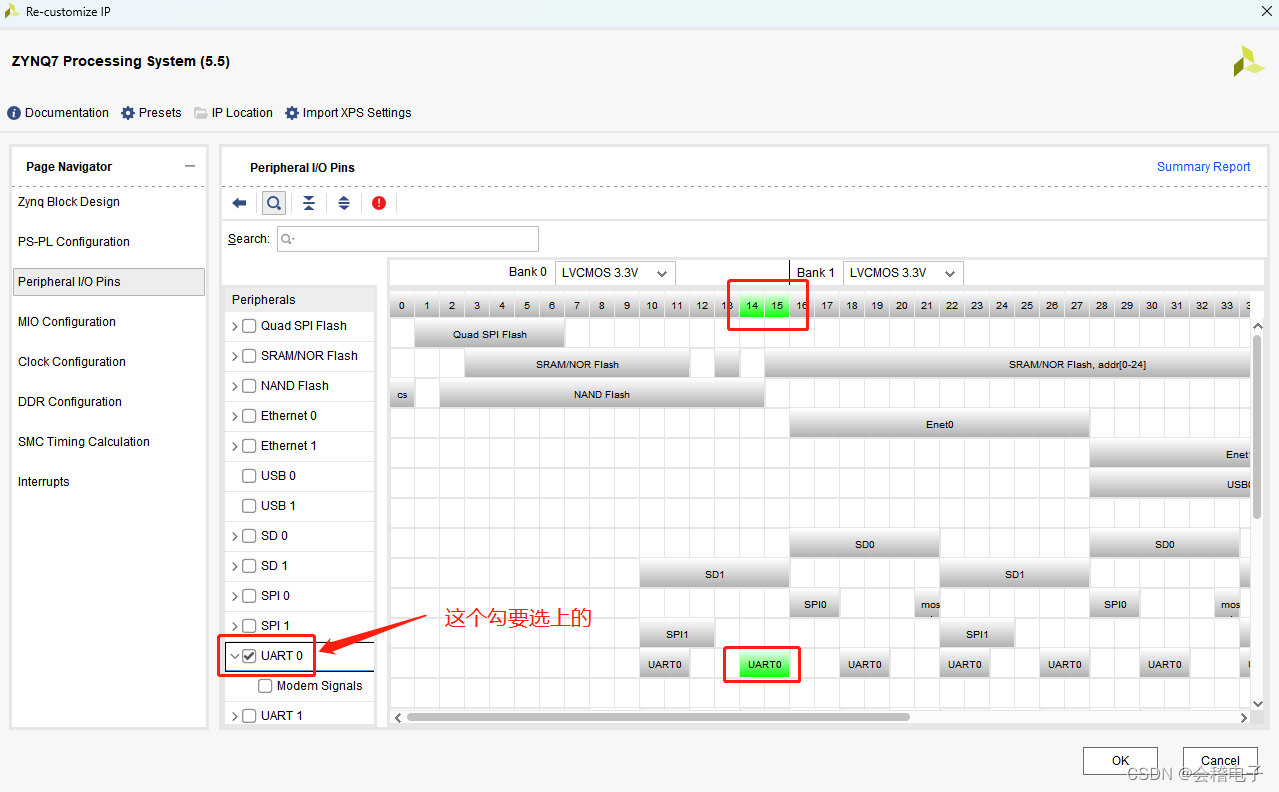

15、配置UART,因为我们要打印“hello world”,就需要配置串口了,我的核心板使用的是UART0,管脚使用的是MIO14和MIO15

16、再回过头去看Peripheral I/O Pins栏,就发现UART0选中的引脚变绿了

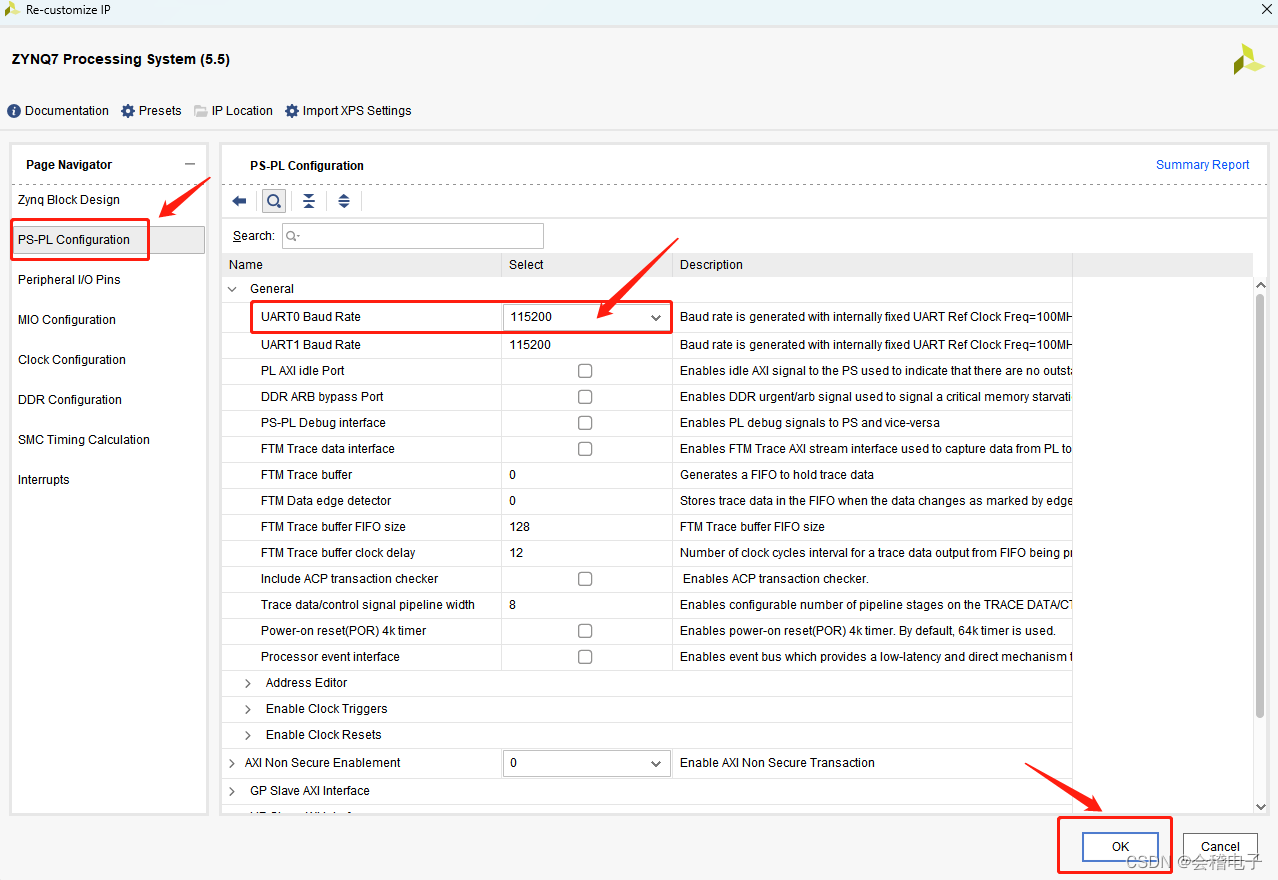

17、接下来配置UART0 的波特率,点击PS-PL Configuration,在General 栏下设置波特率,笔者使用的是115200,也可以通过下拉菜单选择其他的波特率

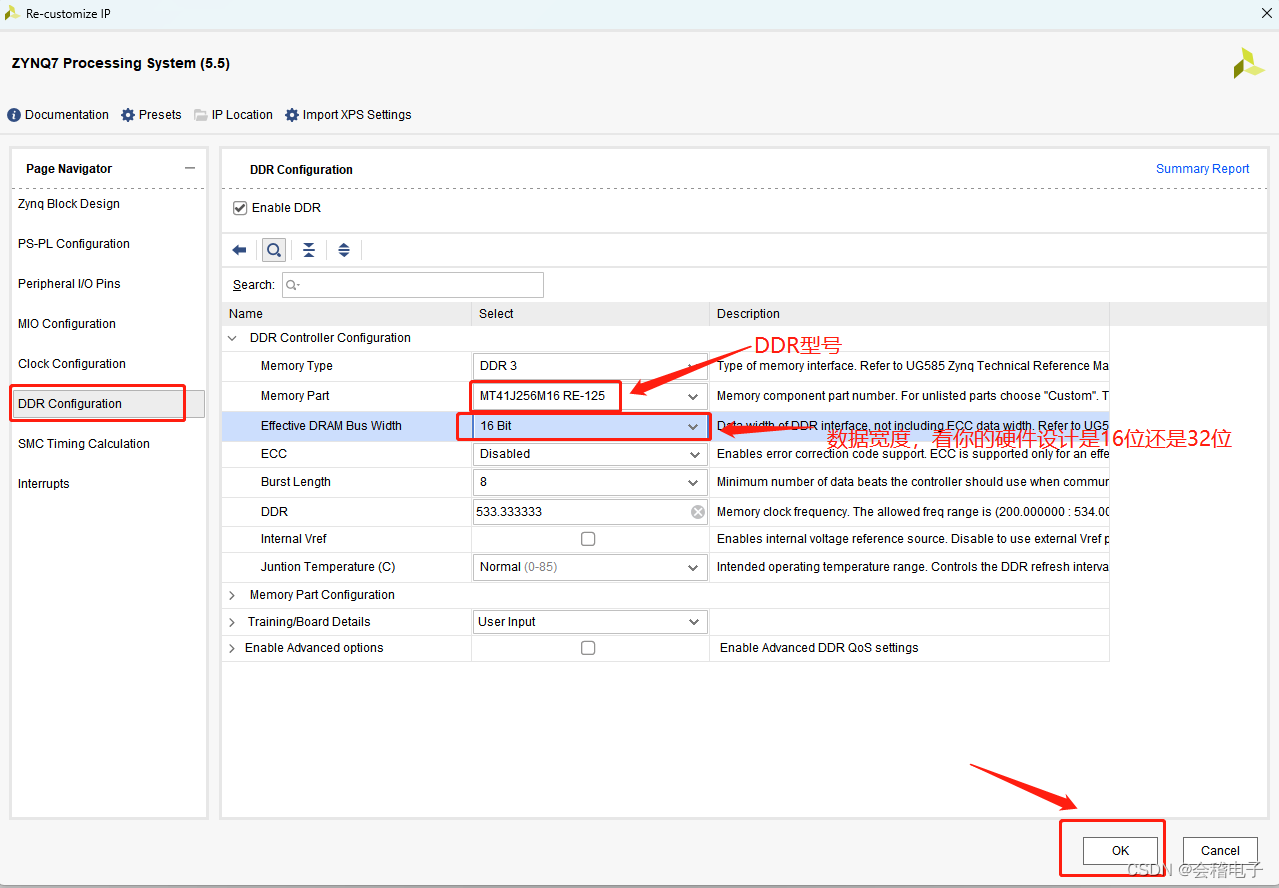

18、ZYNQ的最小系统需要一个DDR,看你的硬件用的是什么DDR就选哪个,在DDR Configuration栏去配置,注意数据宽度,硬件上设计的是多少就选多少16bit和32bit可选。没配置完就不要点OK哈,配置完了再点OK。

19、配置PS的时钟,点击Clock Configuration 栏进行配置,没什么特殊情况就用默认的配置吧。

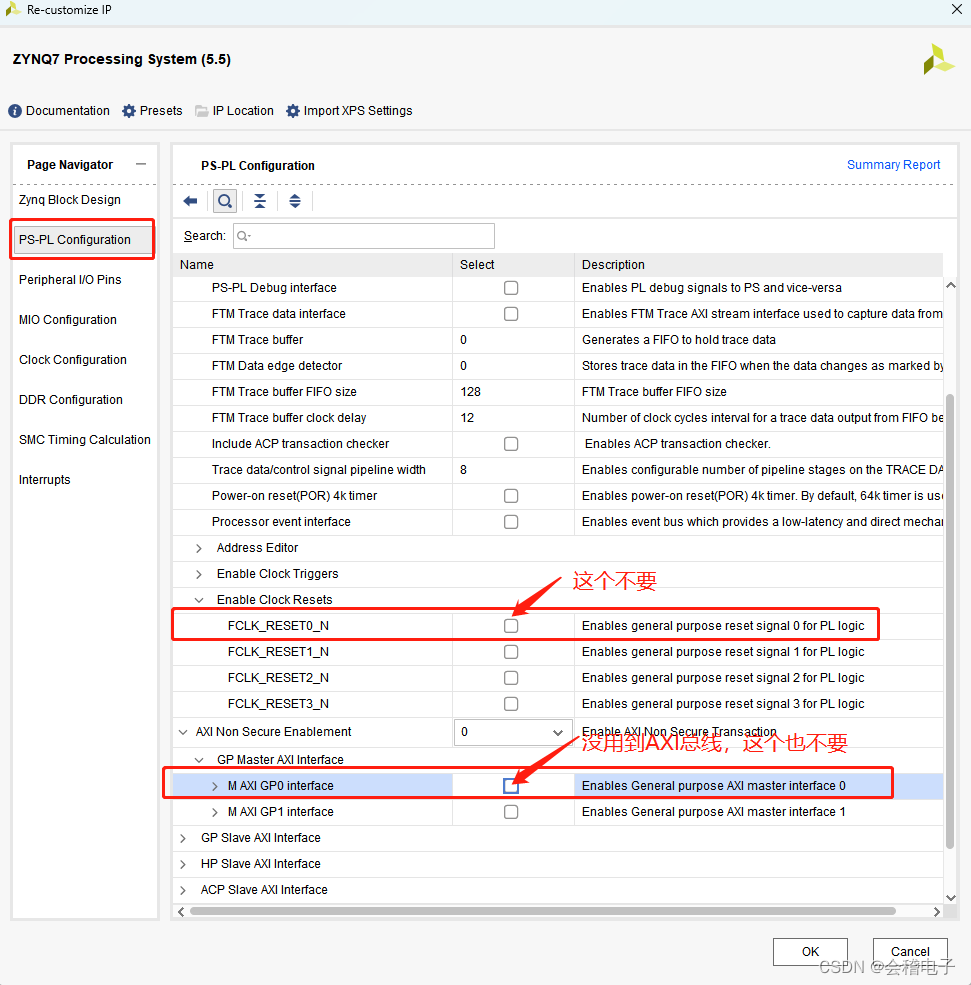

20、上面那步PL的时钟掐的还不彻底,需要在PS-PS Configuration栏继续掐。配置完就可以点OK了。

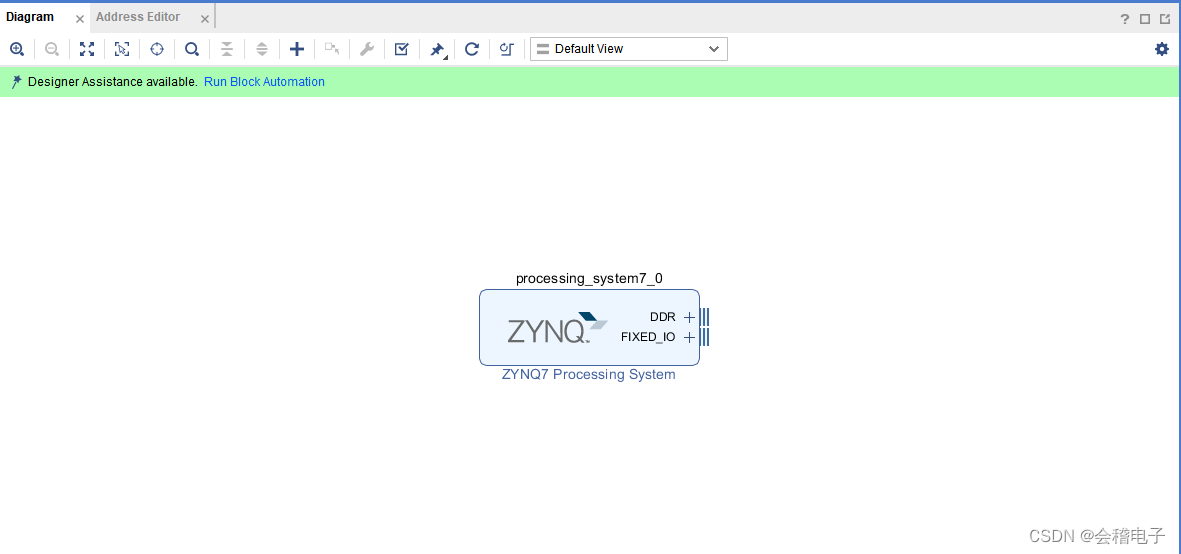

21、配置完的ZYNQ IP就变得光秃秃的没什么东西了

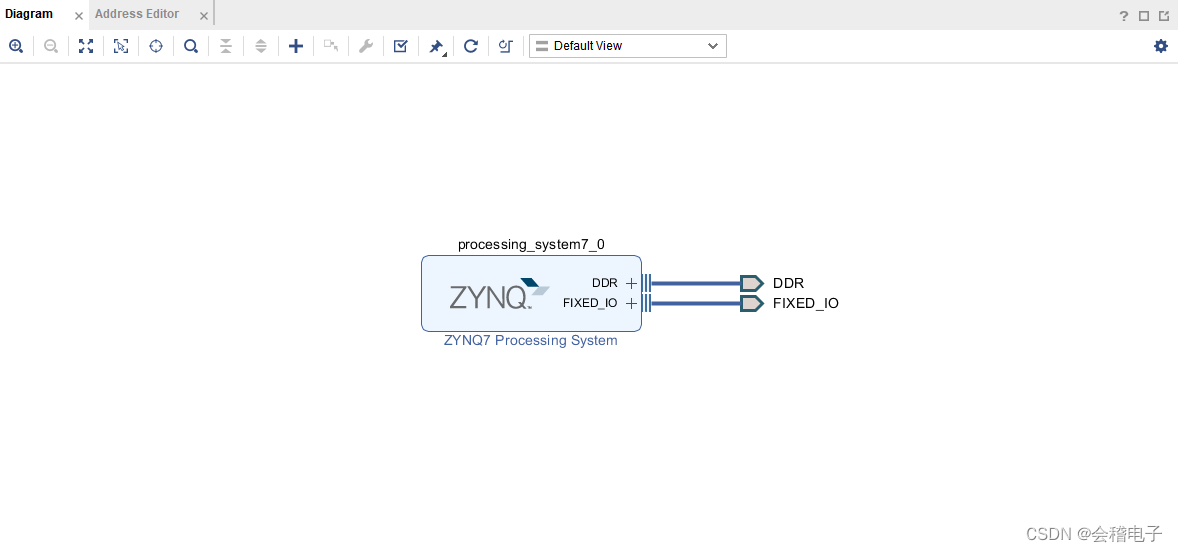

22、点击Run Block Automation,让你的设计生效

23、在弹窗中点击OK,自动连接IP的接口

24、所谓的自动连接端口就是这面这样,相当于DDR和一些固定的IO口与外设连上了。

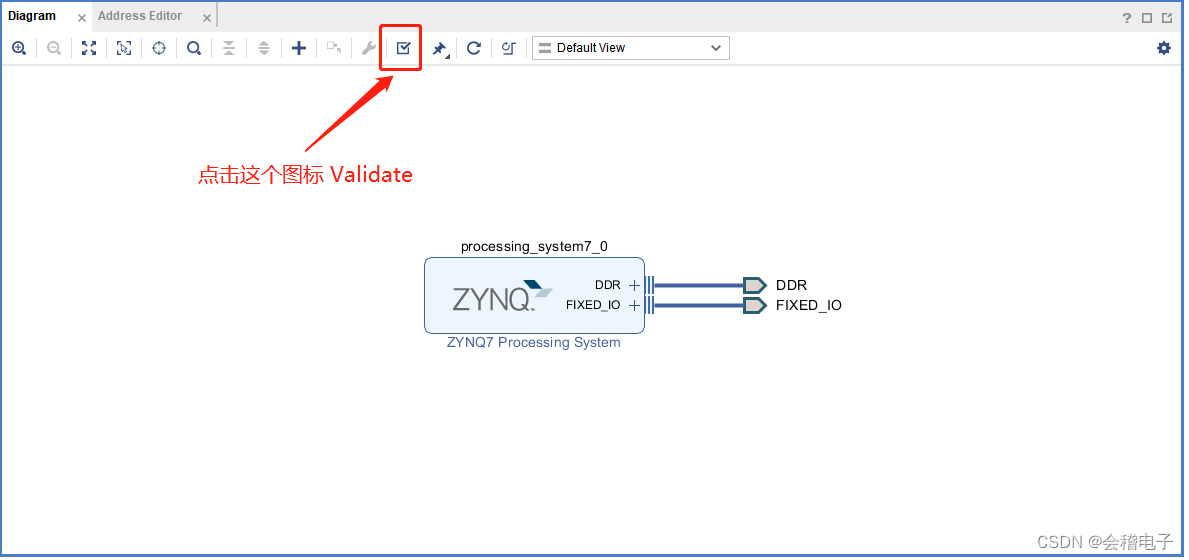

/25、 Ctrl + S保存之后,点击Validate 图标,验证一下有没有问题

26、一般情况是没什么问题的,有问题的话那就重新来过

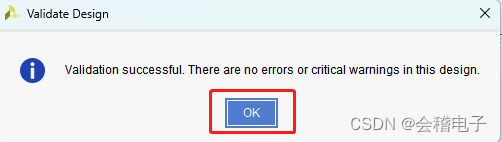

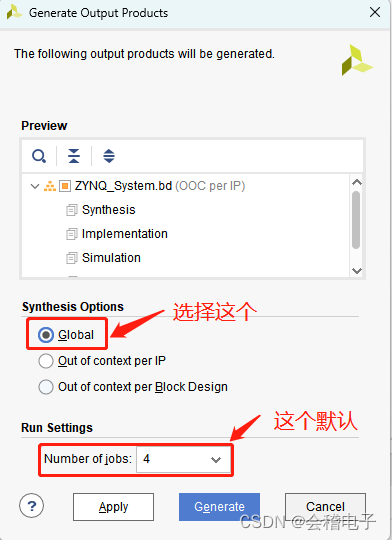

27、点击Block Design 下面的Sources栏,选择那个.bd文件,右击,选择Generate Output Products

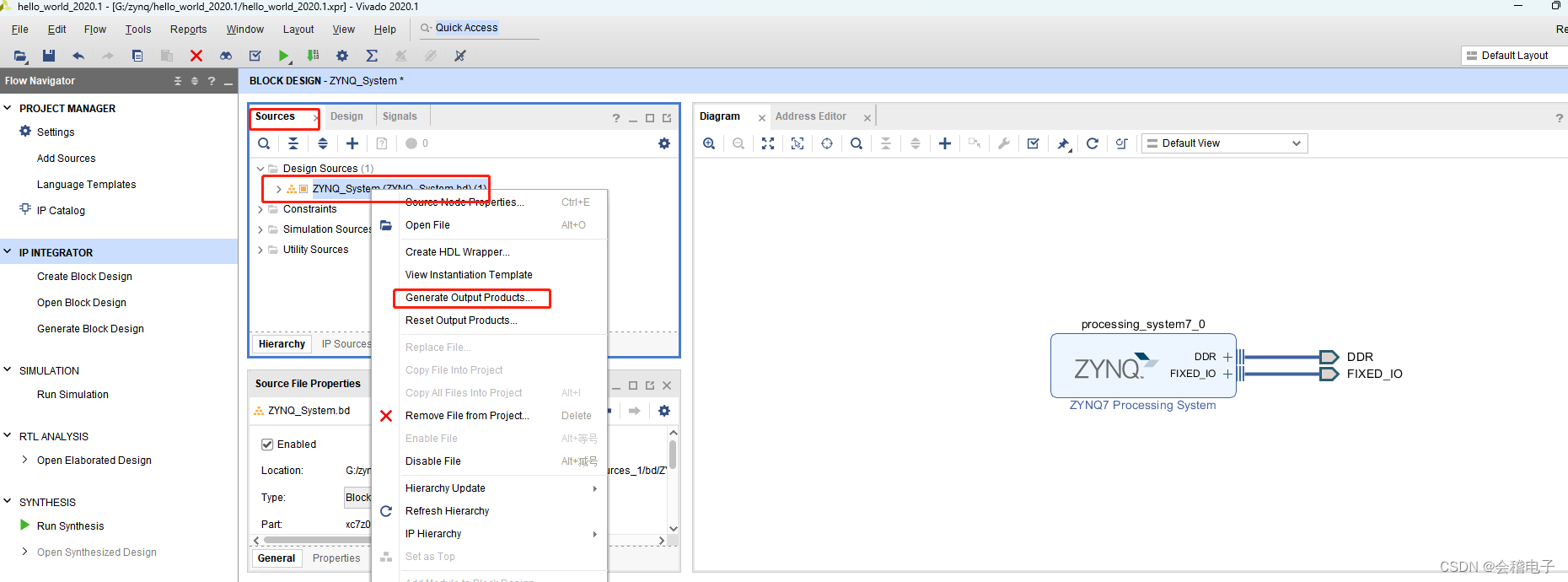

28、在弹窗中选中Global,其他默认,点击Generate

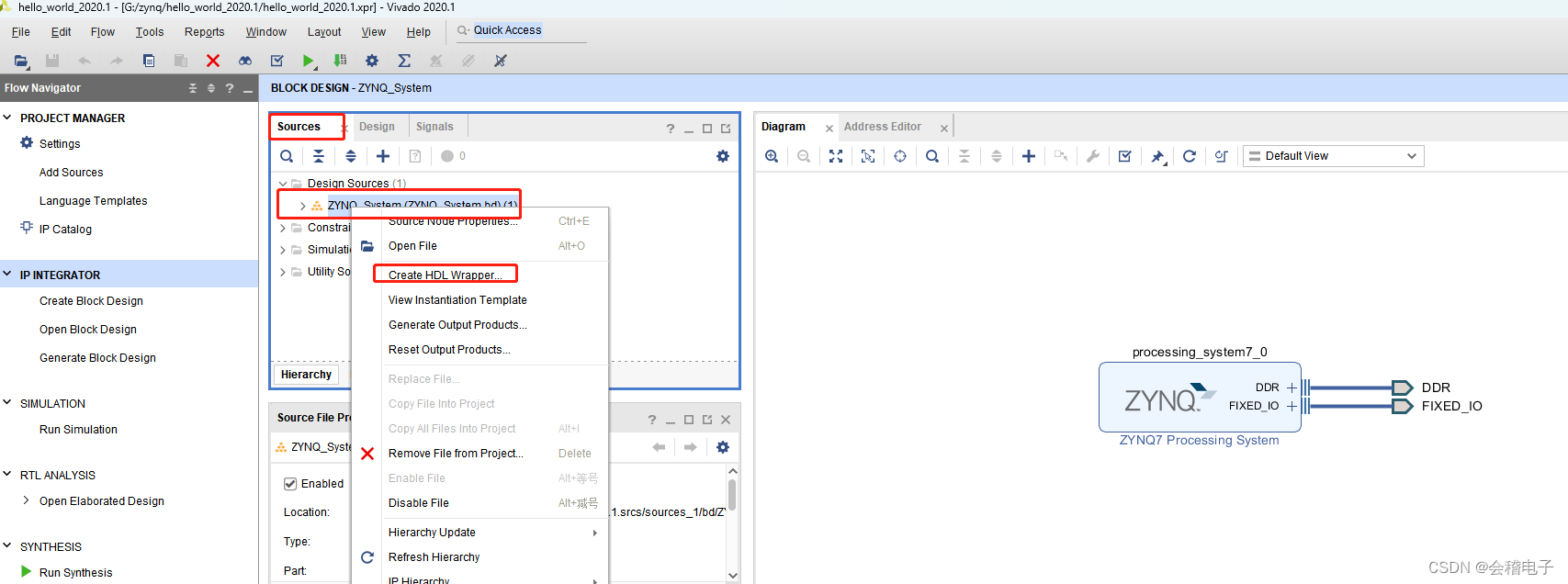

29、再右击这个.bd文件,选择Create HDL Wrapper...

30、在弹窗中选择自动更新

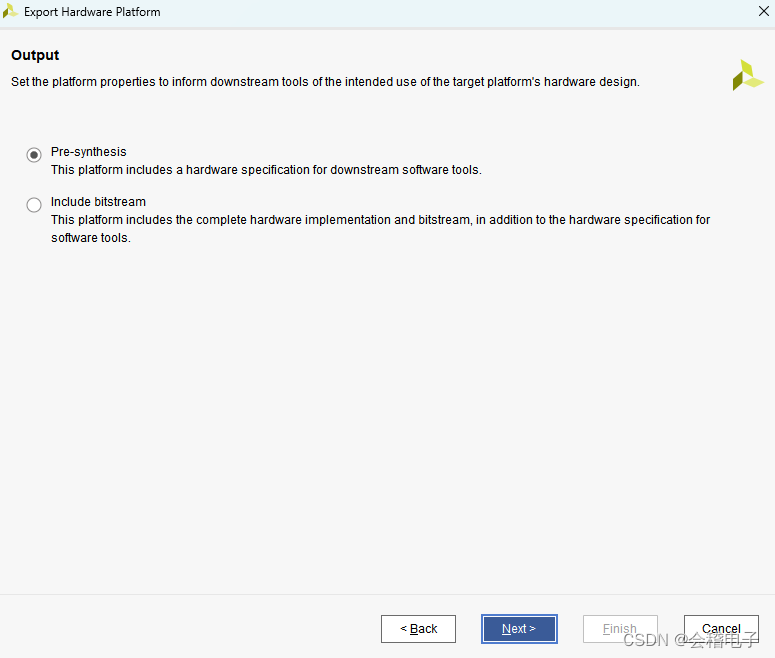

31、导出硬件,因为没有用到PL的资源,就不用生成比特流,点击file--Export--ExportHardware...

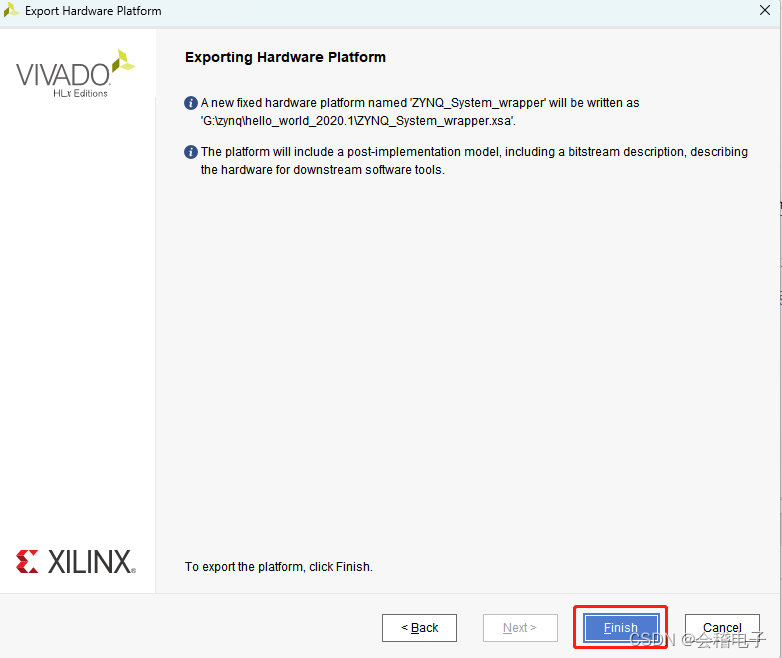

32、弹窗中选择Fixed,Next

33、启动vitis IDE,相当于老版本的SDK

34、弹窗默认就行了,想改路径的自己改在好找的位置

35、弹出下面的界面

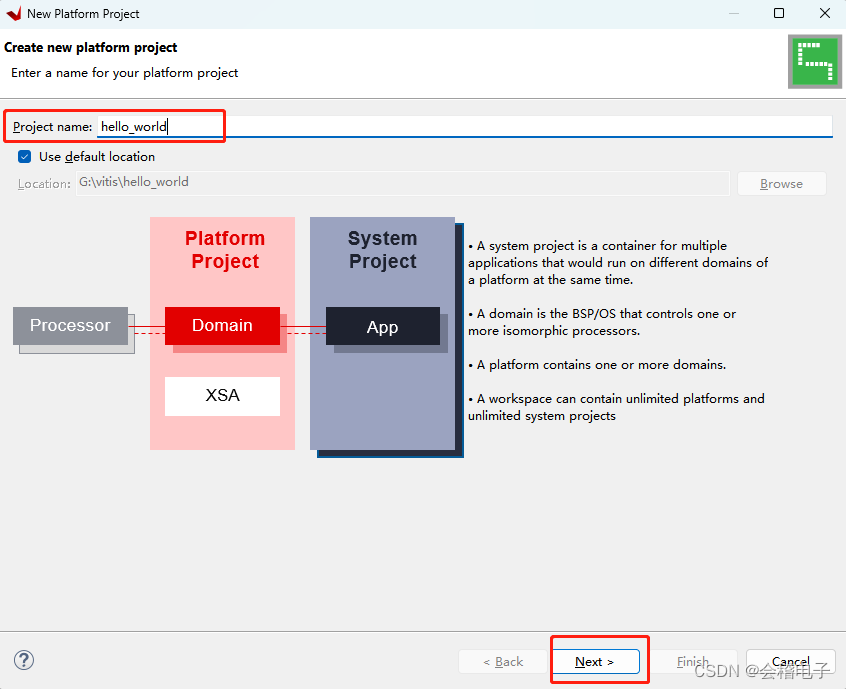

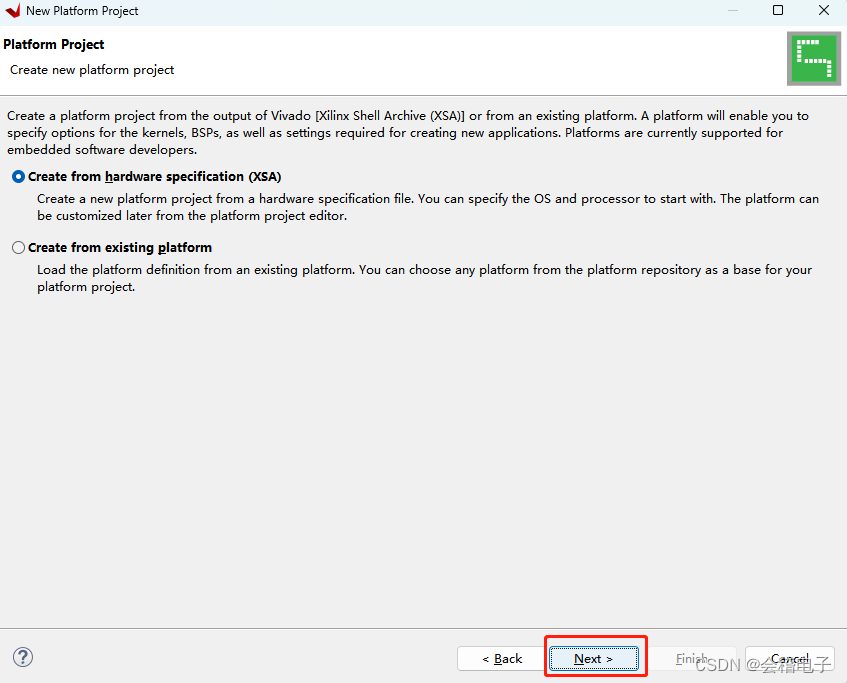

36、创建一个platform project,导入前面的设计

37、在弹窗中修改一下工程名称

38、点击finish,界面就变成这样了

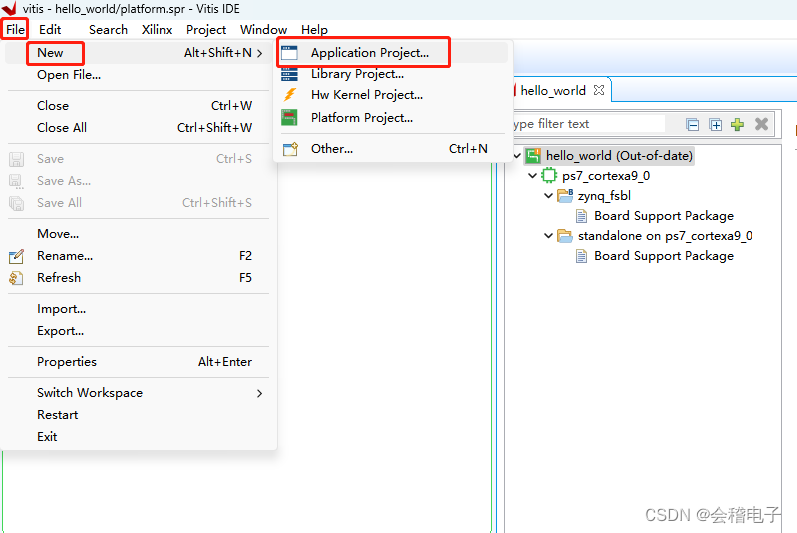

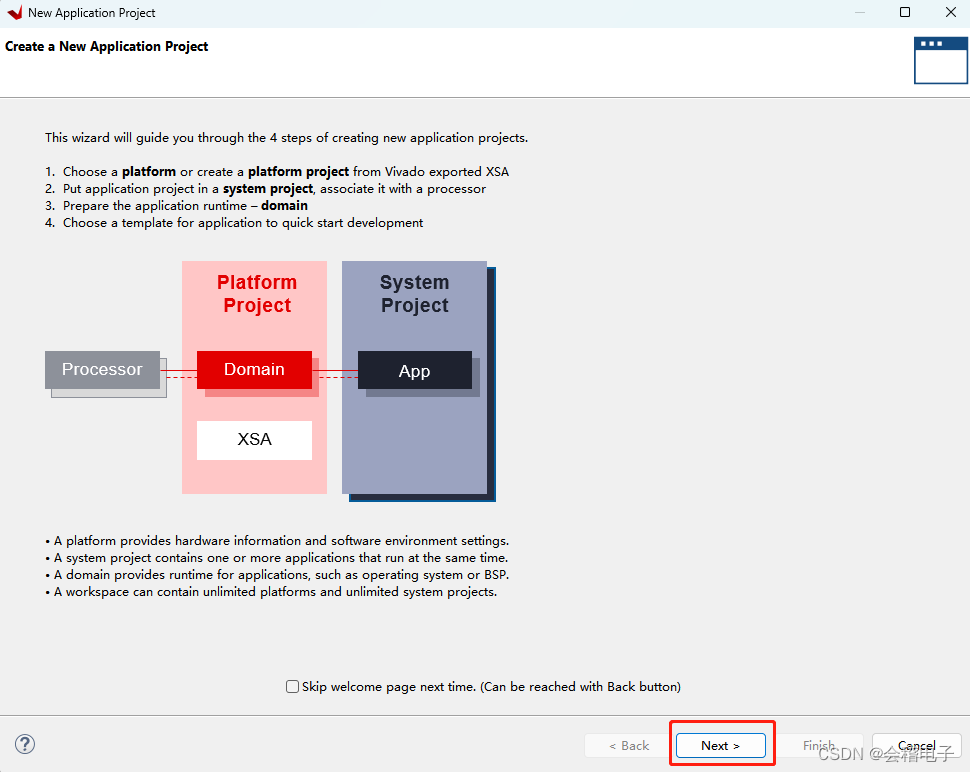

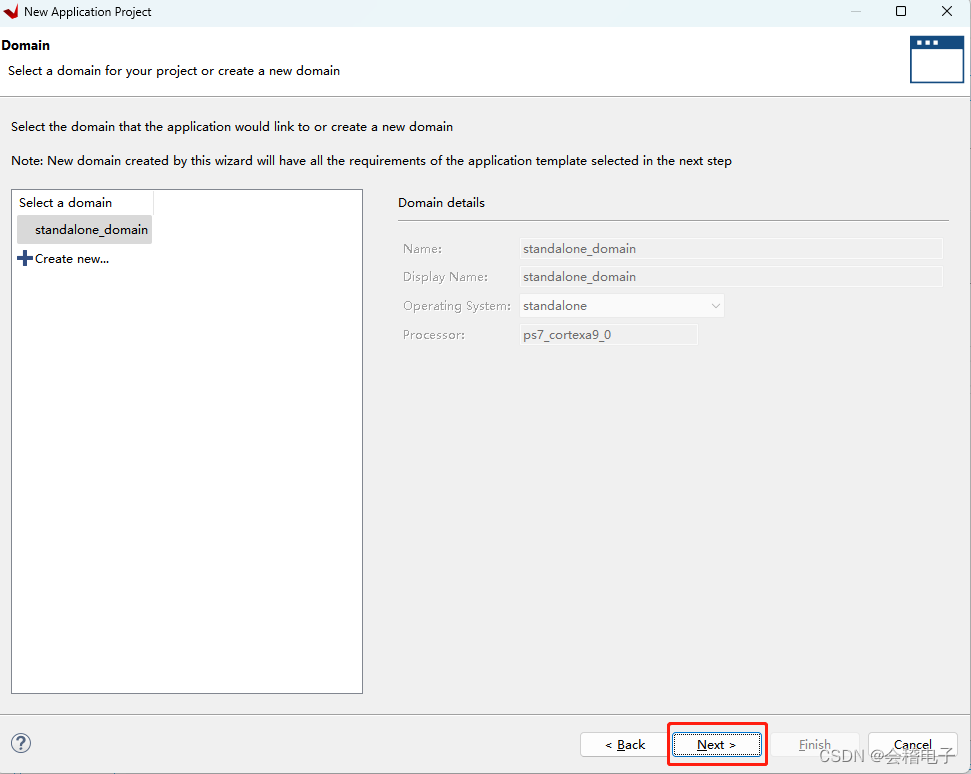

39、创建一个Application project

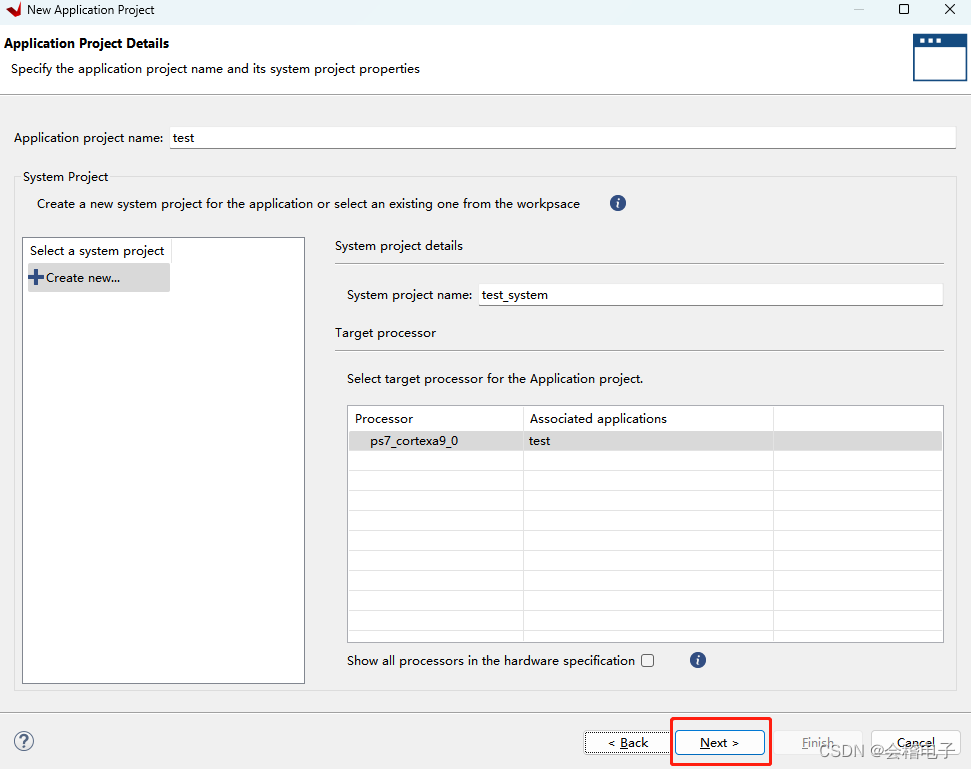

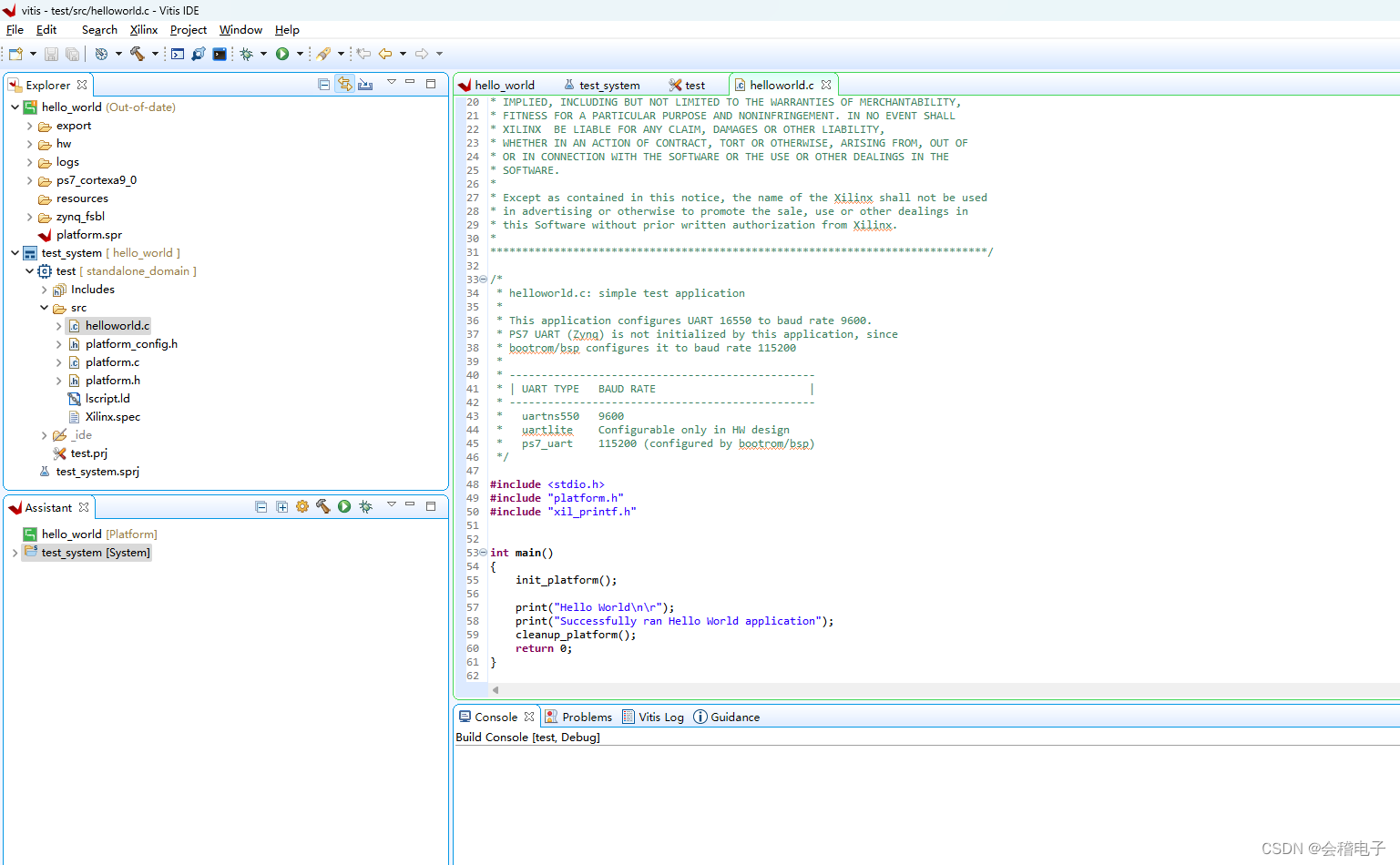

40、工程名称改为test

41、终于把这个hello_world建好了

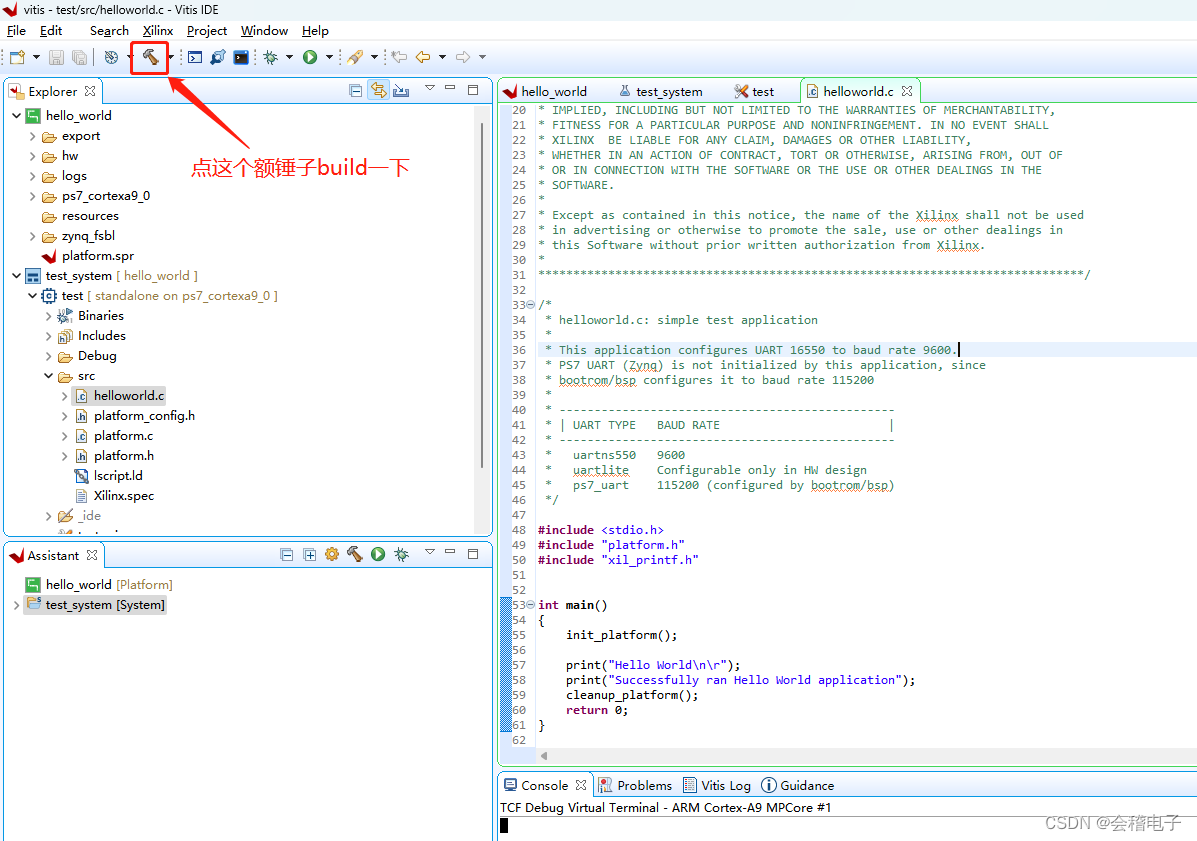

42、编译一下工程

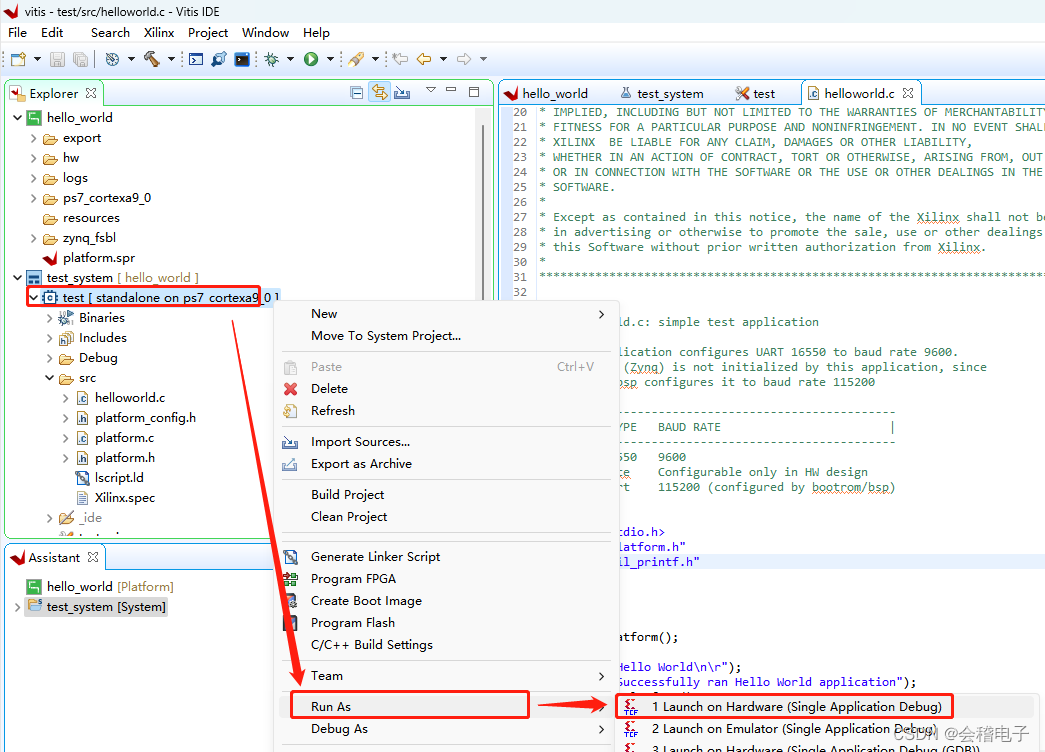

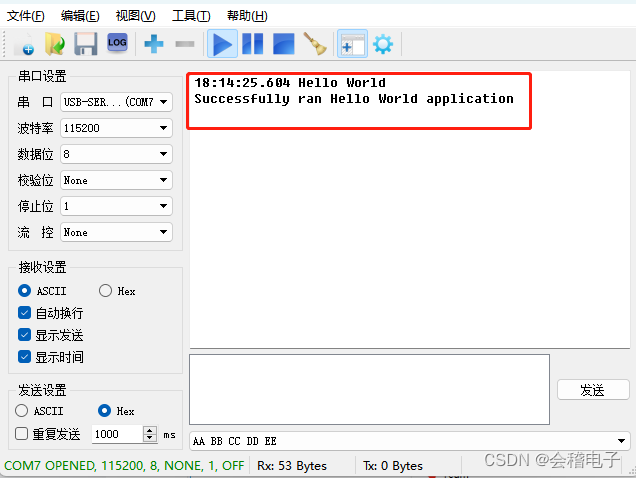

43、下载运行

44、得有个串口调试助手看看效果

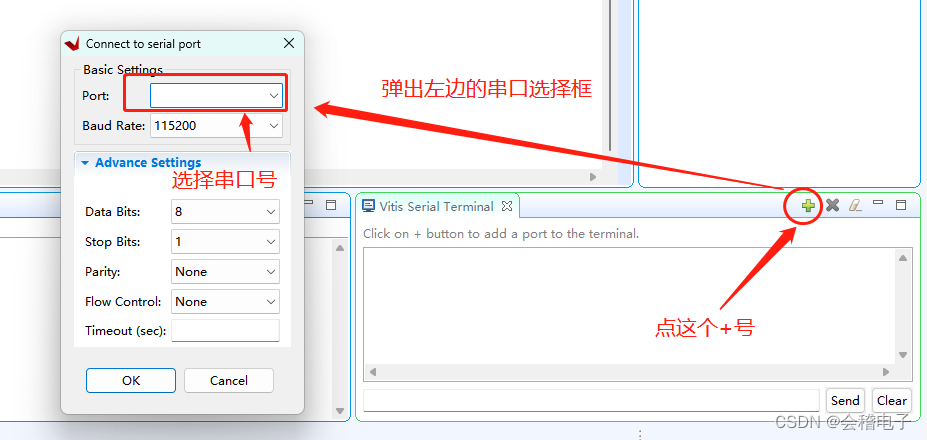

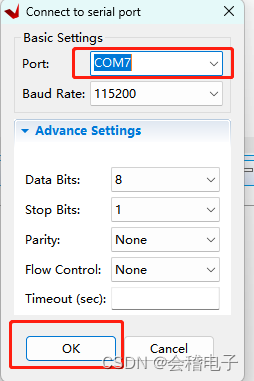

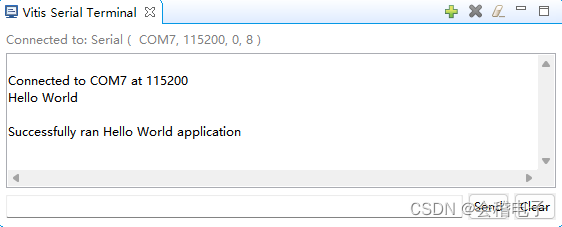

45,当然,也可以用vitis软件自带的terminal

点Windows--show view,在搜索栏输入terminal,选择Vitis Serial Terminal

终于一个最简单的项目搞完了,ZYNQ的门槛比单片机还是高一些,不是有多难,而是这个工具的步骤太多了。撇开PL部分,也就是FPGA部分,PS部分就可以当做一个单片机来操作了。