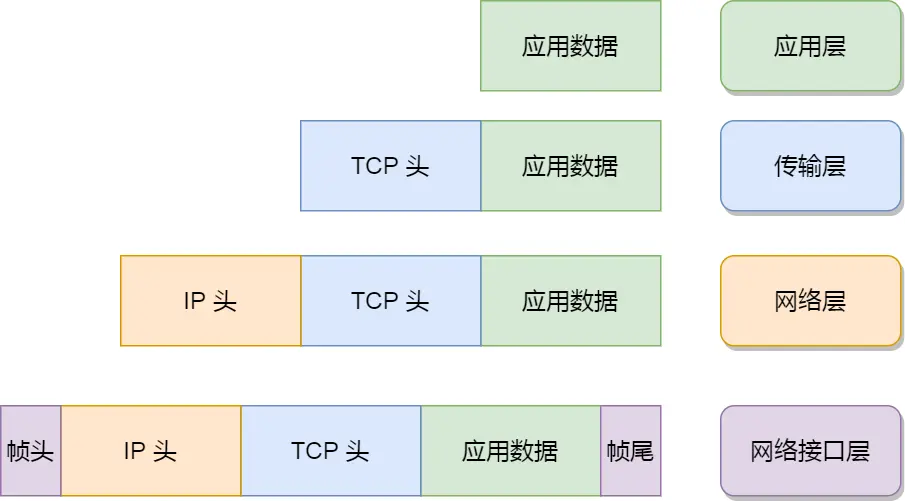

8.1About Physical Constraints(关于物理约束)

Xilinx®Vivado®集成设计环境(IDE)允许通过设置对象属性值对设计对象进行物理约束。示例包括:

•I/O约束,如位置和I/O标准

•布局约束,如单元位置

•布线约束,如固定布线

•配置约束,如配置模式

与时序约束类似,物理约束必须保存在Xilinx设计约束(XDC)文件或Tcl脚本中,以便在打开设计时可以与网表一起加载。将设计加载到内存中后,可以使用Tcl控制台或使用Vivado design Suite IDE编辑工具以交互方式输入新的约束。大多数物理约束是通过对象上的特性来定义的:

set_property <property> <value> <object list>使用Pblock命令的区域约束除外。

8.1.1 Critical Warning(严重警告)

对于XDC文件中的无效约束,包括应用于设计中找不到的对象的约束,会发出严重警告。有关属性定义和用法,请参阅《Vivado Design Suite Properties Reference Guide》 (UG912).。

建议:Xilinx强烈建议您查看所有关键警告,以确保设计受到适当约束。无效的约束在交互应用时会导致错误。

8.2Netlist Constraints(网表约束)

网表约束是在网表对象(如ports, pins, nets 或者cells)上设置的,需要综合和实现才能以特殊方式处理它们。

重要:请确保了解使用这些约束的影响。它们可能会增加设计面积,降低设计性能,或者两者兼而有之。

网表约束包括:

• CLOCK_DEDICATED_ROUTE

• MARK_DEBUG

• DONT_TOUCH

• LOCK_PINS

8.2.1CLOCK_DEDICATED_ROUTE

在网络上设置CLOCK_DEDICATED_ROUTE,以指示时钟信号的路由方式。

CLOCK_DEDICATED_ROUTE属性在时钟网络上用于覆盖默认路由。这是一种高级控制,需要格外小心,因为它可能会影响时间的可预测性和可调度性。

例如,当专用时钟路由不可用时,CLOCK_DEDICATED_ROUTE可以设置为FALSE。

值FALSE允许Vivado工具使用通用路由资源将时钟从输入端口路由到全局时钟资源,如BUFG或MMCM。只有当设备封装引脚分配被锁定,并且时钟输入无法分配给适当的具有时钟功能的输入引脚(CCIO)时,才应将其作为最后手段。除非与FIXED_ROUTE一起使用,否则路由将是次优且不可预测的。有关此属性的更多信息,请参阅《UltraFast Design Methodology Guide for FPGAs and SOCs 》(UG949)中的时钟约束。

8.2.2 MARK_DEBUG

它可以在编译流中的任何点连接到逻辑调试工具。有关更多信息,请参阅 Vivado Design Suite User Guide: Programming and Debugging (UG908).

8.2.3 DONT_TOUCH

在叶单元、分层单元或网络对象上设置DONT_TOUCH,以便在网表优化期间保留它。

DONT_TOUCH最常用于:

•防止网络被优化掉。具有DONT_TOUCH的网络不能通过综合或实现来吸收。这有助于逻辑探测或调试设计中的意外优化。要保留具有多个层次分段的网络,请将DONT_TOUCH放置在最靠近其驱动的网络分段的网络PARENT(get_property PARENT$net)上。

•防止合并手动复制的逻辑。有时最好手动复制逻辑,例如跨大区域的高扇出驱动程序。将DONT_TOUCH添加到手动复制的驱动(以及原始驱动)会阻止综合和实现优化这些单元。

注意:使用reset_property可重置DONT_TOUCH属性。将DONT_TOUCH属性设置为0不会重置该属性。

提示:避免在分层单元上使用DONT_TOUCH进行实现,因为Vivado IDE实现不会使逻辑分层变平。在综合中使用KEEP_HIERARCHY来维护应用XDC约束的逻辑层次结构。

8.2.4 LOCK_PINS

LOCK_PINS是一个单元属性,用于指定逻辑LUT输入(I0、I1、I2…)和LUT物理输入引脚(A6、A5、A4…)之间的映射。常见的用途是强制将时序关键LUT输入映射到最快的A6和A5物理LUT输入。

8.2.4.1LOCK_PINS Constraint Example One(LOCK_PINS约束示例一)

将I1映射到A6,将I0映射到A5(交换默认映射)。

% set myLUT2 [get_cells u0/u1/i_365]

% set_property LOCK_PINS {I0:A5 I1:A6} $myLUT2

# Which you can verify by typing the following line in the Tcl Console:

% get_property LOCK_PINS $myLUT28.2.4.2LOCK_PINS Constraint Example Two(LOCK_PINS约束示例二)

对于LUT6映射I0到A6,I1到I5的映射无关紧要。

% set_property LOCK_PINS I0:A6 [get_cell u0/u1/i_768]8.2.3 I/O Constraints(IO约束)

I/O约束配置:

•端口

•连接到端口的单元典型约束包括:

•I/O标准

•I/O位置

Vivado设计套件支持许多与集成软件环境(ISE)设计套件相同的I/O约束。以下I/O属性列表并非详尽无遗。

•有关I/O属性的完整列表、有关I/O端口和I/O单元属性的更多信息以及正确语法的编码示例,请参阅Vivado Design Suite properties Reference Guide(UG912)。注意:除非另有说明,否则所有属性都应用于端口对象。

•有关这些属性背后的应用程序和方法的更多信息,请参阅设备SelectIO™文档,例如7 Series FPGAs SelectIO Resources User Guide (UG471)。

•DRIVE:设置输出缓冲区驱动强度(mA),仅适用于某些I/O标准。

•IOSTANDARD:设置I/O标准。

•SLEW:设置设备输出的转换速率(转换速率)行为。

•IN_TERM:设置输入端口的输入端接电阻的配置。

•DIFF_TERM:打开或关闭IBUFDS_DIFF_OUT等原语的100欧姆差分终端。

•KEEPER:在三态输出或双向端口上应用弱驱动程序,以在不驱动时保持其值。

•PULLTYPE:在三态输出或双向端口上应用弱逻辑低电平或高电平,以防止其浮动。

•DCI_CASCADE:定义一组主库和从库。DCI参考电压从主存储器组链接到从存储器组。在IOBANK对象上设置DCI_CASACDE。

•INTERNAL_VREF:释放I/O组的VREF引脚,转而使用内部生成的VREF。在IOBANK对象上设置INTERNAL_VREF

•IODELAY_GROUP:使用IDELAYCTRL将一组IDELAY和IODELAY单元分组,以实现IDELAYCTRL在设计中的自动复制和放置。

•IOB:告诉放置者尝试将FF放在I/O逻辑中,而不是放在结构切片中。此属性必须分配给寄存器,而不是分配给端口。

重要:ISE设计套件和Vivado设计套件在IOB处理方面存在显著差异。Vivado工具允许在端口和连接到端口的寄存器单元上设置IOB。如果在端口及其寄存器上设置了冲突的值,则以寄存器上的值为准。Vivado工具仅使用TRUE和FALSE值。值FORCE被解释为TRUE,而值AUTO被忽略。

与ISE不同,如果不能遵守IOB true的设置,Vivado工具会生成严重警告,而不是错误。

•IOB_TRI_REG:用于UltraScale中的HDIO+™ 设备。告诉放置者尝试将驱动三态信号的FF放在I/O逻辑中的HDIO组IOB上,而不是放在结构片上。此属性必须分配给寄存器,而不是分配给端口。

8.4 Placement Constraints(布局约束)

将布局约束应用于单元,以控制它们在设备中的位置。Vivado集成设计环境(IDE)支持许多与集成软件环境(ISE)设计套件和Integrated Software Environment (ISE) Design Suite and the PlanAhead™ 工具。

•LUTNM:应用于两个LUT的唯一字符串名称,以控制它们在单个LUT站点上的位置。与HLUTNM不同,LUTNM可以用于组合属于不同层次单元的LUT。

•HLUTNM:应用于同一层次结构中的两个LUT的唯一字符串名称,以控制它们在单个LUT站点上的位置。在多次实例化的单元中使用HLUTNM。

•PROHIBIT:禁止放置在站点。

•PBLOCK:连接到逻辑块,将它们约束到设备中的物理区域。PBLOCK是一个只读单元属性,是为其分配单元的PBLOCK的名称。只有使用XDC Tcl命令add_cells_to_Pblock和remove_cells_from_block才能更改Cell Pblock成员身份。

•PACKAGE_PIN:指定目标设备包引脚上设计端口的位置。

•LOC:将一个逻辑元素从网表中放置到设备上的一个位置。

•BEL:将网表中的逻辑元素放置到设备切片内的特定BEL。

8.4 .1Placement Types

工具中有两种类型的布局:

•固定布局(Fixed Placement)

•未固定布局(Unfixed Placement)

固定布局

固定布局是用户通过以下操作之一指定的布局:

•手动布局

•XDC约束

•在内存中加载的设计单元对象上使用IS_LOC_FIXED或IS_BEL_FIXED。

未固定的布局(Unfixed Placement)

非固定布局是由实施工具执行的布局。通过将布局设置为固定,实现无法在下一次迭代或增量运行期间移动受约束的单元。固定位置保存在XDC文件中,在该文件中显示为简单的LOC或BEL约束。

•IS_LOC_FIXED:将LOC约束从未固定提升为固定。

•IS_BEL_FIXED:将BEL约束从未固定提升为固定。

8.4 .2Placement Constraint Examples(布局约束示例)

8.4 .2.1(布局约束示例1)

将块RAM定位在RAMB18_X0Y10并固定其位置。

% set_property LOC RAMB18_X0Y10 [get_cells u_ctrl0/ram0]8.4 .2.2(布局约束示例2)

将LUT放置在切片内的C5LUT BEL位置,并固定其BEL分配。

% set_property BEL C5LUT [get_cells u_ctrl0/lut0]8.4 .2.3(布局约束示例3)

将输入总线寄存器定位在ILOGIC单元中,以缩短输入延迟。

% set_property IOB TRUE [get_cells mData_reg*]8.4 .2.4(布局约束示例4)

将两个小LUT组合为一个LUT6_2,该LUT6_2同时使用O5和O6输出。

% set_property LUTNM L0 [get_cells {u_ctrl0/dmux0 u_ctrl0/dmux1}]8.4 .2.5(布局约束示例5)

防止布局器使用块RAM的第一列。

% set_property PROHIBIT TRUE [get_sites {RAMB18_X0Y* RAMB36_X0Y*}]8.4 .2.6(布局约束示例6)

防止布局器使用时钟区域X0Y0。

% set_property PROHIBIT TRUE [get_sites -of [get_clock_regions X0Y0]]8.4 .2.7(布局约束示例7)

防止布局器使用SLR0。

% set_property PROHIBIT TRUE [get_sites -of [get_slrs SLR0]]重要:将BEL和LOC属性同时指定给单元时,必须在LOC之前指定BEL。

8.5Routing Constraints(布线约束)

布线约束应用于网络对象,以控制其布线资源。

8.5.1 Fixed Routing(固定布线)

固定布线是锁定布线的机制,类似于ISE中的定向布线。锁定网络布线资源涉及三个网络属性。见下表。

表10:网络属性

| 属性 | 功能 |

| ROUTE | 只读网络 属性 |

| IS_ROUTE_FIXED | 标记整个布线为固定布线的标志 |

| FIXED_ROUTE | 网络的固定布线部分 |

为了保证网络布线可以固定,它的所有单元也必须事先固定。

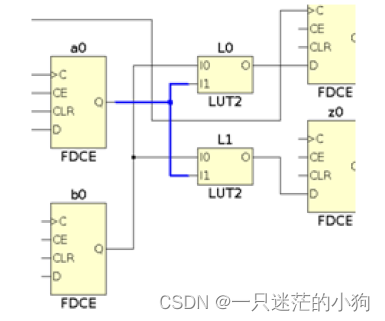

以下是一个完全固定布线的示例。该示例采用下图中的设计,并创建约束来固定netA(蓝色选中)的路由。

图95:图解布线约束的简单设计

在内存中加载已实现的设计后,可以查询任何网络的路由信息:

% set net [get_nets netA]

% get_property ROUTE $net

{ CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5 FAN_BOUNCE5 { IMUX_L17

CLBLL_LL_B3 } IMUX_L11 CLBLL_LL_A4 }路由被定义为一系列相对的路由节点名称,扇出使用嵌入式大括号表示。路由是通过在网络上设置以下属性来固定的:

% set_property IS_ROUTE_FIXED TRUE $net要在XDC文件中对约束进行反向注释以供将来运行,还必须保留连接到固定网络的所有单元的位置。可以通过在原理图或设备视图中选择单元来查询此信息,并在“Properties ”窗口中查看它们的LOC/BEL属性值。或者,您可以直接从Tcl控制台查询这些值:

% get_property LOC [get_cells {a0 L0 L1}] SLICE_X0Y47 SLICE_X0Y47

SLICE_X0Y47

% get_property BEL [get_cells {a0 L0 L1}] SLICEL.CFF SLICEL.A6LUT

SLICEL.B6LUT由于固定布线通常是定时关键的,因此还必须在LUT的LOCK_pins属性中捕获LUT引脚映射,以防止路由器交换引脚。同样,您可以从Tcl控制台查询每个逻辑引脚的站点引脚:

% get_site_pins -of [get_pins {L0/I1 L0/I0}] SLICE_X0Y47/A4 SLICE_X0Y47/A2

% get_site_pins -of [get_pins {L1/I1 L1/I0}] SLICE_X0Y47/B3 SLICE_X0Y47/B2修复netA路由所需的完整XDC约束包括:

set_property BEL CFF [get_cells a0] set_property BEL A6LUT [get_cells L0]

set_property BEL B6LUT [get_cells L1]

set_property LOC SLICE_X0Y47 [get_cells {a0 L0 L1}] set_property LOCK_PINS

{I1:A4 I0:A2} [get_cells L0] set_property LOCK_PINS {I1:A3 I0:A2}

[get_cells L1]

set_property FIXED_ROUTE { CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5

FAN_BOUNCE5 {

IMUX_L17 CLBLL_LL_B3 } IMUX_L11 CLBLL_LL_A4 } [get_nets netA]如果使用交互式Tcl命令而不是XDC,则可以使用place_cell命令同时指定多个放置约束,如下所示:

place_cell a0 SLICE_X0Y47/CFF L0 SLICE_X0Y47/A6LUT L1 SLICE_X0Y47/B6LUT有关place_cell的更多信息,请参阅Vivado Design Suite Tcl Command Reference Guide (UG835)。

8.6 Configuration Constraints(配置约束)

配置约束是应用于当前设计的比特流生成的全局约束。这包括诸如配置模式之类的约束。

8.6.1配置约束示例1

将CONFIG_MODE设置为M_SELECTMAP。

% set_property CONFIG_MODE M_SELECTMAP [current_design]8.6.2配置约束示例2

打开调试比特流。

% set_property BITSTREAM.GENERAL.DEBUGBITSTREAM Yes [current_design]8.6.3配置约束示例3

禁用CRC检查。

% set_property BITSTREAM.GENERAL.CRC Disable [current_design] 有关比特流生成属性和定义的列表,请参阅Vivado Design中的此链接Suite User Guide: Programming and Debugging (UG908).