NEORV32是一个高度可定制的RISC-V软核,由VHDL语言实现,后有人以Verilog实现。由于军工、航天部门较多选用VHDL,所以理论上NEORV32是非常稳定可靠的。NEORV32的资料非常详尽(英文),Github上的更新也非常及时。另外,其支持OpenOCD、BootLoader,资料很全。此外,作者Stephan Nolting还完成了一个NEO430项目,即在FPGA实现msp430。

GitHub - stnolting/neorv32: 🖥️ A tiny, customizable and highly extensible MCU-class 32-bit RISC-V soft-core CPU and microcontroller-like SoC written in platform-independent VHDL.

GitHub - stnolting/neorv32-verilog: ♻️ Convert the NEORV32 processor into a synthesizable plain-Verilog netlist module using GHDL.

GitHub - stnolting/neo430: A damn small msp430-compatible customizable soft-core microcontroller-like processor system written in platform-independent VHDL.

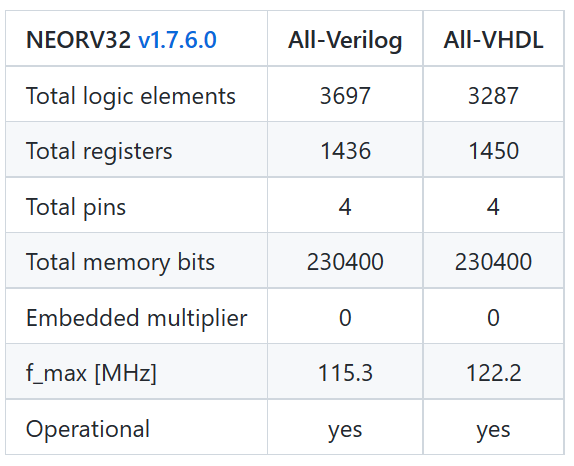

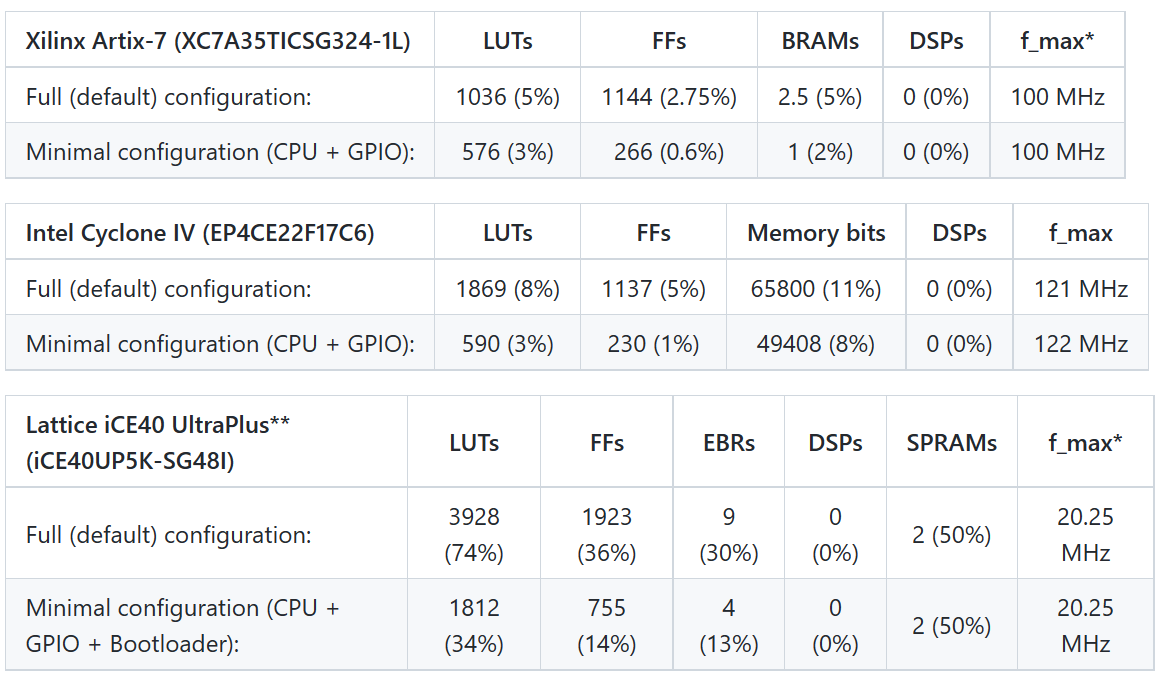

1.资源占用

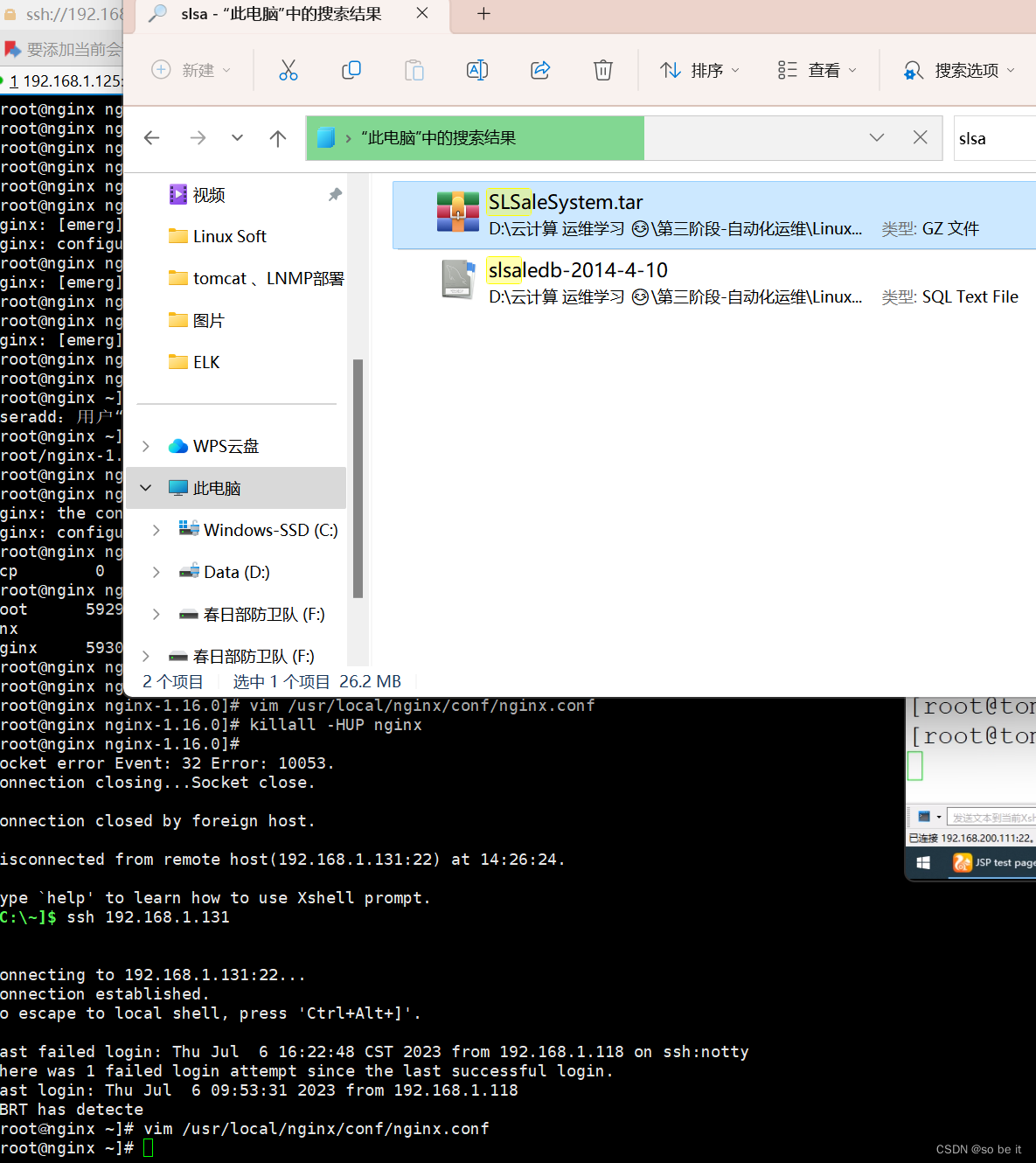

1)EP4CE22F17C6,Quartus Prime Lite 21.1

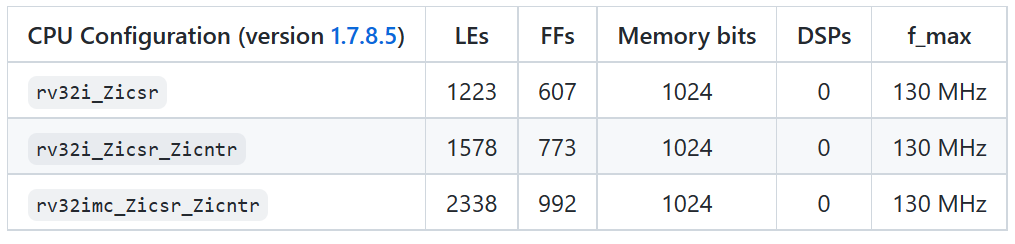

2)xc7a35ticsg324-1L,Xilinx Vivado 2019.2

3)Verilog Vs VHDL(EP4CE22F17C6,Quartus Prime 21.1.0)

Memories: 16kB IMEM (RAM), 8kB DMEM (RAM), 4kB internal bootloader ROM

CPU: rv32imc_Zicsr_Zicntr

Peripherals: UART0, GPIO, MTIME

4)NEO430

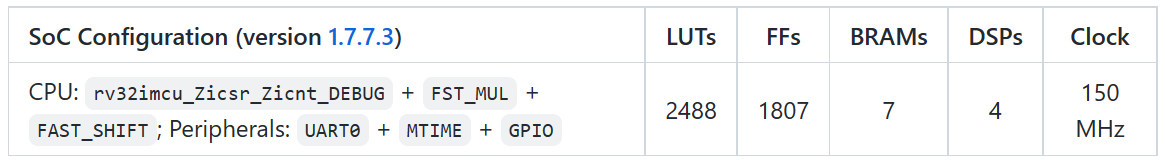

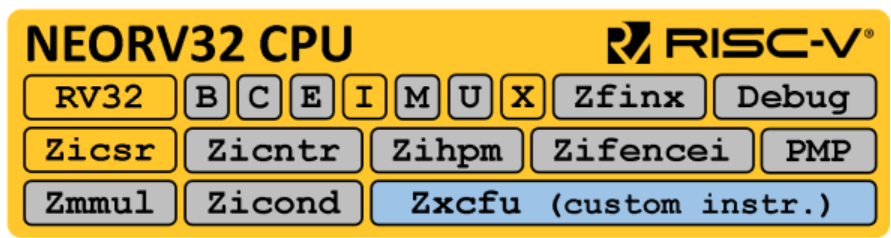

2.指令集(RV32I)

| CPU Instruction Sets and Extensions(CPU ISA扩展指令集) | |||

| CPU_EXTENSION_RISCV_B | boolean | false | Enable B ISA Extension (bit-manipulation). |

| CPU_EXTENSION_RISCV_C | boolean | false | Enable C ISA Extension (compressed instructions). |

| CPU_EXTENSION_RISCV_E | boolean | false | Enable E ISA Extension (reduced register file size). |

| CPU_EXTENSION_RISCV_M | boolean | false | Enable M ISA Extension (hardware-based integer multiplication and division). |

| CPU_EXTENSION_RISCV_U | boolean | false | Enable U ISA Extension (less-privileged user mode). |

| CPU_EXTENSION_RISCV_Zfinx | boolean | false | Enable Zfinx ISA Extension (single-precision floating-point unit). |

| CPU_EXTENSION_RISCV_Zicsr | boolean | true | Enable Zicsr ISA Extension (control and status register access). |

| CPU_EXTENSION_RISCV_Zicntr | boolean | true | Enable Zicntr ISA Extension (CPU base counters). |

| CPU_EXTENSION_RISCV_Zicond | boolean | false | Enable Zicond ISA Extension (conditional operations). |

| CPU_EXTENSION_RISCV_Zihpm | boolean | false | Enable Zihpm ISA Extension (hardware performance monitors). |

| CPU_EXTENSION_RISCV_Zifencei | boolean | false | Enable Zifencei ISA Extension (instruction stream synchronization). |

| CPU_EXTENSION_RISCV_Zmmul | boolean | false | Enable Zmmul - ISA Extension (hardware-based integer multiplication). |

| CPU_EXTENSION_RISCV_Zxcfu | boolean | false | Enable NEORV32-specific Zxcfu ISA Extension (custom RISC-V instructions). |

3.架构

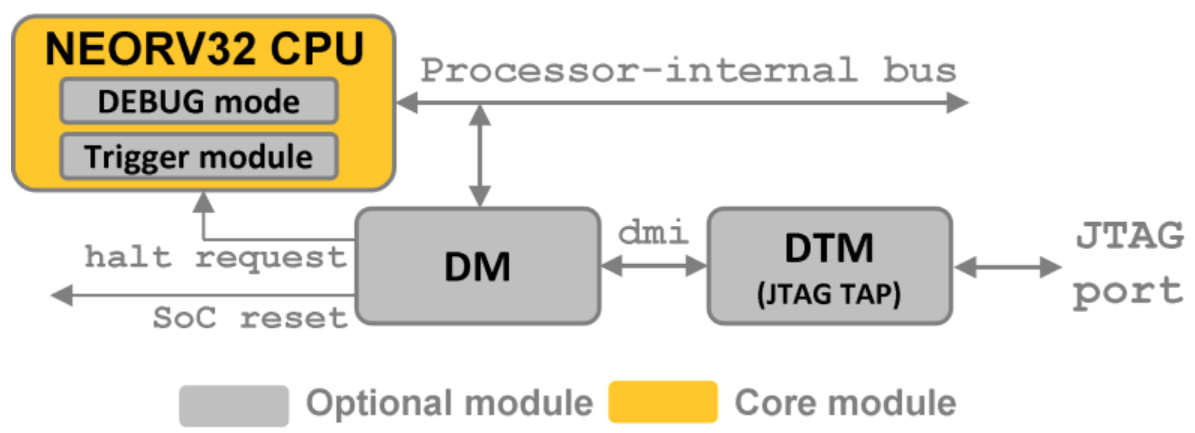

4.OpenOCD(Debug)

CPU Debug模式需要Zicsr和Zifencei指令扩展。

5.BootLoader

UART0:19200-8-N-1

When you reset the NEORV32 processor, the bootloader waits 8 seconds for a UART console input before it starts the automatic boot sequence. This sequence tries to fetch a valid boot image from the external SPI flash, connected to SPI chip select spi_csn_o(0). If a valid boot image is found that can be successfully transferred into the instruction memory, it is automatically started. If no SPI flash is detected or if there is no valid boot image found, and error code will be shown.

即:8秒等待串口,否则正常启动,找SPI Flash。

6.工具链(已打包)