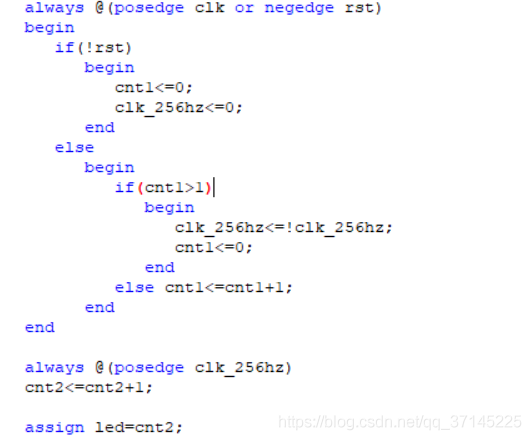

注:上面这段代码中的clk_256hz是想产生25MHz的信号(clk是50MHz)。信号命名需要规范才好呵,否则很容易误导。

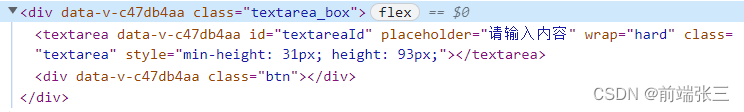

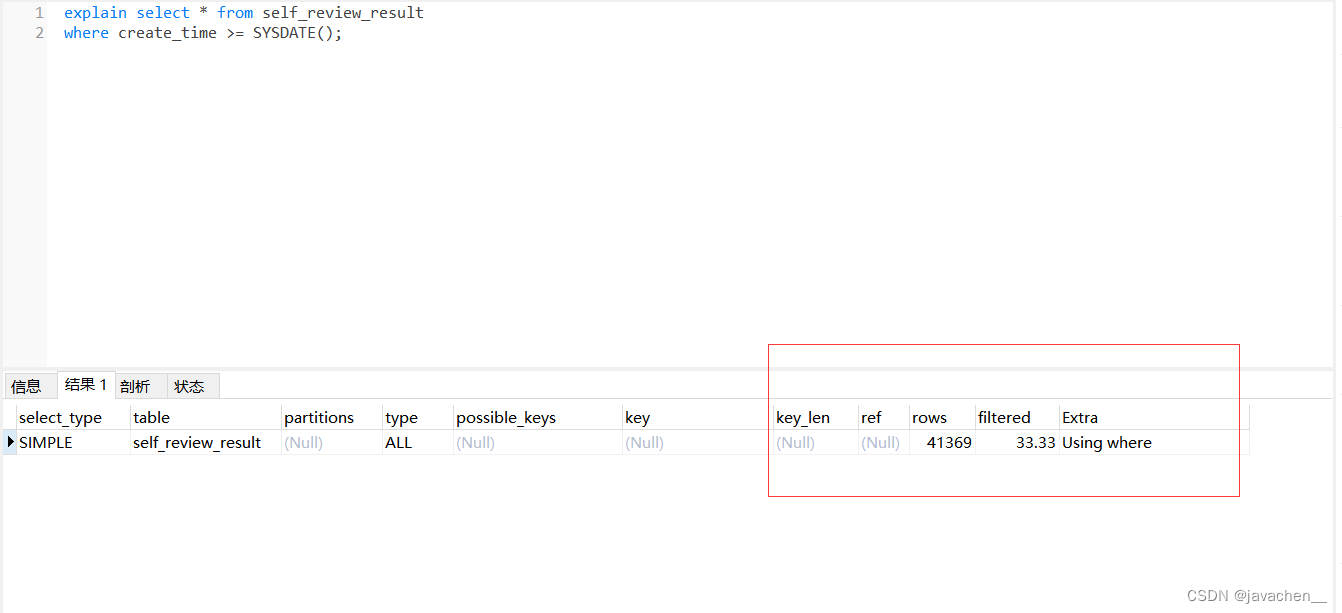

在做实验三时,想通过上图所示的程序代码将50mhz(clk)的时钟分频得到为25mhz(clk_256)的时钟。初以为,它们的分频系数为2,计数值为1,所以写的判断语句为cnt1>1,错误的以为便可以得到25mhz的时钟,但是仿真的结果如下图所示,利用光标测出clk_256一个周期为120000ps,频率为8.3mhz,出现了很大的偏差。

为什么?

他细想想,才发现是6分频波形而不是2分频波形,原因是因为cnt1的值如图2所示为0,1,2,所以clk_256要经过3个上升沿,才会翻转一次,所以是6分频,得到频率为8.3mhz的clk_256。如果将判断语句改为cnt1<1时,cnt1的值只有0,clk_256只会翻转一次,才会得到25mhz的时钟。