目的

为了更好的分析hardfault问题、代码卡在某个地方但是又不方便仿真,需要理解m3、m4的栈是怎样的,更快的定位问题。

预备知识

内核有如下寄存器:

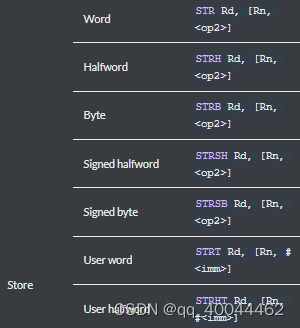

R0~R12,SP(R13),LR(R14),PC(R15),xPSR,在进入异常时内核会自动保存R0 ~ R3,R12,LR,PC,xPSR,对于m4,如果在进入异常前使用了浮点计算还会保存S0 ~ S15,FPSCR寄存器,栈帧如下

SP(R13):

cortex有2个栈指针,复位后默认使用msp主栈指针,中断中使用的是msp;psp线程栈,rtos中各个任务中就是使用psp。

LR(R14):

做分支时,用于保存返回地址;进入异常时用于区分当前使用的msp还是psp

如上LR的bit2=1则使用psp,bit2=0使用msp

并且对于m4,bit4=0则使用了fpu,bit4=1则没有使用fpu

PC(R15):将要执行指令的地址,PC的LSB总是0,但是向PC写值时必须保证LSB=1,用以表明这是在Thumb状态下执行,如果写了0,则企图转入ARM模式,将产生fault异常

栈例子

函数调用过程中的栈

如下例子是在freertos环境,代码如下

int f3(int a,int b)

{a += (a+b);b += (a-b);return a+b;

}int f2(int a,int b)

{int c = f3(a,b);c++;if(c>0)printf("%d\n",c);return c;

}

void f1()

{int c=0;c = f2(1,2);c++;if(c>0)printf("%d\n",c);

}

static void AppTaskStart (void *p_arg)

{

// fault_test_by_unalign();f1();while (1) {LED_RUN_ON;vTaskDelay(500/portTICK_RATE_MS);LED_RUN_OFF;vTaskDelay(500/portTICK_RATE_MS);}

}

在f3第一句打断点,可以看到

1.pc是将要执行的指令,此时还未执行

2.函数调用关系f1–>f2–>f3,所以返回的顺序是f3–>f2–>f1

从f3返回f2

f3返回f2用LR寄存器值写入PC,所以实际返回地址=LR的值-1

f2返回f1就要用之前保存再栈里的值

中断过程中的栈

现在向f3中加入如下函数,将产生hardfault

void fault_test_by_div0(void) {volatile int * SCB_CCR = (volatile int *) 0xE000ED14; // SCB->CCRint x, y, z;*SCB_CCR |= (1 << 4); /* bit4: DIV_0_TRP. */x = 10;y = 0;z = x / y;printf("z:%d\n", z);

}

int f3(int a,int b)

{a += (a+b);fault_test_by_div0();b += (a-b);return a+b;

}

LR的bit2=1,则使用的是psp栈,往前回溯得到pc=0x08001FE2,正是产生hardfault的代码,

pc旁边的LR=0x08001CF3则是要返回的上一及函数

再分析栈中数据,要是奇数且在代码地址范围内

如上一步一步倒推则把调用关系理清了

栈回溯代码

作者Armink就是把上述过程代码化,并增加一些寄存器的错误位解释,源码如下

https://github.com/armink/CmBacktrace

关键代码

作者为了判断PC的准确性还判断PC的上一条指令是不是BL或者BLX,关键代码如下

/* copy called function address */for (; sp < stack_start_addr + stack_size; sp += sizeof(size_t)) {/* the *sp value may be LR, so need decrease a word to PC */pc = *((uint32_t *) sp) - sizeof(size_t);/* the Cortex-M using thumb instruction, so the pc must be an odd number */if (pc % 2 == 0) {continue;}/* fix the PC address in thumb mode */pc = *((uint32_t *) sp) - 1;if ((pc >= code_start_addr + sizeof(size_t)) && (pc <= code_start_addr + code_size) && (depth < CMB_CALL_STACK_MAX_DEPTH)/* check the the instruction before PC address is 'BL' or 'BLX' */&& disassembly_ins_is_bl_blx(pc - sizeof(size_t)) && (depth < size)) {/* the second depth function may be already saved, so need ignore repeat */if ((depth == 2) && regs_saved_lr_is_valid && (pc == buffer[1])) {continue;}buffer[depth++] = pc;}}

/* check the disassembly instruction is 'BL' or 'BLX' */

static bool disassembly_ins_is_bl_blx(uint32_t addr) {uint16_t ins1 = *((uint16_t *)addr);uint16_t ins2 = *((uint16_t *)(addr + 2));#define BL_INS_MASK 0xF800

#define BL_INS_HIGH 0xF800

#define BL_INS_LOW 0xF000

#define BLX_INX_MASK 0xFF00

#define BLX_INX 0x4700if ((ins2 & BL_INS_MASK) == BL_INS_HIGH && (ins1 & BL_INS_MASK) == BL_INS_LOW) {return true;} else if ((ins2 & BLX_INX_MASK) == BLX_INX) {return true;} else {return false;}

}

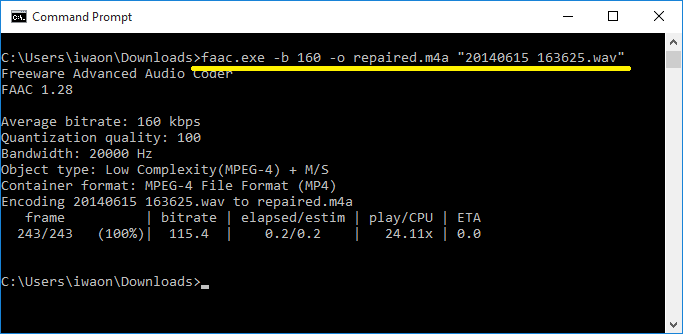

以0x0800035D为例子,减去1就是0x0800035C,再减去4就是0x08000358,而

0x08000358地址的内容是0xF001FC9E,符合第一个if条件,就认为这是一个有效的代码地址

fpu

还有对于有fpu的,如果LR的bit4=0则表明还把S0~S15、FPSCR也压入栈了,分析是要退出来

static uint32_t statck_del_fpu_regs(uint32_t fault_handler_lr, uint32_t sp) {statck_has_fpu_regs = (fault_handler_lr & (1UL << 4)) == 0 ? true : false;/* the stack has S0~S15 and FPSCR registers when statck_has_fpu_regs is true, double word align */return statck_has_fpu_regs == true ? sp + sizeof(size_t) * 18 : sp;

}